ственно с первьм и вторым входами I рого буферных регистров и управляэадания параметров шкалы преобразова- ющим входом второго мультиплексора, теля, выход сумматора соединен с ин- выход которого соединен с вторым информационными входами первого и вто- формационным входом сумматора.

1057953

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для контроля последовательности байтов данных дисковой памяти | 1985 |

|

SU1315979A1 |

| НАКОПИТЕЛЬ ИМПУЛЬСНЫХ СИГНАЛОВ | 1991 |

|

RU2089043C1 |

| Устройство для обучения | 1988 |

|

SU1663618A1 |

| Микропрограммный процессор | 1985 |

|

SU1275457A1 |

| Устройство для сопряжения ЦВМ с группой абонентов | 1988 |

|

SU1559349A1 |

| Процессор | 1984 |

|

SU1247884A1 |

| Устройство для сопряжения вычислительной машины с устройством ввода изображения | 1985 |

|

SU1260967A1 |

| Устройство для ввода информации | 1989 |

|

SU1695314A1 |

| Процессор с микропрограммным управлением | 1983 |

|

SU1149273A1 |

| Устройство для сопряжения ЭВМ с объектами управления | 1986 |

|

SU1401469A1 |

Щ1ФРОВОЙ НЕЛИНЕЙНЫЙ МАСШТАБИРУЮЩИЙ ПРЕОБРАЗОВАТЕЛЬ, содержащий блок управлеш1Я, блок деления на два, группу элементов И, сумматор и сдвиговый регистр, выход которого соеди.нен с первыми входами элементов И группы, вторые входат и выходы которых соедипены соответственно с выходом блока деления на два и первым информационным входом сумматора, от л ич а ю щ и йен тем, что, с целью расширения области применения путем преобразоиания произвольных нелинейных зависимостей , в него введены два буферных регистра, два мультиплексора и блок памяти, причем блок управления содержит два элемента И, два триггера, два счетчика, дешифратор и генератор импульсов, выход которого соединен с первым вхо дом первого элемента И, выход которого соединен с входом первого счетчика, выход переполнения которого соединен со счетным входом второго счетчика и первыми входами второго элемента И и первого триггера, второй вход и выход которого соединены соответственно с первым выхо дом и первым входом дешифратора, второй вход которого соединен с разрядным выходом первого счетчика, выход второго элемента И соединен с первым входом второго триггера, выход которого соединен с вторым входом первого элемента И, вход задания шкалы блока управления соединен с установочным входом второго счетчика и вторым входом второго триггера, второй вход второго элемента И блока управления соединен с выходом знака первого буферного регистра, выходы с первого по четвертый дешифратор блока управления соединены I соответственно с входом приема кода первого буферного регистра, входом (П 1;риама кода сдвигового регистра, входом приема кода второго буферного с регистра, и управляющими входами блока деления :ia два и сдвигового регистра, выход первого триггера блока управления соединен с управляющими входами первого мультиплексора и сд сумматора и входом младшего разряда si адреса блока памяти, вход старших со ел разрядов которого соединен с выходом второго счетчика блока управпе1ШЯ, выход блока памяти соединен с 00 первым информационным входом второго мультиплексора и входом блока деления иа два, выход и второй информационный вход второго мультиплексора соединены соответственно с входом сдвигового регистра, вторым входом сумматора и выходом первого мультиплексора, первый и второй информационные входы которого соединены соответственно с выходами первого и второго буферных регистров, установочные входал которых соединены соответ

Изобретение относится к устройствам для обработки хщфровых данных.

Известен хщфровой преобразователь, содержащий элементы И и ИЛИ, сумматор, дшшфраторы, шифраторы, сдвиго- 5 вые регнстры и триггер С i 3«

Недостатком известного преобразователя является сложность.

Наиболее близким к предлагаемому по техш1ческ й сущности является преобразователь, содержащий cyi iaTOp зквивалентьв и группу схем И, входы которых соединены С выходами блока деления на.два И1 ормационш 1е входа которого соедаыены с группой вход- 5 iSitx вшн а выкоды соединены с входами сумматору эквивалентов, управляюпще входы сзгем И соединены с выходами даойчного регистра сдвига, информационные nxofifd которого соеди- 20 нё1Ш с другой группой входных вщн, а управляющий вход соеяинен-с вы ходом блока управпекшя, другой выход которого подкшочбЯ к управляющему входу блока деле1шй на два 2. 25

Известный преобразователь может быть использован только в информационно-измерительных системах, рабс таю1щх с датчиками , характеристики которых 1Шяе&1ал, В то же время 30 в i1po в вIШeшIOcти используют значительное количество типов датчиков С ч-щнейньши хаоактерисч кшш, напри1 мер датчики тe шepatyplI, датчики давления и ф. При работе информа- 35 ционно-измерительных систеам с такого рода датчиками необходимо выполнить фуикодо нальное преобразование, т.е. операцию линеаризации. Для реализад ш .линеаризации могут быть ис- 40 пользованы либо цифровое вычислительное устройство, ;шбо специализированные аналоговые приборы.

Цель изобретения - расширение области применения преобразователя пу- 5 тем преобразования произвольных нелинейных зависимостей.

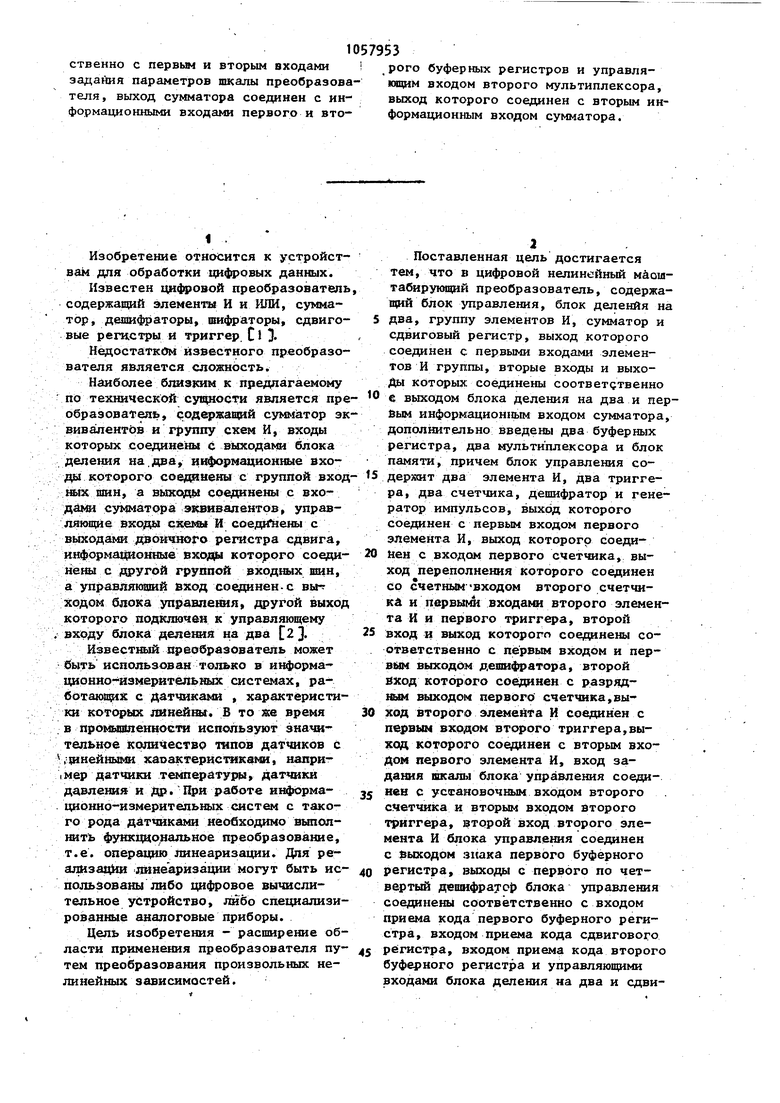

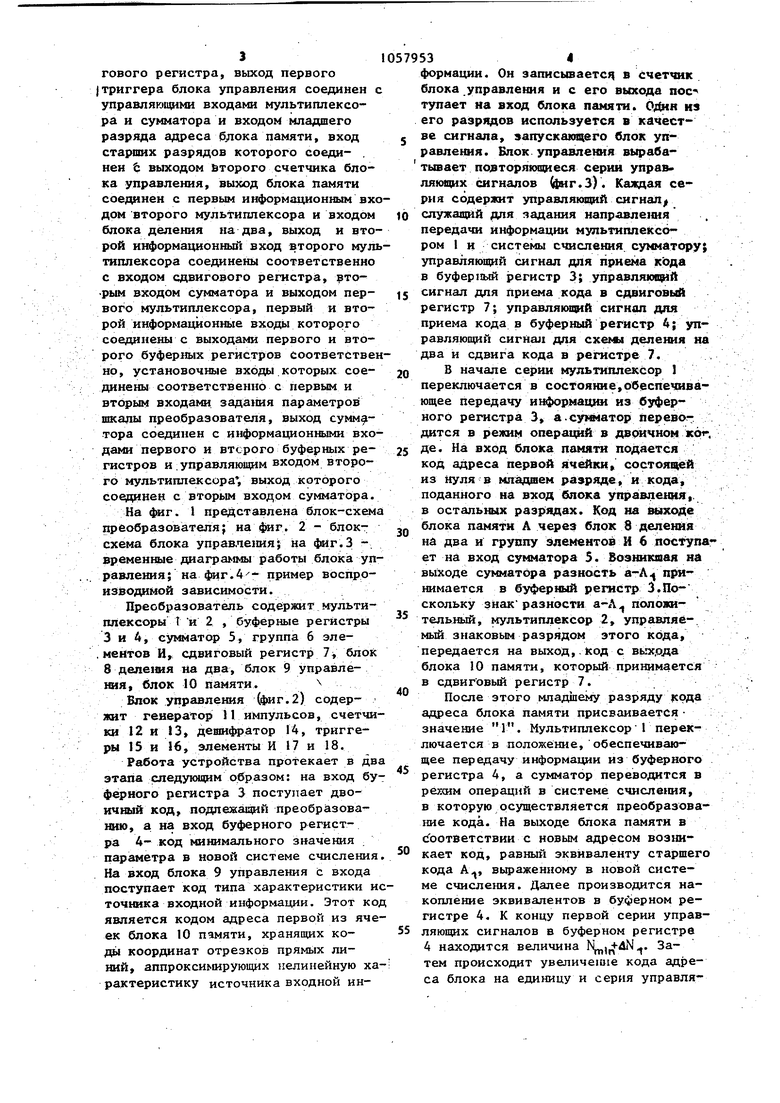

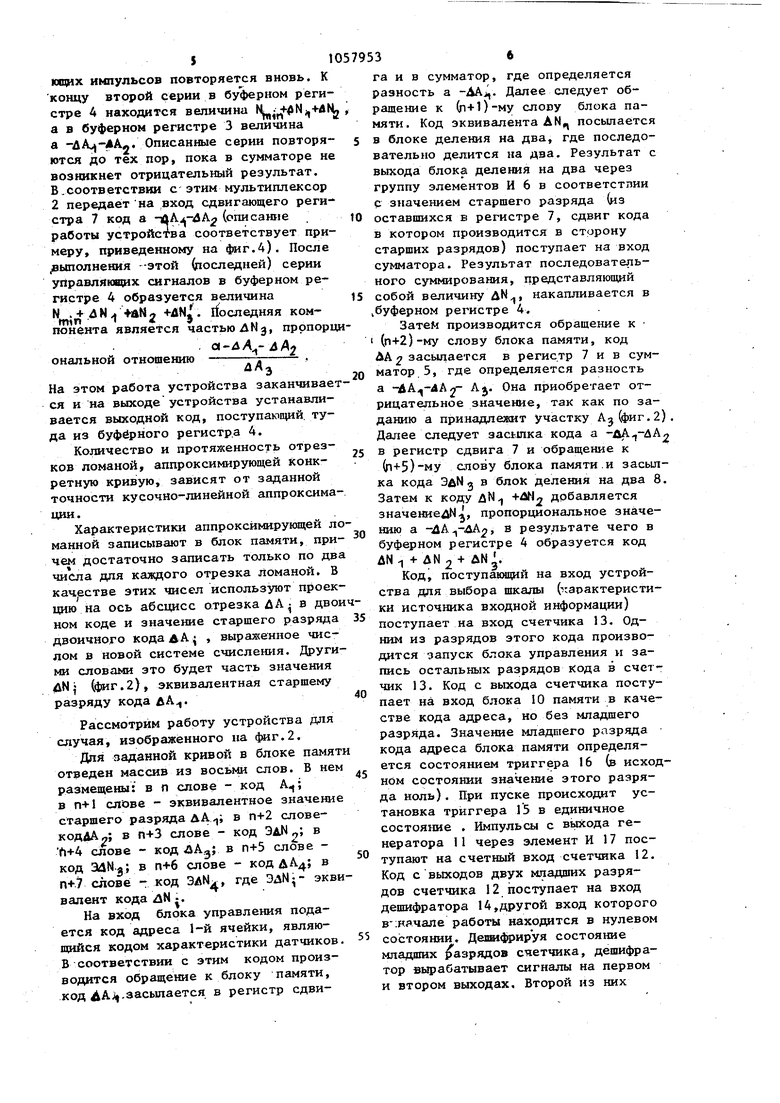

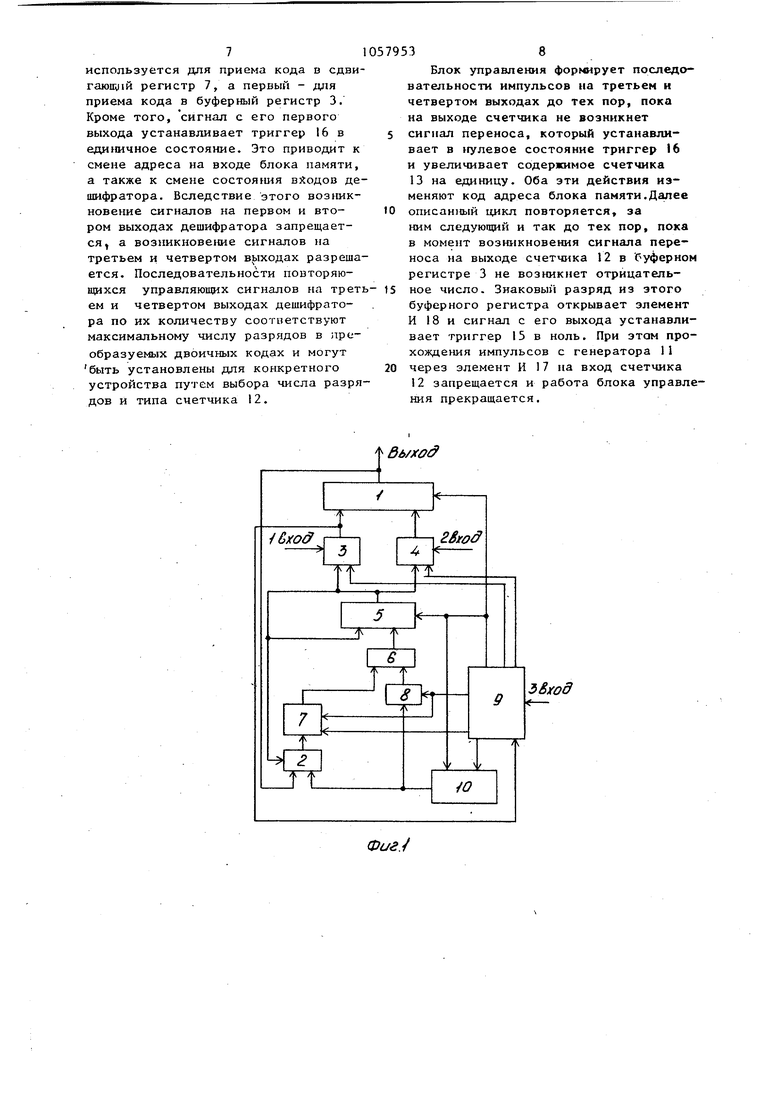

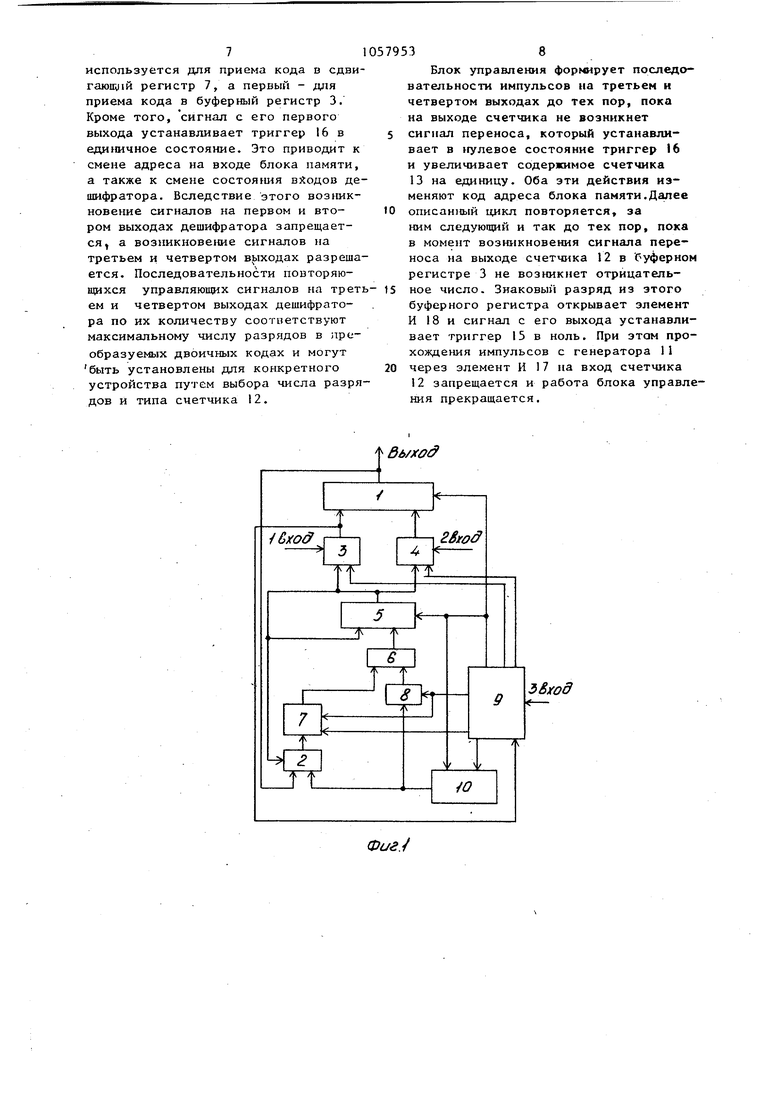

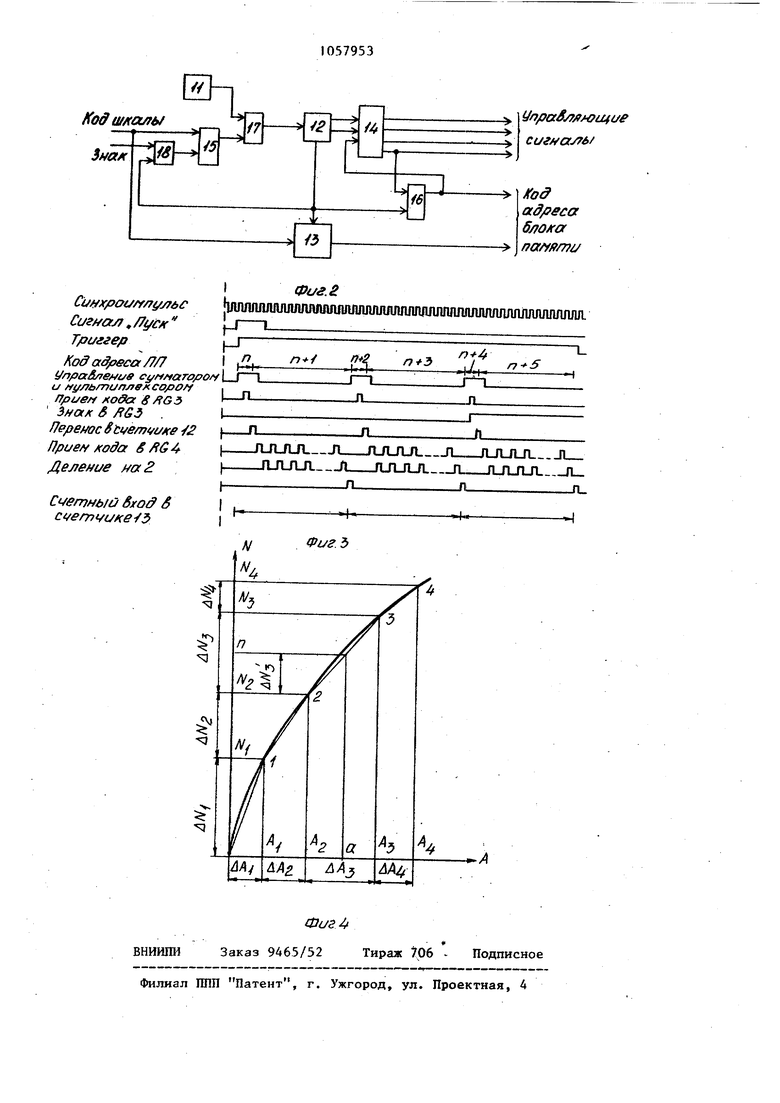

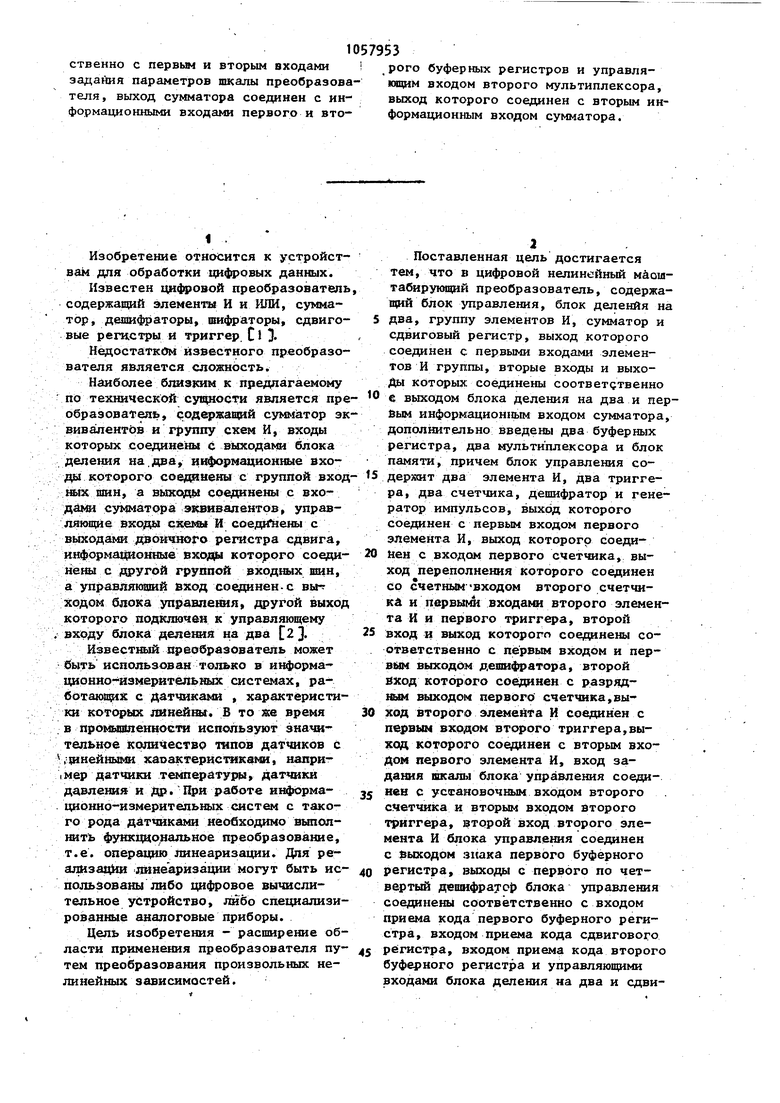

Поставх{енная цель достигается тем, что в цифровой нелинейный маоитабирующий преобразователь, содержащий блок 1Т1равления, блок деления н два, группу элементов И, сумматор и сдвиговый регистр, выход которого соединен с первыми входами элементов И группы, вторые входы и выходы которых; соединены соответственно е выходом блока деления на два и певым информацион шм входом сумматора дополнительно введены два буферных регистра, два мультиплексора и блок памяти, причем блок управления содержит два элемента И, два триггера, два счетчика, дешифратор и генератор импульсов, выход которого соединен с первым входом первого злемента И, выход которого соединен с входом первого счетчика, выход переполнения которого соединен со счетным входст второго счетчикд. и первыгш входами второго элемента И и первого триггера, второй вход и выход которого соединены соответственно с первым входом и первым выходом дешифратора, второй вход которого соединен с разрядным выходом первого счетчика,выход второго элемента И соединен с первым входом второго триггера,выход которого соеданеи с вторым входом первого элемента И, вход задания шкалы блока управления соединен с усгановочШ) входом второго счетчика и вторым входом второго триггера, второй вход второго элемента И блока управления соединен с выходом зкака первого буферного регистра, выходы с первого по четвертый де1шфра7о1; блока управления соединены соответственно с входом приема кода первого буферного регистра, входом приема кода сдвигового решстра, входом приема кода второго буферного регистра и управляющими входами блока деления на два и сдвигового регистра, выход первого Jтриггера блока управления соединен управляющими входами мультиплексора и сумматора и входом младшего разряда адреса 0/1ока памяти, вход старших разрядов которого соеди- . ней & выходом Ьторого счетчика блока управления, выход блока памяти соединен с первым информационным вх дом второго мультиплексора и входом блока деления на два, выход и вто рой информационный вход второго мул шплексора соединены соответственно с входом сдвигового регистра, вторым входом сумматора и выходом первого мультиплексора, первый и второй информационные входы которого соединены с выходами первого и второго буферных регистров соответстве но, установочные входы которых соединены соответственно с первым и вторым входами задагшя параметров шкалы преобразователя, выход сумматора соединен с информационными вхо дами первого и второго буферных регистров и управляющим входом второго мультиплексора, выход которого соединен с вторым входом сумматора. На фиг. I представлена блок-схем преобразователя; на фиг. 2 - блоксхема блока управления; на фиг.З -. временные диаграммы работы блока уп . равления; на фиг. пример воспроизводимой зависимости. Преобразователь содержит мультиплексоры Т и 2 , буферные регистры 3 и 4, су1Ф1атор 5, группа 6 эле. ментов И сдвиговый регистр 7у блок 8 деления на два, блок 9 управления, блок 10 памяти. Блок управления (фиг.2) содеряит генератор 11 импульсов, счетчи ки 12 к 13, деши( 14, триггеры 15 и 16, элементы И 17 и 18. Работа устройства протекает в дв этапа следующим образом: на вход бу ферного регистра 3 поступает двоичный код, подлежавший преобразоваМйю, а на вход буферного регистра 4- код минимального значения , параметра в новой системе счисления На вход блока 9 управления с входа поступает код типа характеристики и точника входной информации. Этот ко является кодом адреса первой из яче ек блока 10 памяти, хранящих кода координат отрезков прямь1х линий, аппроксимирующих нелинейную ха рактеристику источника входной нн534формации. Он записываете) в счетчик блока управления и с его выходца пос- тупает на вход блока памяти. из его разрядов используется в качестве сигнала, запускающего блок управления. Блок управления вырабатывает позторякщиеся серии управ лякяцих сигналов г.З). Каждая серия содержит управлякпций сигнал служащий для задания направле1шя , передачи информации мультиплексором I и системы счисления, сумматору; управляющий сигнал для приема в буферный регистр 3; управляювр й сигнал для Приема кода в сдвиговый регистр 7; управляк ф1й сигнал для приема кода в буферный регистр 4; управляющий сигнал для схемы депеиия на два и сдвига кода в регистре 7. В начале серии мультиплексор 1 переключается в состояние,обеспечивающее передачу информации из буферного регистра 3, а.сумматор перево-дится в режим операций в двоичном крп де. На вход блока памяти подается код адреса первой ячейки состоящей из йуля в младшем разряде, и кода, поданного иа вход блока управления,. в остальных разрядах. Код на выходе блока памяти А через блок 8 деления на два и группу элементов И 6 поступает на вход сумматора 5. Возникшая на выходе сумматора разность а-Л принимается в буферный регистр 3.Поскольку знак разности а-А положительный, мультиплексор 2, управляв-, мый знаковым разрядом этого кода, передается на выход,.код с выхрда блока 10 памяти, который принимается в сдвиговый регистр 7. После зтого младшему разряду |сода адреса блока памяти присваиваетсязначение 1. Мультиплексор 1 переключается в положение,обеспечивающее передачу информации из буферного регистра 4, а сумматор переводится в рехсим операций в системе счисления, в которую осуществляется преобразование кода. На выходе блока памяти в «Соответствии с новым адресом воз1Шкает код, равный эквиваленту старшего кода А, выраженному в новой системе счиспе шя. Далее производится накопление эквивалентов в буферном регистре 4. К концу первой серии управляющих сигналов в буферном регистре 4 находится величина N,|+4N. Затем происходит увеличешш кода адреса блока на еди1шцу и серия управля5Ю1Щ1Х импульсов повторяется вновь. К концу второй серии в буферном регистре Д находится величина Nj, а в буферном регистре 3 величина а . Описанные серии повторя ются до тех пор, пока в сумматоре не возникнет отрицательный результат. В.соответствии с этим мультиплексор 2 передаетна вход сдвигающего регистра 7 код а (описание работы устройства соответствует примеру, приведенному на фиг.4). После ьтолнения -этой последней) серии управляющих сигналов в буферном регистре 4 образуется величина N . +4N,j MNj ANj. Йоследняя компонента является частью ANj, пррпорц а-АА. ональной отношению --т - . ЛАа На этом работа устройства заканчивае ся и на выходе устройства устанавливается выходной код, поступающий, туда из буферного регистра 4. Количество и протяженность отрезков ломаной, аппроксимирующей конкретную кривую, зависят от заданной точности кусочно-линейной аппроксима ции. Характеристики аппроксимирующей л манной записывают в блок памяти, при чем достаточно записать только по дв числа для каждого отрезка ломаной. В качестве этих чисел используют проек цию на ось абсцисс отрезка йА- в дво ном коде и значение старшего разряда двоичного кода ДА , выраженное числом S новой системе счисления. Други ми словами зто будет часть значения uN (фиг.2), эквивалентная старшему разряду кода дА. Рассмотрим работу устройства для случая, изображённого на (jMr.2. Для заданной кривой в блоке памят отведен массив из восььш слов. В нем размещешл: в п слове - код А.,; в п+1 слове - эквивалентное значение старшего разряда в п+2 словекодДАл; в п+3 слове - код 3iii 2 h+4 слове - код ЛА.; в п+5 слове код , в п+6 слове - код дА4; в п+7 слове - код 3AN, где ЭДМ-- экви валент кода ЛН . На вход блока управления подается код адреса 1-й ячейки, являющийся кодом характеристики датчиков В соответствии с этим кодом производится обращение к блоку памяти, код АА .засылается в регистр сдви53га и в сумматор, где определяется разность а -АА,. Далее следует обращение к (п+1)-му слову блока памяти. Код эквивалента АN посылается в блоке деления на два, где последовательно делится на два. Результат с выхода блока деления на два через группу элементов И 6 в соответствии С значением старшего разряда (из оставшихся в регистре 7, сдвиг кода в котором производится в сторону старших разрядов) поступает на вход сумматора. Результат последовательного суммирования, представляющий собой величину ДК, накапливается в Iбуферном регистре 4. Затей производится обращение к (п+2)-му слову блока памяти, код ДА 2 засылается в регистр 7 и в сумматор 5, где определяется разность а -йА -ДАл- AJ. Она приобретает отрицательное значение, так как по заданию а принадлежит участку А (фиг. 2) . Далее следует засьтка кода а в регистр сдвига 7 и обращение к (п+5)му саову блока памяти,и засыпка кода ЭдЫд в блок деления на два 8. Затем к коду дМ Добавляется значениедМ, пропорциональное значе™ ° -ЛА.АА2, в результате чего в буферном регистре 4 образуется код AN-, + AN 2+ UN . Код, поступакиций на вход устройства для выбора шкалы (сарактеристики источника входной информации) поступает на вход счетчика J3. Одним из разрядов этого кода производится запуск блока управления и запись остальных разрядов кода в счетчик 13. Код с выхода счетчика поступает на вход блока 10 памяти в качестве кода адреса, но без младшего разряда. Значение младшего разряда кода адреса блока памяти определяется состоянием триггера 16 (в исходном состоянии значение этого разряда ноль). При пуске происходит установка триггера 15 в единичное состоя1ше . Импульоя с выхода генератора 1I через элемент И 17 поступают на счетный вход счетчика 12. Код с выходов двух младших разрядов счетчика 12 поступает на вход дешифратора 14,другой вход которого в:начале работы находится в нулевом состоянии. Дешифрируя состояние младших разрядов счетчика, дешифратор вырабатывает сигналы на первом и втором выходах. Второй из них используется для приема кода в сдв гающий регистр 7,3 первый - для приема кода в буферный регистр 3. Кроме того, сигнал с его первого выхода устанавливает триггер 16 в единичное состояние. Это приводит смене адреса на входе блока памяти а также к смене состояния взводов д шифратора. Вследствие этого возник новение сигналов на первом и втором выходах дешифратора запрещается, а возникновение сигналов на третьем и четвертом выходах разреш ется. Последовательности повторяющихся управляюгцих сигналов на тре ем и четвертом выходах дешифратора по их количеству соответствуют максимальному числу разрядов в пре образуемых двоичных кодах и могут быть установлены для конкретного устройства путем выбора числа разр дов и типа счетчика 12. 38 Блок управления формирует последовательности импульсов на третьем и четвертом выходах до тех пор, пока на выходе счетчика не возникнет сигнал переноса, который устанавливает в гулевое состояние триггер 16 и увеличивает содержимое счетчика 13 на единицу. Оба эти действия изменяют код адреса блока памяти.Далее описанный цикл повторяется, за JWM следующий и так до тех пор, пока в момент возникновения сигнала переноса на выходе счетчика 12 в буферном регистре 3 не возникнет отрицательное число. Знаковы разряд из этого буферного регистра открывает элемент И 18 и сигнал с его выхода устанавливает триггер 15 в ноль. При этом прохождения импульсов с генератора 11 через элемент И 17 на вход счетчика 12 запрещается и работа блока управления прекращается. ((/у7бс

yf}paS/ /t ou4iff CL/if a f

ffod

adflecat

f ff ff/77 / IФс/г.2 fmnnnflnmrnnnnimmiminjimumminnfuinnnmwmnnnJinnnimnjui

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Аналого-цифровые и цифроаналоговые нелинейные вычислительные устройства.Л., Энергия, 1974, с | |||

| Способ получения бензидиновых оснований | 1921 |

|

SU116A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Разборный с внутренней печью кипятильник | 1922 |

|

SU9A1 |

Авторы

Даты

1983-11-30—Публикация

1981-12-18—Подача