1

Изобретение относится к области вычислительной техники и может быть использовано при оценке качества случайных чисел.

Известны устройства для анализа вероятности характеристик датчика случайных чисел.

Одпо из известных устройств для анализа вероятности характеристик датчика случайных чисел содержит счетчики, дешифратор, блок сравиения, триггер, усилитель, блок задержки, вентплн, элемент ИП. Однако это устройство имеет невысокую точность I.

Другое из известных устройств для аналнза вероятностных характеристик датчика случайных чисел также содержит ечетчики, блок сравнеиия, блок задерлски, вентнли. Для повышения точности устройство, кроме того, содержит генератор импульсов, коммутатор, мультивибратор, элемент ИЛИ и днфферепцнруюш,ую день. Однако это устройство нмеет малый диапазои проверяемых случайных чнсел 2.

Наиболее близким техническим решением к данному изобретению является устройство для анализа вероятиоетиых характеристик датчика случайных чисел, содержаш,ее индикатор, первый вход которого подключен к выходу блока унравлепия, а второй вход - к выходу блока сравнения, первая группа входов которого соедииена с выходами коммутатора

соответствеино, первая группа входов которого является входами зстройства 3.

Недостатком этого устройства является низкое быстродействие.

Нелью изобретеиия является иовышение быстродействия.

Для достижения поставленргой цели устройство содерлсит первый и второй регистры памяти, входы которых соедииеиы с выходом блока управлепмя, а выходы - со вторыми груннамп входов коммутатора н блока сравнения соответственно.

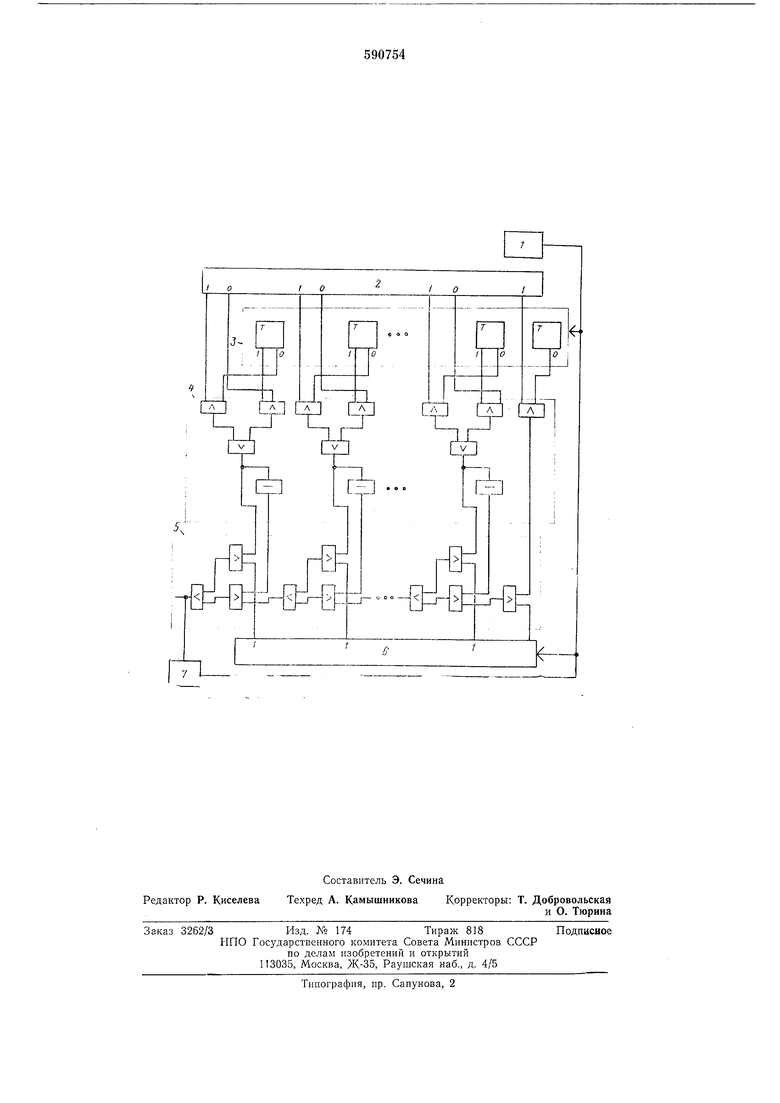

Блок-схема устройства приведена на чертеУстройство содержит блок управления I, датчик случайных чнсел ДСЧ 2, первый региетр памятн 3, выходы которого соединены со входами коммутатора 4, другие входы которого соединены с выходами датчика случайных чисел 2, а выходы - со входами блока сравиеипя 5, другие входы которого соединены с выходами второго регистра памяти 6, выход которого соединен со входом индикатора 7, другой вход которого соединен со входом второго регистра намятн 6нс выходом блока управления I.

Регистр памяти 3 представляет собой трпггерный регистр, служап ий для храпення двоичного числа. Коммутатор 4 является сумматором 110 модулю 2 с прямыми и инверсными выходами в каждом разряде. Коммутатор служит для выбора заданной группы (заданного сочетания) двоичных комбннаций (наборов), поступающих с выхода ДСЧ. При фиксироваппом числе наборов в грунне максимальное число неповторяющихся сочетаний равно, 2, где л - число разрядов ДСЧ. Эта величина определяется тем, что каждому числу, записанному в регистр 3, соответствует одно сочетание.

Блок сравнения 5 служит для пзменения чпсла комбинаций в группе. Число комбинаций в группе можно менять от О до 1.

Регистр памяти 6 служит для хранения заданного числа проверяемых комбннаций.

Индикатор 7 служит для фиксации вероятности появлеиня заданной группы комбинаций. В нростейщем случае он может состоять из двух счетчиков: счетчика общего числа обращений к ДСЧ и счетчика числа появлений заданной группы.

Работает устройство следующим образом.

В регистр памяти 3 записывается число, оиределяющее проверяемую группу комбинаций. В регистр 6 записывается число, задающее количество комбинаций в группе.

При подаче синхронизирующих импульсов с выхода датчика случайных чисел на коммутатор поступает случайная последовательность двоичных наборов (комбинаций). Коммутатор, суммируя эту носледовательность но модулю 2 с числом, записанным в регистре 3, образует новую последовательность двоичных наборов. Блок сравнения 5 из последовательности, ноступающей с выходов коммутатора, выбирает задапное чнсло комбинаций. Индикатор 7 определяет вероятность выпадания этой группы комбннаций. Качество случайности определяется по степени расхождения гипотетического и эмпирического распределений. Для этого, в частности, молсно использовать в качестве меры, характеризующей степень этого расхождения, критерий у.

Рассмотрим более подробно работу устройства на конкретном примере. Пусть датчик случайных чисел имеет три разряда. Тогда на его выходе всевозможные неповторяющиеся комбинации имеют внд:

000, 001, 010, 011, 100, 101, 110, 111.

Покажем как можно менять (задавать) число проверяемых комбпиаций. Число проверяемых комбинаций определяется двоичным набором, записанным в регистр 6. Для понимания работы блока сравнения предположим, что двоичные наборы с выхода датчика поступают непосредственно на блок сравнения.

Пусть число проверяемых комбинаций равно единице. Запишем двоичное представление этого числа - 001 в регистр 6. Тогда на выходе преобразователя (исходя из логики coej динеиия элементов преобразователя) высокий (единичпый) потенциал будет появляться

только при поступлепип на его вход набора 001.

Пусть число проверяемых комбинаций )ав110 двум. Запишем двоичное представление этого числа - 010 в регистр 6. Тогда на выходе преобразователя единичпый потеициал будет появляться лншь при поступлении на его вход двух наборов - 010 и 001. То есть схема блока сравнения такова, что

при записи в регистр 6 двоичного числа блок сравнения 5 «пропускает на свой выход число определенных наборов, равное числу, заиисаниому в регнстр 6. Рассмотрим как с помощью коммутатора

можно менять вид «пропускаемых наборов

прн их фиксированном числе, т. е. как молсно

«пропускать требуемое сочетание наборов с

выходов датчика через блок сравнения 5.

Обозначим наборы на выходе ДСЧ через

« «2 а наборы, записываемые в регистр 3 через pj fij . Тогда в связи с тем, что коммутатор является сумматором по модулю 2, каждому из восьми наборов «2 аз можно сопоставить на выходе коммутатора набор

а, ., Р.2 Рз.

двоичная заиись которого равна числу (,), ,

где знак (Т) означает суммирование по модулю 2.

Работу коммутатора можно пояснить таблицей соответствия.

Из таблицы видно, что фиксированному сочетанию наборов на выходе коммутатора со25 ответствуют различные сочетания наборов на

выходе датчика в зависимости от содержимого регистра 3. Наиример, пусть в регистре 6 иаходится число 011 (двоичиос представление десятичного числа 3). В этом случае преобразователь с выхода коммутатора будет «пропускать па свой выход только следующих три набора: 001, 010, 011. Тогда, если в регистр 3 запишем число 000, то наборы с выхода датчика иройдут на выход коммутатора без перекодировки п проверяемое сочетание будет иметь вид 001, 010, 011. Если же в регистр 6 заиишем число 111, то в этом случае иаборам 001, 010, 011, поступающим с выхода коммутатора соответствует (как это видно из таблицы) проверяемое сочетание вида 110, 101, 100.

Таким образом, если блок сравнения 5 «настроен на «иропуск онределенной группы наборов, то меняя содержимое регистра 3, можно проверить заданное чиело комбпиаций, иоявляющихея па выходе датч1 ка в разлнчпых сочетаниях.

Если датчик выдает случайную последовательность, идеально соответствующую равномерному распределеи;по, то вероятность появления группы наборов будет одна и та же для любого сочетания наборов в этсл группе. В том случае, когда случайные числа имеют корреляпиоиную связь, то для каждого сочетання вероятность будет различна.

Подсчнтывая общее число обращений к датчику (за фиксированное время) и число появлений задаииого сочетания наборов можно оценить качество случайной последовательности, в частпости по известной формуле

т

Р

3а,

N

где сг-среднее квадратичное отклоиешю, т - число иояьлеиий задаииого счетания

наборов, Л - общее число обращений к датчику.

Для более надежной оцеикн соответствия результата экспери.меита иредиолагаемому раснределенню можно нс11ол;:,зовуть критерий corjiaciiM 7.

В даином случае нз 2 возможных сочетаний необходнмо выбрать 8-10 такнх, которые отличаются друг от друга всеми наборамн. Число наборов в сочетаниях должно быть иримерно одинаково, причем суммарное число наборов во всех сочетаниях должио быть )авно 2. При соответствующей разрядности ДСЧ такой выбор всегда можно сделать иутем подбора определенных чисел в регистры 3 li 6.

Формула изобретен и я

Устройство для анализа вероятностных характеристик датчика случайных чисел, содержащее индикатор, иервый вход которого нодключен к выходу блока управлсння, а второй вход - к выходу блока сравнення, первая грунна входов которого соединена с выходами коммутатора соответетвеппо, первая группа входов которого является входами устройства, о т л и ч а ю щ е е е я тем, что, с целью иовышеиия быстродействия устройства, оно содержит иервый и второй регистры иамяти, р,ходы которых соединены с выходом блока управления, а выходы - с вторыми группами входов коммутатора и блока сравиепня соответственно.

Источники информации, принятые Ю внимание ири экспертизе

1.Авторское евидетельство СССР № 235398, кл. G 06F 11/00, 1967.

2.Авторское евндетельство СССР № 236851, кл. G 06F 1/02, 1967.

3.Авторское свидетельетво СССР Л 262497, кл. G 06F 11/00, 1968.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для вероятностного моделирования | 1973 |

|

SU488212A1 |

| СУММИРУЮЩЕЕ УСТРОЙСТВО ПО МОДУЛЮ | 1993 |

|

RU2034328C1 |

| N-СВЯЗНЫЙ МАРКОВСКИЙ ГЕНЕРАТОР ПСЕВДОСЛУЧАЙНОЙ ДВОИЧНОЙ ПОСЛЕДОВАТЕЛЬНОСТИ | 2024 |

|

RU2841349C1 |

| Устройство для преобразования по функциям Уолша | 1983 |

|

SU1129619A2 |

| Комбинаторное устройство | 1978 |

|

SU798807A1 |

| ГЕНЕРАТОР СЛУЧАЙНЫХ ЧИСЕЛ | 2001 |

|

RU2211481C2 |

| Датчик случайных чисел | 1983 |

|

SU1200285A1 |

| ПРОЦЕССОР ПОВЫШЕННОЙ ДОСТОВЕРНОСТИ ФУНКЦИОНИРОВАНИЯ | 2018 |

|

RU2708956C2 |

| Устройство для анализа вероятностныхХАРАКТЕРиСТиК дАТчиКА СлучАйНыХчиСЕл | 1979 |

|

SU822198A2 |

| Устройство для моделирования динамических процессов | 1990 |

|

SU1817107A1 |

Авторы

Даты

1978-01-30—Публикация

1976-02-05—Подача