(54) УСТРОЙСТВО ДЛЯ ФОРМИРОВАНИЯ

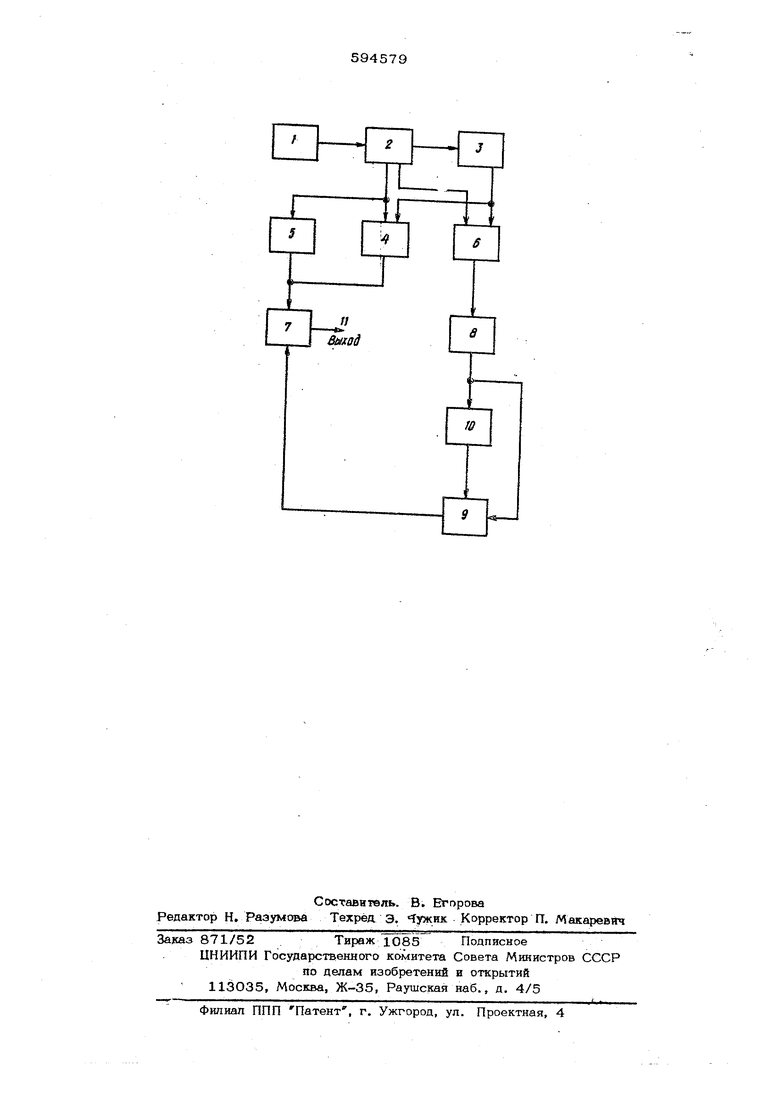

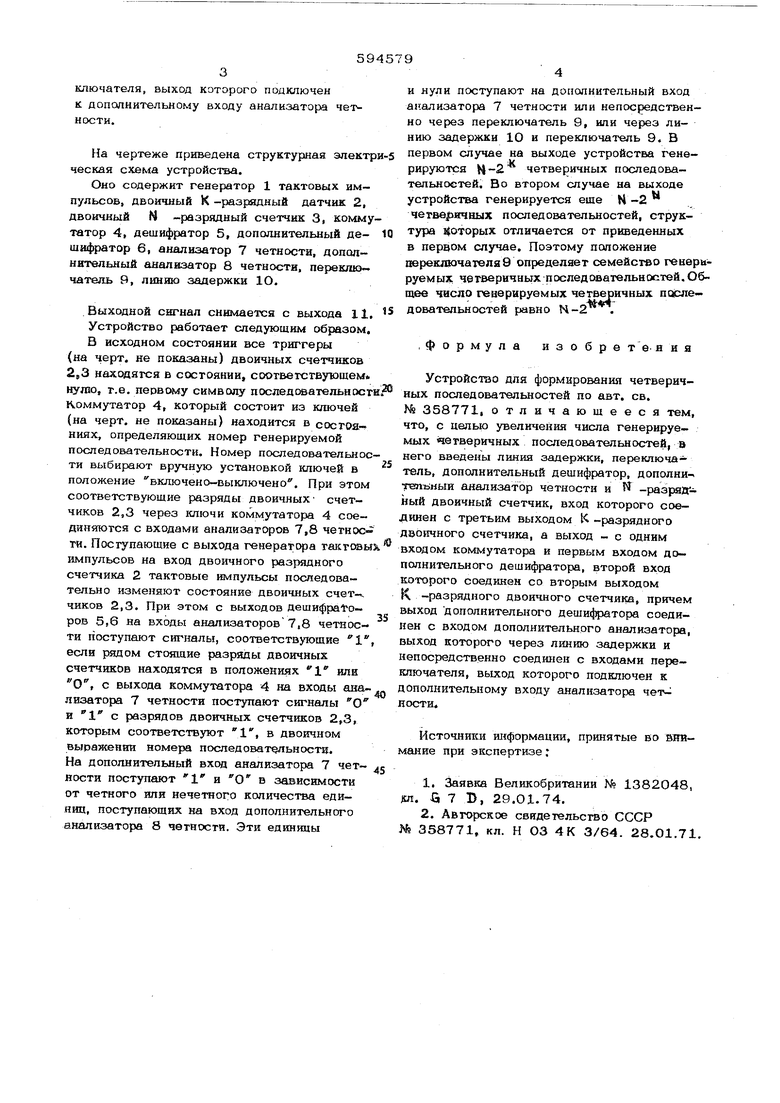

ЧЕТВЕРТИЧНЫХ ПОСЛЕДОВАТЕЛЬНОСТЕЙ ключателя, выход которого подключен к дополнительному входу анализатора четности. На чертеже приведена структурная элект ческая схема устройства. Оно содержит генератор 1 тактовых импульсов, двоичный К -разрядный датчик 2, двоичный N -разрядный счетчик 3, комм татор 4, дешифратор 5, дополнительный дашифратор 6, анализатор 7 четности, дополнительный анализатор 8 четности, переклю чатель 9, линшо задержки 1О. Выходной сигнал снимается с выхода 11 Устройство работает следующим образом В исходном состоянии все триггеры (на черт, не показаны) двоичных счетчиков 2,3 находягся в состоянии, соотвегсгвуюшем нугао, т.е. первому символу последсжательнос Коммутатор 4, который состоит из ключей (на черт, не показаны) находится 0 сосгоаниях, определяющих номер генерируемой последовательности. Номер последовательно ти выбирают вручную установкой ключей в положение включено-выключено. При этом соответствующие разряды двоичных счетчиков 2,3 через ключи коммутатора 4 соединяются с входами анализаторов 7,8 чегнос ти. Поступающие с выхода генератора тактовы импульсов на вход двоичного разрядного счетчика 2 тактовые импульсы последовательно изменяют состояние двоичных счетчиков 2,3. При этом с выходов ДешифраТо ров 5,6 на входы анализаторов 7,8 четности поступают сигналы, соответствующие 1 если рядом стоящие разрвды двоичных счетчиков находятся в положениях 1 или О, с выхода коммутатора 4 на входы еаш лизатора 7 четности поступают сигналы О и 1 с разрядов двоичных счетчиков 2,3, которым соответствуют 1, в двоичном выражении номера послед ости. На дополнительный вход анализатора 7 четности поступают I и О в зависимсюти от четного или нечетного количества единиц, поступающих на вход дополнительного анализатора 8 четности. Эти единицы и нули поступают на дополнительный вход анализатора 7 четности или непосредственно через переключатель 9, или через линию задержки 10 и переключатель 9. В первом случае на выходе устройства генерируютса Ц-2 четверичных последовательнсхзтей. Во втором случае на выходе устройства генерируется еще Ы -2 четверичных последовательностей, структура 1 оторых отличается от приведенных в первом случае. Поэтому положение переключателя 9 определяет семейство генерируемых четверичньгх последовательностей. Общее число генерируемых четверичных псюледовательностей равно N-2 . ,формула изобре те я и я Устройство для формирования четверичных последовательностей по авт. св. № 358771, отличающееся тем, что, с целью увеличения числа генерируемых четверичных последовательностей, в него введены линия задержки, переключатель, дополнительный дешифратор, дополни тгшпэлыи анализатор четности и N -разрад ный двоичный счетчик, вход которого соеинен с третьим выходом К -разрядного двоичного счетчика, а выход - с одним входом коммутатора и первым входом дополнительного дешифратора, второй вход которого соединен со вторым выходом К -разрядного двоичного счетчика, причем выход дополнительного дешифратора соединен с входом дополнительного анализатора, выход которого через линию задержки и непосредственно соединен с входами переключателя, выход которого подключен к дополнительному входу анализатора чет ности. Йсточншси шсформации, принятые во внвмгшие при экспертизе . 1.Заявка Великобритании № 1382048, ;ш. а 7 D, 29.01.74. 2.Авгорское свигдетельство СССР J 358771, кл. Н ОЗ 4К 3/64. 28.О1.71,

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для формирования ортогональных последовательностей | 1977 |

|

SU661733A1 |

| УСТРОЙСТВО для ФОРМИРОВАНИЯ ЧЕТВЕРИЧНЫХ ПОСЛЕДОВАТЕЛЬНОСТЕЙ | 1972 |

|

SU358771A1 |

| Устройство для формирования четвертичных последовательностей | 1974 |

|

SU528692A1 |

| Устройство для формирования сложныхСигНАлОВ | 1979 |

|

SU817994A1 |

| Логический анализатор | 1986 |

|

SU1432527A1 |

| Устройство для выделения импульсов синхронизации | 1978 |

|

SU785977A1 |

| РАДИОЛИНИЯ С ПСЕВДОСЛУЧАЙНОЙ ПЕРЕСТРОЙКОЙ РАБОЧЕЙ ЧАСТОТЫ | 2009 |

|

RU2411663C1 |

| УСТРОЙСТВО ДЛЯ ФОРЛ1ИРОВАНИЯ ЧЕТВЕРИЧНО- КОДИРОВАННЫХ ПОСЛЕДОВАТЕЛЬНОСТЕЙ | 1972 |

|

SU430517A1 |

| Устройство для контроля блоков постоянной памяти | 1983 |

|

SU1104590A1 |

| УСТРОЙСТВО ДЛЯ УПРАВЛЕНИЯ РЕЖИМАМИ СТРЕЛЬБЫ ЭЛЕКТРОИНИЦИИРУЕМЫХ ЗАРЯДОВ | 1993 |

|

RU2072072C1 |

Авторы

Даты

1978-02-25—Публикация

1976-11-25—Подача