Изобретение относится к вычислительной технике и может быть использовано как в качестве автономного решающего узла, так и в качестве составной части частотно-импульсных вьгчислительных устройств,

Известно множительно-делительное устройство для частотно-импульсных сигналов ij

Недостатком этого устройства являет ся появление динамической ошибки при измерении входных сигналов.

Известно также близкое по техническому решению к данному изобретению частотноимпульсное множительно-делительное устройство ,, содержащее , элементы И, дешифратор, первый вход которого соединен с единичным выходом первого триггера, а второй вход с единичным выходом второго триггера и первьтм входом первого элемента И , второй вход которого соединен с источником первой частотьт, а выход является выходом устройства. Первый и второй выходы дешифратора соединены с пер.выми входами второго и третьего элем ентов И соответственно, вторые входы которых соединены с источником второй частоты, в выходы каждого из элементов И соединены с нулевым и счетным входами первого и второго триггеров соответственно.

Недостаток этого устройства в возникновении динамической ошибки, если одна из входных частот (или обе сразу) имеют во времени непродолжительные скачкообразные изменения.

Цель изобретения в снижени.и динамических погрешностей.

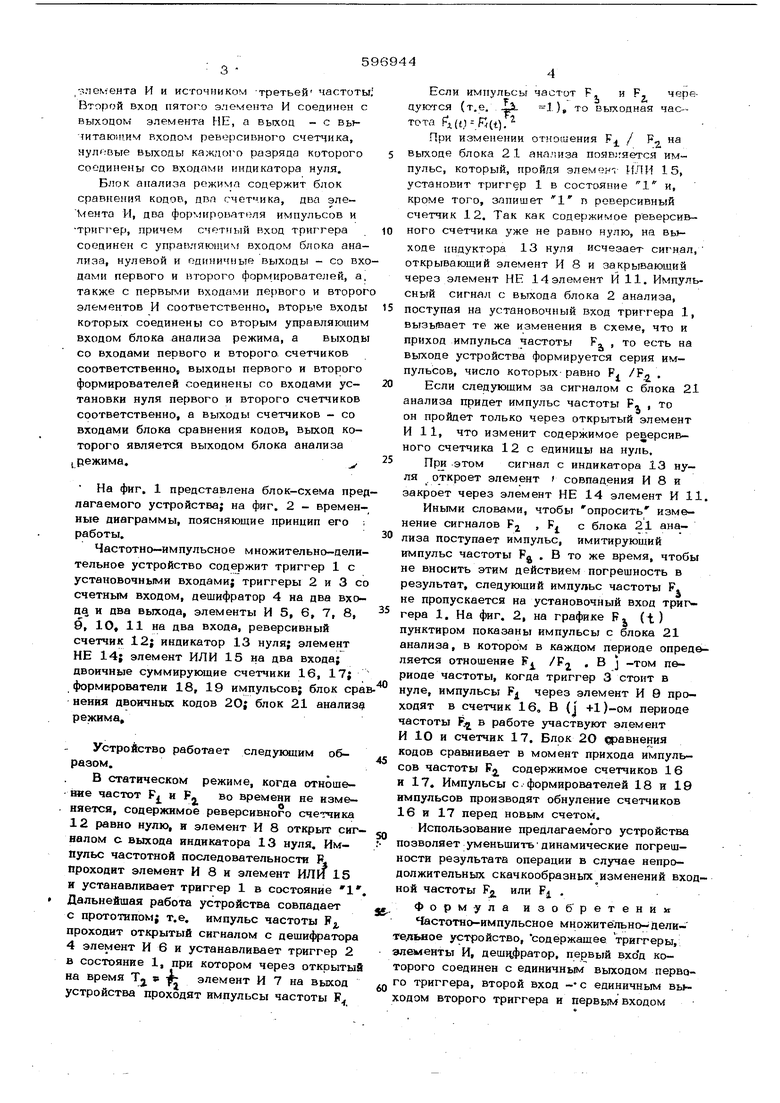

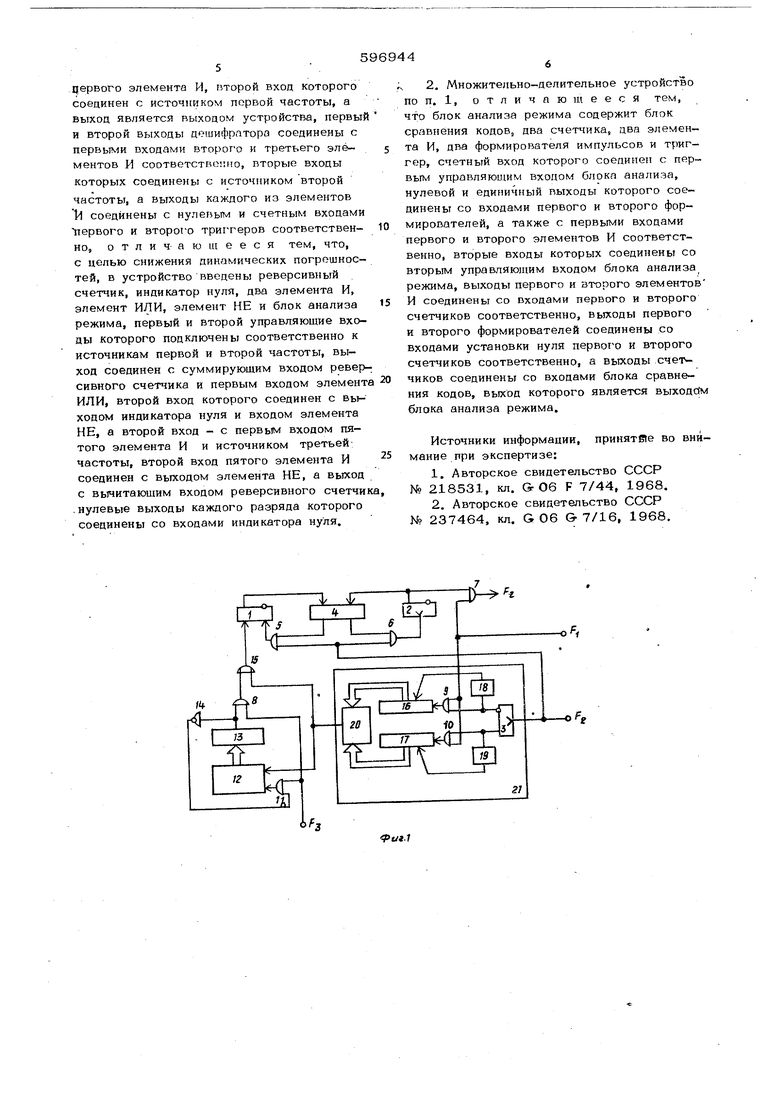

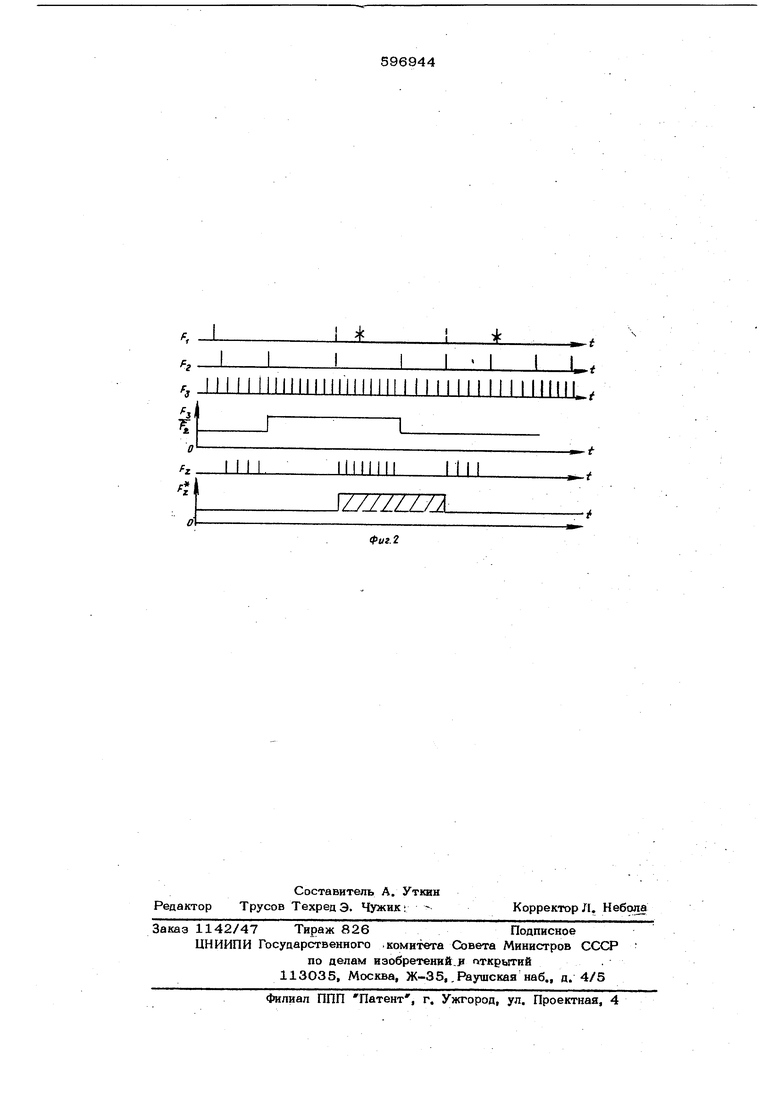

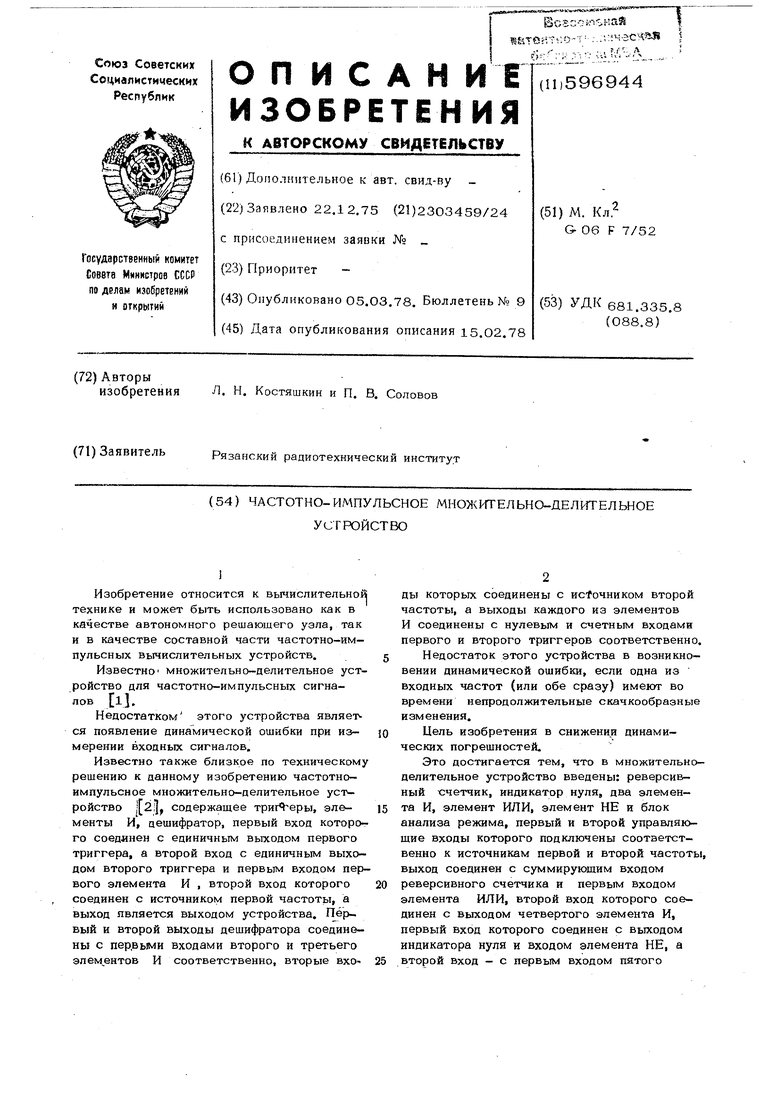

Это достигается тем, что в множительноделительное устройство введены: реверсивный счетчик, индикатор нуля, два элемента И, элемент ИЛИ, элемент НЕ и блок анализа режима, первый и второй управляющие входы которого подключены соответственно к источникам первой и второй частоты выход соединен с суммирующим входом реверсивного счетчика и первьгм входом элемента ИЛИ, второй вход которого соединен с Выходом четвертого элемента И, первый вход которого соединен с выходом индикатора нуля и входом элемента НЕ, а второй вход - с первым входом пятого /элемента И и источником -третьей частоты Второй вход ПЯТО1-О элемента И соединен с выходом элемента НЕ, а вьтхоц - с вьтчитаю111им вхопом реверсивного счетчика, нул.вые выходы каждого разряда которого соединены со входами индикатора нуля. Блок анализа режима содержит блок сравнения кодов, два счетчика, два элеЫента И, два формирователя импульсов и триггер, причем счетный вход триггера соединен с управляющим входом блока анализа, нулевой и единичные выходы - со вх дами первого и второго формирователей, а. также с первьми входами первого и второг элементов И соответственно, вторые входы которых соединены со вторым управляющим входом блока анализа режима, а выходы со входами первого и второго, счетчиков соответственно, выходы первого и второго формирователей соединены со входами установки нуля первого и второго счетчиков соответственно, а выходы счетчиков - со входами блока сравнения кодов, выход которого является выходом блока анализа J режима. На фиг, 1 представлена блок-схема пре лагаемого устройства; на фиг. 2 - временные диаграммы, поясняющие принцип его работы, Частотно-импульсное множительно-дели тельное устройство содержит триггер 1 с установочными входами; триггеры 2 и 3 с счетньтм входом, дешифратор 4 на два входа и два выхода, элементы И 5, 6, 7, 8, 9, 10, 11 на два входа, реверсивный счетчик 12j индикатор 13 нуля; элемент НЕ 14; элемент ИЛИ 15 на два входа; двоичные суммирующие счетчики 16, 17; формирователи 18, 19 импульсов; блок сра неняя двоичных кодов 20; блок 21 анализу режима. устройство работает следукшим образом, В статическом режиме, когда отношение частот FI и Fj во времени не изменяется, содержимое реверсивного счетчика 12 равно нулю, и элемент И 8 открыт сиг валом с выхода индикатора 13 нуля. ИмНульс частотной последовательности F проходит элемент И 8 и элемент ИЛИ 15 и устанавливает триггер 1 в состояние 1 Дальнейшая работа устройства совпадает с прототипом; т.е. импульс частоты F проходит открытый сигналом с дешифратора 4 элемент И 6 и устанавливает триггер 2 в состояние 1, при котором через открытый на время T,j fr элемент И 7 на выход устройства проходят импульсы частоты F Если импульсы частот F, i, чередуются (т.е. .ХЗ- -I), то выходная частота Fi(t,) R(t). При изменении отношения F. / Р на вьгходе блока 21 анализа появ;гяется импульс, который, пройдя элемент- ИЛИ 15, установит триггер 1 в состоя ие 1 и, кроме того, запишет 1 п реверсивный счетчик 12. Так как содержимое реверсивного счетчика уже не равно нулю, на вььходе индуктора 13 нуля исчезает сигнал, открывающий элемент И 8 и закрывающий через элемент НЕ 14 элемент И 11. Импульсный сигнал с выхода блока 2 анализа, поступая на установочный вход триггера 1, вызывает те же изменения в схеме, что и приход импульса частоты F , то есть на вьрсоде устройства формируется серия импульсов, число которых равно Р /Р . Если следующим за сигналом с блока 21 анализа придет импульс частоты F, , то он пройдет только через открытый элемент И 11, что изменит содержимое реверсивного счетчика 12с единицы на нуль, ripji этом сигнал с индикатора 13 нуля откроет элемент совпадения И 8 и закроет через элемент НЕ 14 элемент И 11. Иными словами, чтобы опросить измес блока 21 ана- нение сигналов FJ , F имитирующий лиза поступает импульс, импульс частоты F . В то же время, чтобы не вносить этим действием погрешность в результат, следующий импульс частоты F. не пропускается на установочный вход триггера 1, На фиг. 2, на графике F. (t ) пунктиром показаны импульсы с блока 21 анализа, в котором в каждом периоде определяется отношение F /F . В j -том периоде частоты, когда триггер 3 стоит в нуле, импульсы F через элемент И 9 проходят в счетчик 16, В ( +1)-ом периоде частоты F в работе участвуют элемент И 10 и счетчик 17. Блок 2О уравнения кодов сравнивает в момент прихода импульсов частоты F2 содержимое счетчиков 16 и 17. Импульсы с. формирователей 18 и 19 импульсов производят обнуление счетчиков 16 и 17 перед новым счетом. Использование предлагаемого устройства позволяет уменьшить динамические погрешности результата операции в случае непродолжительных скачкообразных изменений входной частоты Fjj или F .. формула изобретенииг Частотно-импульсное множительно-делиельяое устройство, содержащее триггеры, лементы И, дешифратор, первый вход коорого соединен с единичным выходом первого триггера, второй вход - с единичным выодом второго триггера и первым входом цервого элемента И, второй вход которого соединен с источником первой частоты, а выход является выходом устройства, первы и второй выходы дешифратора соединены с первьми входами второго и третьего элементов И соответство :ио, вторые входы которых соединены с источником второй частоты, а выходы каждого из элементов М соединены с нулег5Ь1М и счетным входами первого и второго триггеров соответственно, отлич-ающееся тем, что, с целью снижения динамических погрешностей, в устройство введены реверсивный счетчик, индикатор нуля, два элемента И, элемент ИЛИ, элемент НЕ и блок анализа режима, первый и второй управляющие входы которого подключены соответственно к источникам первой и второй частоты, выход соединен с суммирующим входом ревер сивного счетчика и первым входом элемент ИЛИ, второй вход которого соединен с выходом индикатора нуля и входом элемента НЕ, а второй вход - с первьтм входом пятого элемента И и источником третьей частоты, второй вход пятого элемента И соединен с выходом элемента НЕ, а вькод с вьяитающим входом реверсивного счетчик нулевые выходы каждого разряда которого соединены со входами индикатора нуля. 2. Множительно-делительное устройство по п. 1, отличающееся тем, что блок анализа режима содержит блок сравнения кодов, два счетчика, два элемента И, два формирователя импульсов и триггер, счетный вход которого соединен с первым управляющим входом блока анализа, нулевой и единичный выходы которого соединены со входами первого и второго формирователей, а также с первыми входами первого и второго элементов И соответственно, вторые входы которых соединены со вторым управляющим входом блока анализа режима, выходы первого и второго элементов И соединены со входами первого и второго счетчиков соответственно, выходы первого и второго формирователей соединены со входами установки нуля первого и второго счетчиков соответственно, а выходы счет чиков соединены со входами блока сравнекия кодов, вь1ход которого является выходом блока анализа режима. Источники информации, принятие во внимание при экспертизе: 1,Авторское свидетельство СССР N« 218531, кл. G-O6 F 7/44, 1968. 2.Авторское свидетельство СССР № 237464, кл. G 06 G-7/16, 1968.

I Jf /с, JI

fIIIII

.. M niinilllHIHillMI inn

;-, JJLUJJ

l////////i

| название | год | авторы | номер документа |

|---|---|---|---|

| Многоканальное устройство для контроля параметров | 1987 |

|

SU1444714A1 |

| Частотно-импульсное множительно-дЕлиТЕльНОЕ уСТРОйСТВО | 1979 |

|

SU813426A1 |

| Цифровое множительно-делительное устройство | 1981 |

|

SU1012246A2 |

| ЦИФРОВОЙ ТЕРМОМЕТР | 1992 |

|

RU2039953C1 |

| ЧАСТОТНО-ИМПУЛЬСНОЕ МНОЖИТЕЛЬНО-ДЕЛИТЕЛЬНОЕУСТРОЙСТВО | 1972 |

|

SU424188A1 |

| Устройство автоматической подстройки частоты | 1987 |

|

SU1539999A2 |

| Многоканальное цифровое устройство для обработки информации частотных преобразователей | 1982 |

|

SU1083197A1 |

| Измерительное информационное устройство | 1984 |

|

SU1314360A1 |

| Устройство допускового контроля | 1979 |

|

SU864538A1 |

| Коммутатор | 1985 |

|

SU1354408A1 |

Авторы

Даты

1978-03-05—Публикация

1975-12-22—Подача