(54) ЧАСТОТНО-ИМПУЛЬСНСЖ МНОЖИТЕЛЬНС. ДЕЛИТЕЛЬНСЖ УСТРСЙСТВО

| название | год | авторы | номер документа |

|---|---|---|---|

| ЧАСТОТНО-ИМПУЛЬСНЫЙ ЛИНЕЙНЫЙ ИНТЕРПОЛЯТОР | 1973 |

|

SU407317A1 |

| Частотно-импульсное делительное устройство | 1978 |

|

SU763914A1 |

| ЧАСТОТНО-ИМПУЛЬСНЫЙ ФУНКЦИОНАЛЬНЫЙ ПРЕОБРАЗОВАТЕЛЬ | 1972 |

|

SU425182A1 |

| ЧАСТОТНО-ИМПУЛЬСНОЕ МНОЖИТЕЛЬНО-ДЕЛИТЕЛЬНОЕУСТРОЙСТВО | 1968 |

|

SU217047A1 |

| Частотно-импульсное множительно-делительное устройство | 1975 |

|

SU556437A1 |

| ЧАСТОТНО-ИМПУЛЬСНОЕ МНОЖИТЕЛЬНО-ДЕЛИТЕЛЬНОЕ УСТРОЙСТВО | 1992 |

|

RU2012040C1 |

| Множительно-делительное устройство | 1977 |

|

SU788128A1 |

| МНОЖИТЕЛЬНО-ДЕЛИТЕЛЬНОЕ УСТРОЙСТВО | 2002 |

|

RU2210102C1 |

| Устройство для умножения импульсных сигналов | 1980 |

|

SU879600A1 |

| Устройство для дифференцирования частоты повторения импульсов | 1974 |

|

SU525117A1 |

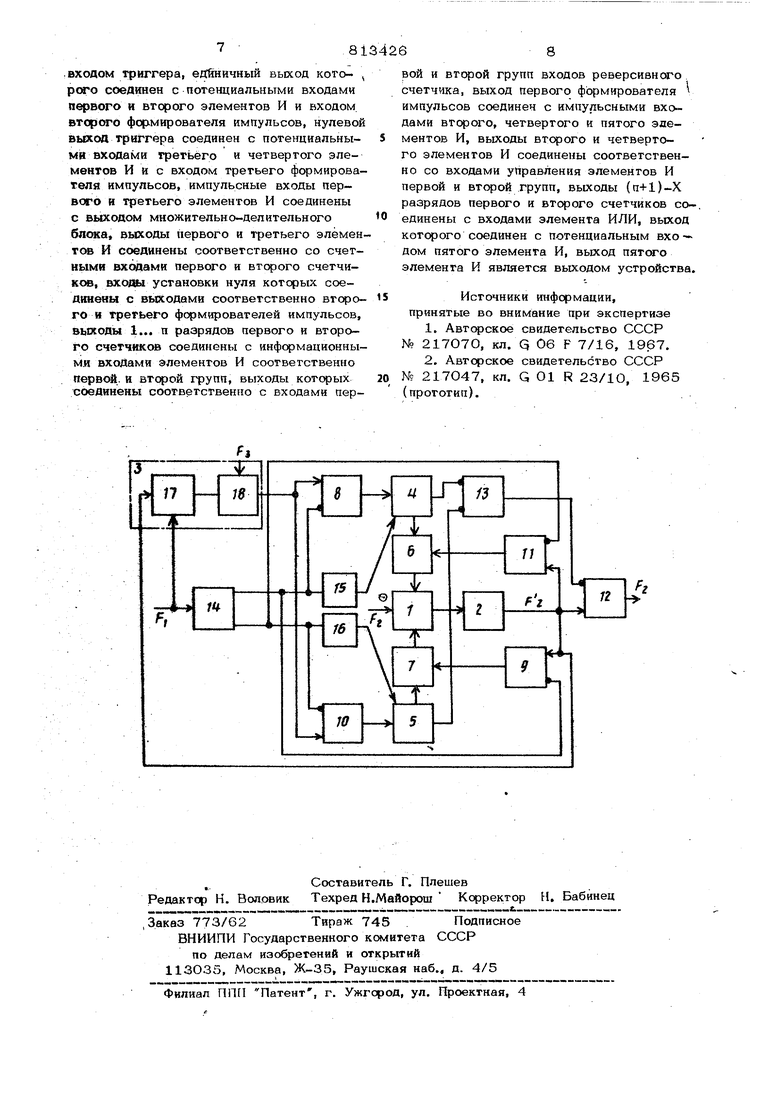

Изобретение относится к вычислител ной технике н может быть использовано в вьпвсднтёльных н управляющих комплексах в качестве вычислительного устройства, совершающего математические операции над сигналами, тфедставленными в частотно-импульсной . Известно частотно-импульсное множи тельно-делительное устрсйство, представ ляющее собой замкнутую систему компен сационнсго принципа действия, в цепи прямой и офатной передач в которсй включены схемы логических триггерных копец ЛТК-1 и ЛТК-2. Тракт усиления состоит из реверсивнсоо счетчи- ка PC и двоичного умножителя частоты ДУ. Указанное устройство обладает моделирующей зависимостью вида Р -fiJ -Efla. . Величина наблюдательного времени определйется из соотношения г .п Расчеты псжазывают, что переходасй провесе заканчивается в течение нескольких сот периодов входной-частоты Cl . . Наиболее близким к предложенному йвляется частотно-импульсное множительноделнтельное устройство представляющее собой операционную модель развертывающего принципа действия и содержащее реверсивный счетчик PC, формирователь импульсов ФИ и множительно-:делительный блок, состоящий из лся ического триггерного кольда и элемента И. Моделирующая зависимость для устройства имеет вид: Сотласно (финципу работы устройства результат операции формируется в течение одного периода выходной частоты L2. Однако, рассматриваемое устройство не находит шнрсжого применения в технике частотно-импульсного моделирования в силу следующих причин. 1. Наличие существенного ослабления в вькодном сигнале, как по входу F , та )ии по входу : характеризуемое коэф циентом равным. П1--Ь:. Так как; величина коэффициента ослабления влияет на среднеквадратичную ошибку G (РЗ) в последовательности а б (Р,) .У- /и л (.« Jr«1 то уменьшение ее является нежелательным. 2. Предъявление жестких требований к стенени равномерности сигнала Р так как наличие пульсации в последовательности F-I приводит к появлению существенной по величине погрешности в реаультирующем сигнале. Наличие ограничений накладываемых на диапазон изменения входной последовательности Fj Согласно принципу работы в устройствепрототипе должно соблюдаться условие ; , -. . . . Цель изобретения - увеличение точности и расширение области применения устройства за счет уменьшения влияния пульсации. Указанная Цель достигается тем, что в частотно -импульсное множительно-делительное устройство, содержащее реверсивный счетчик, формирователь импульсов, множительно-делительный блсж, при этом, разрядные выходы реверсивного счетчика соединены с соответствующими входами формирователя импульсов, выход которого соединен с входом первого сомножителя множительно-делительного блока, вход второго сомножителя которого является входом делителя устройства вход делителя множительно-делительного блсжа с входом первого сомножителя уст ройства, а вход вычитания реверсивного счетчика является входом второго сомно жителя устрсмйства, дополнительно введены два (П +1)-разрядных счетчика, две группы элементов И, элемент И, элемент ИЛИ, триггер н формирователи импульсов, причем вход первого сомножителя устройства соединен со счетным входом триггера, единичный выход которого соединен с потенциальными входам первого и второго элементов И и входом второго формирователя импульсов, нулевсА выход триггера соединен с потенци альными входами третьего и четвертого элементов И и с входом третьего форми рователя импульсов, импульсные входы первого и третьего элементов И соединены с выходом множительно-делительного блока, выходы первого и третьего элементов И соединены соответственно со счетными входами первого и BTqjoro счетчиков, входы установки нуля которых соединены с выходами соответственно второго и третьего ффмирователей импульсов, выходы 1... п разрядов первого и второго счетчиков соединены с информационными входами элементов И соответственно первой и второй групп, выходы которых соединены соответственно с входами первой и второй групп входов реверсивного счетчика, выход первого формирователя импульсов соединен с импульсными входами втсфого, четвертого и пятого элементов И, выходы второго и четвертого элементов И. соединены соответственно со входами управления элементов И первой и втфой групп, выходы {П+1) - X разряд. Дов первого и второго счетчиков соединены с входами элемента ИЛИ, выходы которого соединен с потенциальным входом пятого элемента И, выходы пятого элемента И является выходом устройства. На чертеже приведена схема устройства., Устройство содержит реверсивный счетчик 1 (п-разрядный) первый формирователь 2 импульсов, множительно-Делительный блок 3, счегчики 4 и 5 (п+1)разрядные группы элементов И 6 и 7, элементы И8 - 12, элемент ИЛИ 13, триггер 14, формирователи 15 и 16 импульсов, логическое триггерное кольцо 17, элемент И 18. В предлагаемом .устройстве импу Ьсные последовательности, частоты котфых F-i)f-aiP3 пропорциональны математическим величинам, поступают соответственно: -на вход ЛТК 17 и триггера 14; -на вычитающую шину реверсивного счетчика 1; - на импульсный вход элемента И 18 множительно-делительного блока 3. ,Устройство работает следующим образом. Предположим, что в рассматриваемый момент времени триггер 14 находится в таком состоянии, при котором на его нулевом выходе (нижний на чертеже) сформировался разрешающий сигнал, в счетчиках 5 и 4 записано некоторое число Р . В момент обнуления реверсивного счетчика 1 формирователем импульсов 2, вырабатывается сигнал импульсной последоватйльности, частота которой равна ,Р . Z р Импульс последовагельности Р йосгупае на вход первого сомножителя множительно-делительного блока 3 и через элемен 11 на управляющий вход группы элементов И6, переписывая при этом код числа Р из счетчика 4 в реверсивный счетчик 1. Одновременно импульсы последовательности РЗ- поступают на вход схемы совпадения 12. Если входной сигнал P-t не.вышел за заданный диапазон изменения, то в разрядах и н- -т счетчиков 4 и 5 будут записаны нули, что обуслав ливает появление разрешающего сигнала на входе элемента ИЛИ 13 и на потенциальном входе элемента И 12. При этом импульсы вырабатьшаемый формиро телем 2 через элемент И 12 поступает на вход устройства, С приходом последу ющегр импульса последовательности P-f триггер 14 занимает положение при котором формируется разрешающий сигна на его единичном выходе. По переднему фронту сигнала триггера 14 запускается фсрмирователь 15, импульс которого ус- танав1ливает счетчик в нулевое состояние Одновременно импульс последовательноети F-i воздействует на логическое триггерное кольцо 17, формируя на его выхо де сигнал длительностью i, В течение которого на входы элементов И 8 и 1О поступает Р число импульсов равное Так как по потенциальному входу открыт элемент И 8, то число импульсов Р запи шется и счетчик 9. С учетом равенства (7) и (9) результирующая частота F. определяется соотношением, .До прихода следующего импульса последовательности FT с появлением каждого сигнала Р. происходит передача числа Р из счетчика 5 в реверсивный счетчик 1, Из приведенного описания принципа работы предлагаемой схемы частотно-импульсного множительно-делительн.ого устройства следует, что каждый импульс последовательности подлежит обработке. Наличие неравномерности в последователь ности FT не приведет к появлению погрешности в результирующем сигнале F. Из принципа работы устройства также спедует, что введение счетчиков 4 и 5 позволяет обеспечить нормальное функцио нирование предлагаемой модели при раз- личных значениях частоты F , т.е. RjiPa При использовании устройства в режиме работы Р;г РЭ О каналу имеет место усиление сигнала. Принимая во внимание, что предлагаемое МДУ наиболее целесообразно применять в роли масштабирующего блсяса с регулируемым коэффициентом передачи, указанный режим F F является основным. Следовательно построение операционных частотно-импульсных моделей (суммирующих, функциональных) на базе предлагаемого устр йства, используемого в роли масштабяр тощего блсяса, позволит улучшить динамические характеристике последующих на два-три , особенно, когда входные величины/представлены низкочастотными последовательностями при использовании предлагаемого устрс44ства отпадает необходимость в постановке сглаживающего блсжа при представлении P-J в виде неравномерней импульсной последовательности. Формула изобретения Частотно-импульсное множитв №но-делительное устройство содержащее реверсивный счетчик, формирователь импульсов, множите/1 ьно-делительный блок, при этом разрядные BbKojU i реверсивного счетчика соединены с соответствующими входами формярсюателя импульсов, выход которого соединен с входом первого сомножителя множительно-делительнсмго блока, вход второго сомножителя которого является входом делителя устройства, вход делнтеля множительно-делительного бл(Жа - входом первого сомножителя устройства, а вход вычитания реверсивного счетчика является входом второго сомножителя устройства, отличающееся тем, что, с целью увеличения точности вычислений и расширения области применения устройства за счет уменьшения влияния пульсации, в него дополнительно введены два {п+1)-разрядных счетчвпка, ае группы элементов И, элементы И, лемент ИЛИ, триггер и формирователи мпульсов, причем вход первсяо сомяо ителя устройства соеданен со счетным

.входом триггера, единичный выход когормо соединен с потенциальными входами первого и второго элементов И и входом второго формирователя импульсов, нулевой выход триггера соединен с потенциальными вхсюами третьего и четвертого элементов И и с входом третьего формирователя импульсов, импульсные входы первого и третьего элементов И соединены G выходом множйтельно-делительного

блока, выходы первого и третьего элементе И соединены соответственно со счетными входами первого и второго счетчик в, вхошл установки нуля которых соединены с выходами соответственно второГО и Третьего формирователей импульсов, выходы 1... п разрядов первого и второго счетчиков соединены с информационными входами элементов И соответственно первой, и втфой групп, выходы которых соединены соответственно с входами первой и второй групп входов реверсивнся о счетчика, выход первого формирователя импульсов соединен с импульсными входами BTopoi o, четвертого и пятого элементов И, выходы второго и четвертого элементов И соединены соответственно со входами управления элементов И первой и второй групп, выходы (п+1)-Х разрядов первого и второго счетчиков со единены с входами элемента ИЛИ, вьосод котсрого соединен с потенциальным входом пятого элемента И, выход пятого элемента И является выходом устройства

Источники информации, принятые во внимание при экспертизе

Авторы

Даты

1981-03-15—Публикация

1979-01-24—Подача