(54) УСТРОЙСТВО ДЛЯ УПРАВЛЕНИЯ ПЕЧАТАЮЩИМ МЕХАНИЗМОМ

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для подготовки данных | 1988 |

|

SU1617429A1 |

| Устройство для контроля блоков памяти | 1985 |

|

SU1270799A1 |

| Система управления алфавитно-цифровым построчно-печатающим устройством | 1972 |

|

SU474802A1 |

| Устройство для управления форматом печати информации | 1986 |

|

SU1354227A1 |

| Устройство для регистрации параметров химических источников тока | 1978 |

|

SU765915A1 |

| Устройство для регистрации парамет-POB ХиМичЕСКиХ иСТОчНиКОВ TOKA | 1978 |

|

SU817823A1 |

| Устройство для контроля памяти | 1983 |

|

SU1129656A1 |

| Печатающее устройство с переменным форматом | 1980 |

|

SU877586A1 |

| Логический анализатор | 1986 |

|

SU1432527A1 |

| Устройство для обработки радиосигналов | 1980 |

|

SU955083A1 |

Изобретение относится к области автоматики и вычислительной техники и может быть использовано в построчно печатающих быстродействующих алфавитно-цифровых устройствах.

Известно устройство для управления печатающим механизмом, содержащее блок сопряжения, подключенный к блоку памяти, счетчик числа строк, соединенный с блоком управления, генератор синхросигналов, подключенный к схеме сравнения, и соединенный с ней формирователь сигналов печати 1.

Наиболее близким техническим рещением к данному изобретению является устройство для управления печатающим механизмом, содержащее блок сопряжения, подключенный к блоку памяти, к последовательно соединенным первому и второму регистрам, соединенным с блоком памяти, с третьим и четвертым регистрами, первую схему сравнения, подключенную к блоку памяти, первому и третьему регистрам и к формирователю кода позиции, соединенному с третьим и четвертым регистрами, формирователь сигналов печати, подключенный к четвертому регистру, соединенному с блоком памяти, генератор синхросигналов и формирователь сигналов транспорта 2.

Недостатком известных устройств для управления печатающим механизмом является необходимость применения элементов с высоким быстродействием для получения достаточной скорости печати.

Целью изобретения является повыщение быстродействия устройства для управления печатающим механизмом без применения высокопроизводительных логических элементов и элементов памяти.

Это достигается тем, что предлагаемое устройство для управления печатающим механизмом содержит пятый и щестой регистры, вторую схему сравнения и формирователь синхросерий, причем первый и второй входы пятого регистра соединень с выходами третьего регистра, третий вход - с одним из выходов формирователя синхросерий и одним нз входов четвертого регистра, к другим входам которого подключены первый выход пятого регистра, выходы щестого регистра и выход первой схемы сравнения, соединенный с блоком памяти, другой выход формирователя синхросерий подключен ко вхОду формирователя кода позиции, его вход соединен с генератором синхросигналов, первый вход щестого регистра подключен к выходу второй схемы сравнения, соединенной с блоком памяти, второй вход - к выходу формирователя сигналов печати, третий вход-к выходу второго регистра, один из входов второй схемы сравнения подключен ко второму выходу формирователя кода позиции, два других входа соединены с соответствующими входами первой схемы сравнения, а второй выход пятого регистра соединен с формирователем сигналов транспорта.

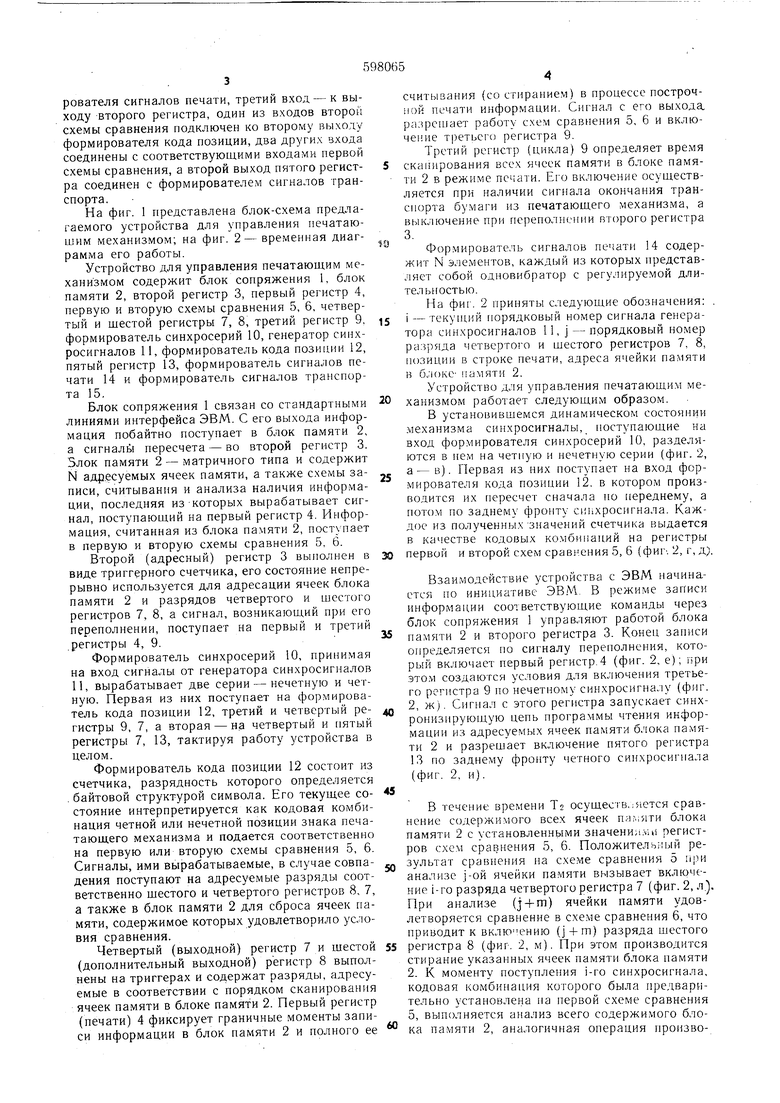

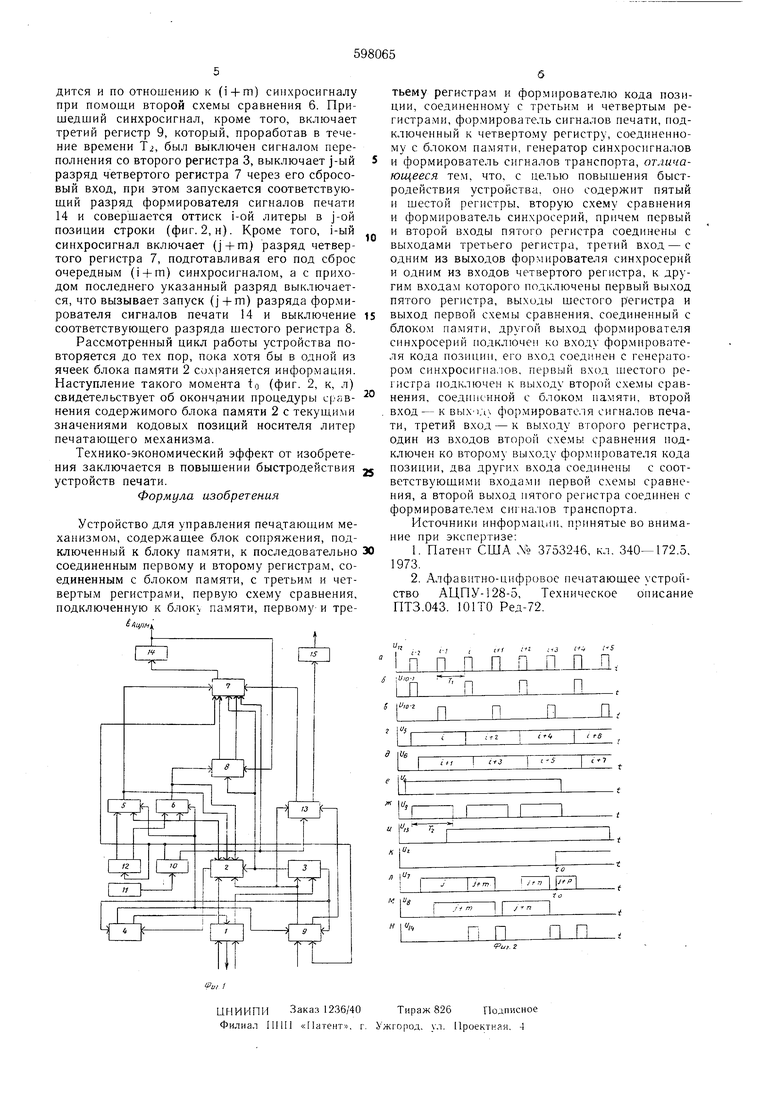

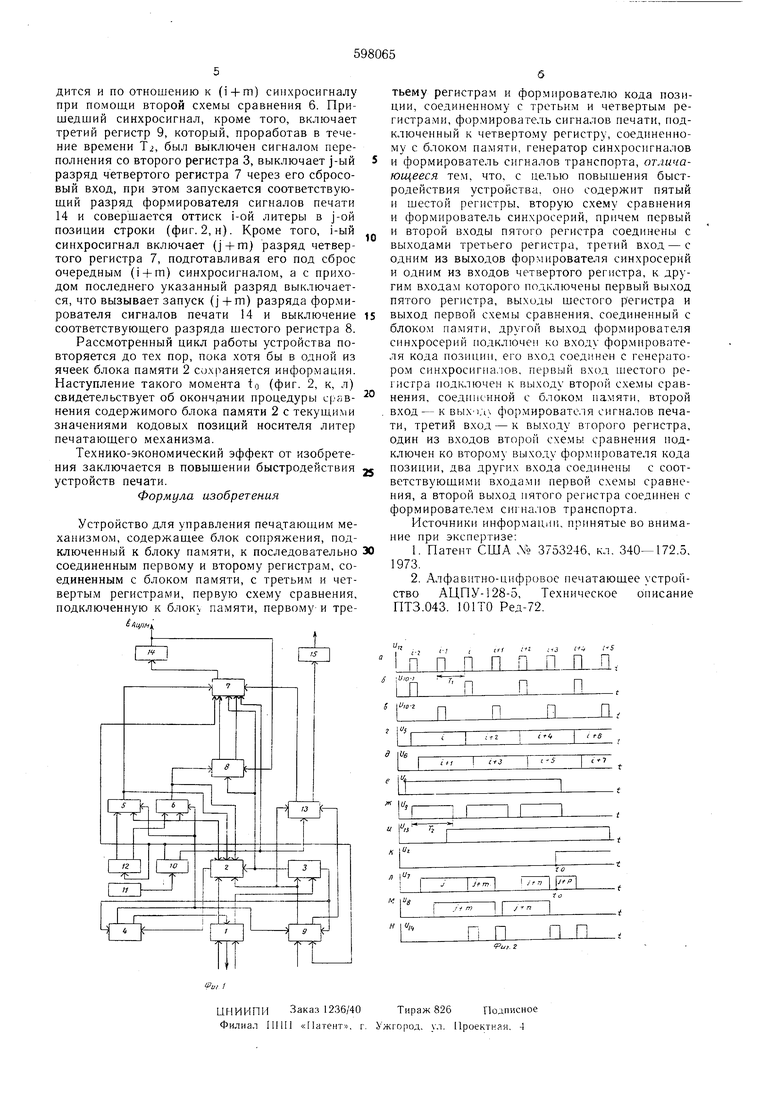

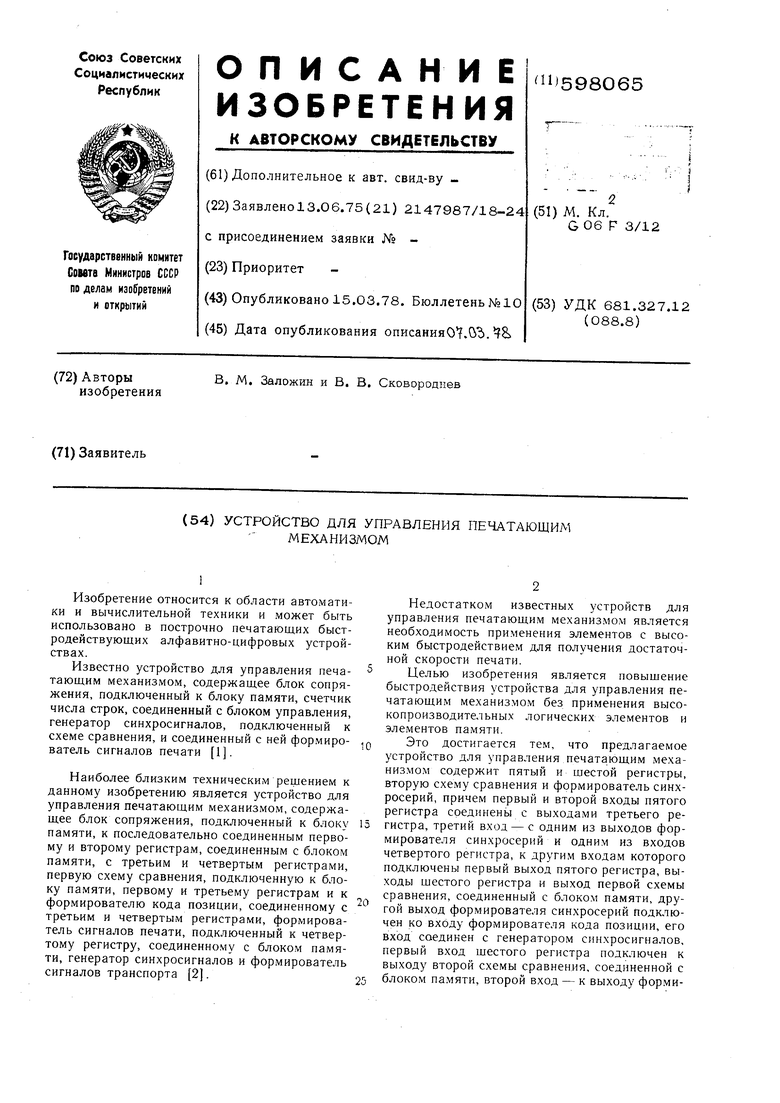

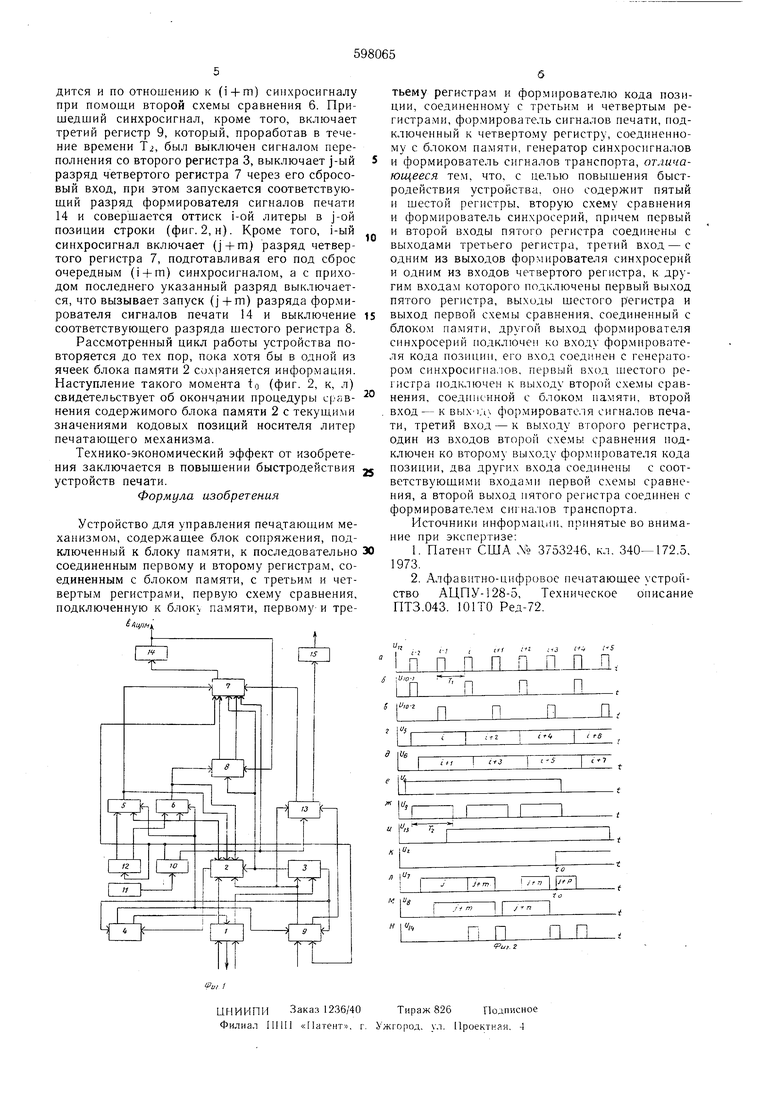

На фиг. 1 представлена блок-схема предлагаемого устройства для управления печатающим механизмом; на фиг. 2-временная диаграмма его работы.

Устройство для управления печатающим механизмом содержит блок сопряжения 1, блок памяти 2, второй регистр 3, первый регистр 4, первую и вторую схемы сравнения 5, 6, четвертый и щестой регистры 7, 8, третий регистр 9, формирователь синхросерий 10, генератор синхросигналов 11, формирователь кода позиции 12, пятый регистр 13, формирователь сигналов печати 14 и формирователь сигналов транспорта 15.

Блок сопряжения 1 связан со стандартными линиями интерфейса ЭВМ. С его выхода информация побайтно поступает в блок памяти 2, а сигналь пересчета - во второй регистр 3. Злок памяти 2 - матричного типа и содержит N адресуемых ячеек памяти, а также схемы записи, считывания и анализа наличия информации, последняя из-которых вырабатывает сигнал, поступающий на первый регистр 4. Информация, считанная из блока памяти 2, поступает в первую и вторую схемы сравнения 5, 6.

Второй (адресный) регистр 3 выполнен в виде триггерного счетчика, его состояние непрерывно используется для адресации ячеек блока памяти 2 и разрядов четвертого и шестого регистров 7, 8, а сигнал, возникающий при его переполнении, поступает на первый и третий регистры 4, 9.

Формирователь синхросерий 10, принимая на вход сигналь от генератора синхросигналов 11, вырабатывает две серии - нечетную и четную. Первая из них поступает на формирователь кода позиции 12, третий и четвертый регистры 9, 7, а вторая - на четвертый и пятый регистры 7, 13, тактируя работу устройства в целом.

Формирователь кода позиции 12 состоит из счетчика, разрядность которого определяется .байтовой структурой символа. Его текущее состояние интерпретируется как кодовая комбинация четной или нечетной позиции знака печатающего механизма и подается соответственно на первую или вторую схемы сравнения 5, 6. Сигналы, ими вырабатываемые, в случае совпадения поступают на адресуемые разряды соответственно щестого и четвертого регистров 8, 7, а также в блок памяти 2 для сброса ячеек памяти, содержимое которых удовлетворило условия сравнения.

Четвертый (выходной) регистр 7 и шестой (дополнительный выходной) регистр 8 выполнены на триггерах и содержат разряды, адресуемые в соответствии с порядком сканирования ячеек памяти в блоке памяти 2. Первый регистр (печати) 4 фиксирует граничные моменты записи информации в блок памяти 2 и полного ее

считывания (со стиранием) в процессе построч 1ой печати информации. Сигнал с его выхода разрешает работу с.хем сравнения 5, 6 и включение третьего регистра 9.

Третий регистр (цикла) 9 определяет время 5 сканирования всех ячеек памяти в блоке памяти 2 в режиме печати. Его включение осуществляется при наличии сигнала окончания транспорта бумаги из печатающего механизма, а выключение при переполпем|ии второго регистра 3.

Фор.мирователь сигналов печати 14 содержит N элементов, каждый из которых представляет собой одновибратор с регулируемой длительностью.

На фиг. 2 приняты следующие обозначения: 5 i - текуниш порядковый номер сигнала генератора синхросигналов 11, j - порядковый номер разряда четвертого и шестого регистров 7, 8, позиции в строке печати, адреса ячейки памяти в б.поке- памяти 2.

Устройство для управления печатающим ме0 ханизмом работает следующим образом.

В установившемся динамическом состоянии .механизма синхросигналы, поступающие на вход формирователя синхросерий 10, разделяются в нем на четную и нечетную серии (фиг. 2, - а - в). Первая из них поступает на вход формирователя кода позиции 12. в котором производится их пересчет сначала по переднему, а потом по заднему фронту синхросигнала. Каждое из полученных значений счетчика выдается в качестве кодовых ко.мбипаций на регистры 0 первой и второй схем сравнения 5, 6 (фиг-. 2, г, д;.

Взаимодействие устройства с ЭВМ начинается по инициативе ЭВМ. В режиме записи информации соответствующие команды через блок сопряжения 1 управляют работой блока памяти 2 и второго регистра 3. Конец записи определяется по сигналу переполнения, который включает первый регистр. 4 (фиг. 2, е); при этом создаются условия для включения третьего регистра 9 по нечетному синхросигналу (ф1П 2, ж). Сигнал с этого регистра запускает синхронизирующую цепь программы чтения информации из адресуемых ячеек памяти блока памяти 2 и разрешает включение пятого регистра 13 по заднему фронту четного синхросигнала (фиг. 2, и).

В течение времени То осуществ.:яется сравнение содержимого всех ячеек памяти блока памяти 2 с установленньши значении.-у-и регистров схем сравнения 5, 6. Положительный результат сравнения на схе.ме сравнения 5 при анализе j-ой ячейки памяти вызывает включение i-ro разряда четвертого регистра 7 (фиг. 2, л,. При анализе (j + m) ячейки памяти удовлетворяется сравнение в схе.ме сравнения 6, что приводит к (j-1-m) разряда шестого

регистра 8 (фиг. 2, м). При этом производится стирание указанных ячеек памяти блока памяти 2. К моменту поступлепия i-ro синхросигнала, кодовая комбинация которого была предварительно установлена па первой схеме сравнения 5, выполняется анализ всего содержимого блока памяти 2, аналогичная операция нроизво

Авторы

Даты

1978-03-15—Публикация

1975-06-13—Подача