Изобретение относится к запоминающим устройствам (ЗУ), в частности к устройствам для контроля ЗУ.

Известно устройство, позволяющее реализовать проверяющие тесты, .определяющие сохранность информации по данному адресу при обращении к другим адресам, что позволяет эффективно использовать его для контроля полупроводниковой памяти 1. Однако известное устройство не позволяет обеспечить возможность регенерации содержимого запоминающих ячеек при контроле динамической оперативной памяти.

Наиболее близким техническим рещением к изобретению является устройство для контроля памяти, содержащее формирователь тестовых сигналов, формирователь сигналов записи и считывания, блок останова, схему сравнения, регистр числа, блок управления, триггер, первый и второй регистры адреса, блок местного управления и коммутатор, причем входы регистров адреса подключены соответственно к первому и второму выходам блока управления, а выходы - к одним из входов коммутатора, вход формирователя тестовых сигналов соединен с третьим выходом блока управления, а выходы соединены соответственно с одним из входов регистра числа и первыми входами схемы сравнения и формирователя сигналов записи и считывания, вторые входы которых подключены соответственно к выходу регистра числа и первому выходу блока местного управления, второй выход и вход которого подключены соответственно к входу блока управления и выходу блока останова, вход которого соединен с выходом схемы сравнения, четвертый выход блока управления подключен к входу триггера, третий регистр адреса, элементы И, элемент НЕ и формирователь сигналов регенерации, входы которого подключены соответственно к третьему выходу блока управления, а первый выход соединен с входом элемента НЕ и одним из входов первого элемента И, другой вход которого подключен к выходу триггера, входы третьего регистра адреса подключены соответственно к второму выходу формирователя сигналов регенерации и щестому выходу блока -управления, а выход соединен с Ъдним из элементов НЕ и третьим входом формирователя сигналов записи и считывания, выходы элементов И подключены к другим входам коммутатора.

В этом устройстве обеспечена возможность регенерации содержимого запоминающих ячеек при. контроле динамической памяти с паспортным значением периода регенерации Трет... содержимого запоминающих ячеек 2.

Недостатком данного устройства является отсутствие возможности формирования режима прерывания по признаку с переменной длительностью паузы между обращениями к соседним столбцам матрицы накопителя динамического оперативного ЗУ, что не позволяет определить запас работоспособности ЗУ.

5 Цель изобретения - расщирение области применения устройства контроля за счет формирования режима прерывания для определения области работоспособности (ОР) контролируемой памяти.

Поставленная цель достигается тем, что

10 в устройство для контроля памяти, содержащее блок управления, формирователь тестовых сигналов, формирователь адресных сигналов, формирователь сигналов записи и считывания, регистр числа, блок сравне15 ния, блок останова, блок местного управления, первый счетчик, причем первый, второй, третий, четвертый, пятый и шестой выходы блока управления подключены соответственно к первым входам формирователя тестовцх сигналов, формирователя сигналов записи

20 и считывания, первого счетчика, формирователя адресных сигналов, блока сравнения и блока останова, вход блока управления подключен к выходу блока местного управления, первый выход формирователя тесто5 вых сигналов подключен к второму входу блока сравнения, третий вход и выход которого соединены соответственно с первым выходом регистра числа и вторым входом блока останова, выход которого подключен к первому входу блока, местного управления,

30 первый выход первого счетчика соединен с вторым входом формирователя адресных сигналов, а второй выход первого счетчика подключен к вторым входам формирователя тестовых сигналов и формирователя сигналов записи и считывания, третий вход формирователя тестовых сигналов соединен с вторым выходом регистра числа, вход которого является входом устройства, второй выход формирователя тестовых сигналов, выход формирователя сигналов записи и

0 считывания и первый выход формирователя адресных сигналов являются выходами устройства, введены блок свертки по модулю два, второй и третий счетчики, блок сравнения, триггер, причем второй выход формирователя адресных сигналов соединен с первым входом блока свертки по модулю два, второй вход которого подключен к выходу третьего счетчика, вход которого соединен с первым выходом триггера, второй выход которого подключен к второму входу 50 блока местного управления, выход блока свертки по модулю два подключен к первым входам триггера и второго счетчика, выход которого соединен с первым выходом блока сравнения, выход которого подключен к второму входу триггера, вторые входы второго

55 счетчика и блока сравнения и третий вход триггера соединены соответственно с седьмым, восьмым и девятым выходами блока управления.

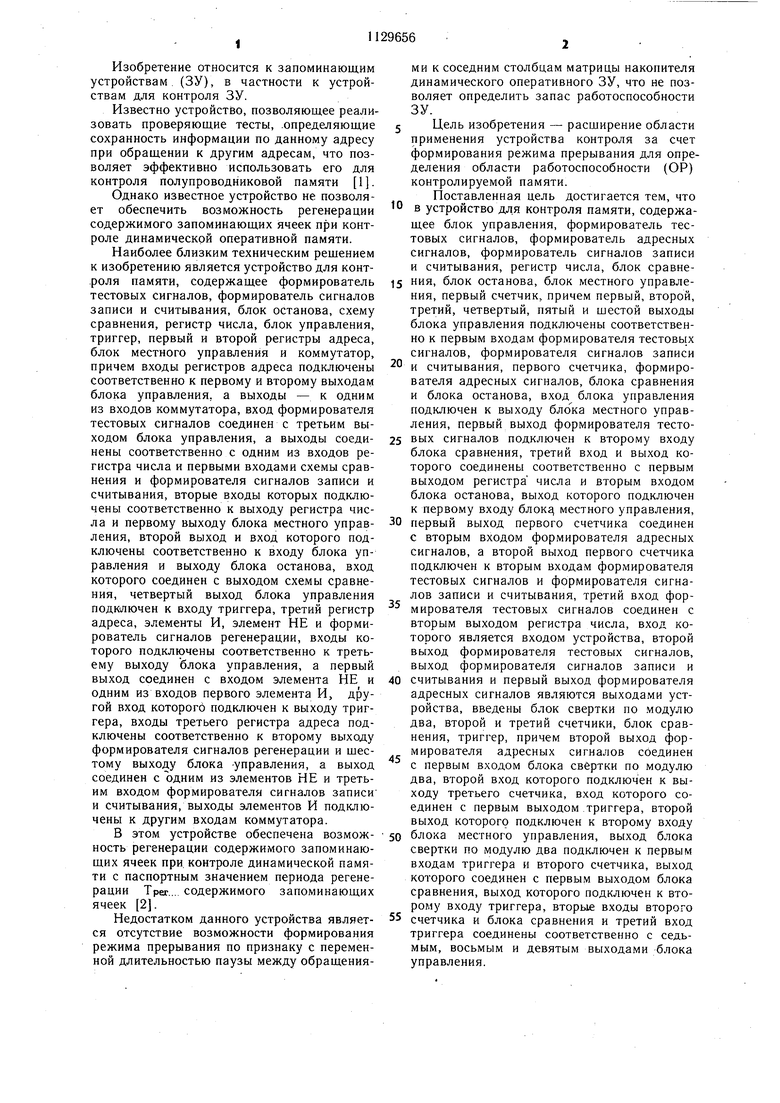

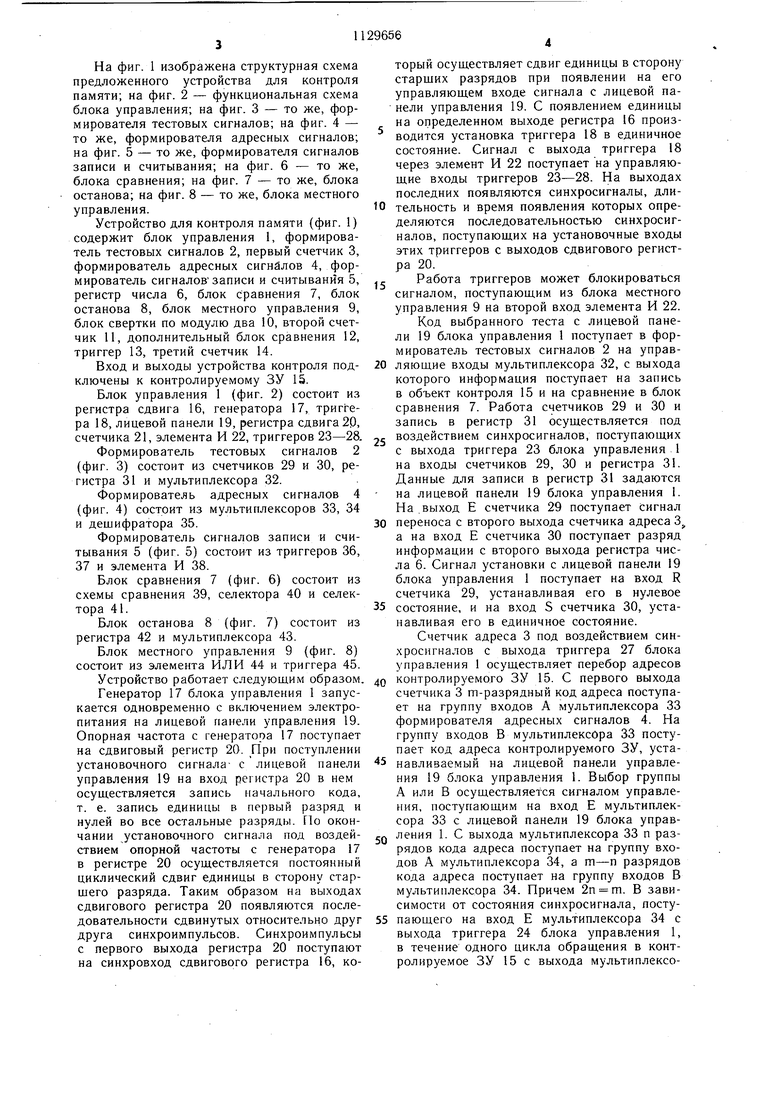

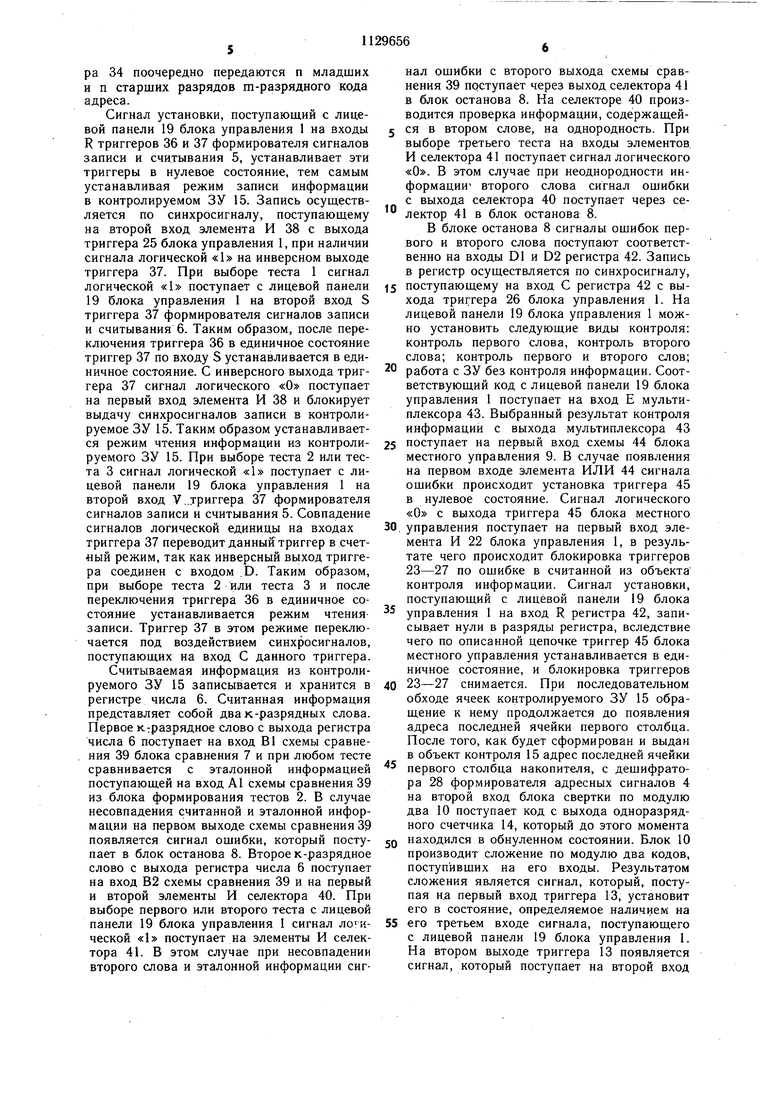

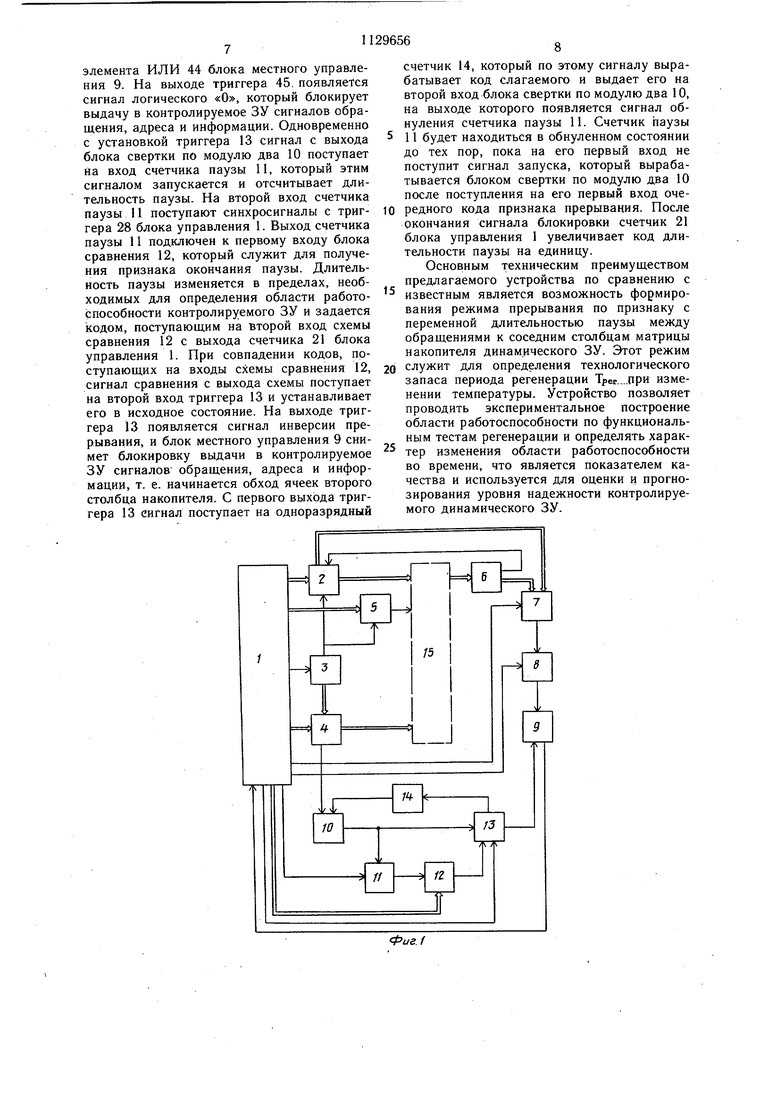

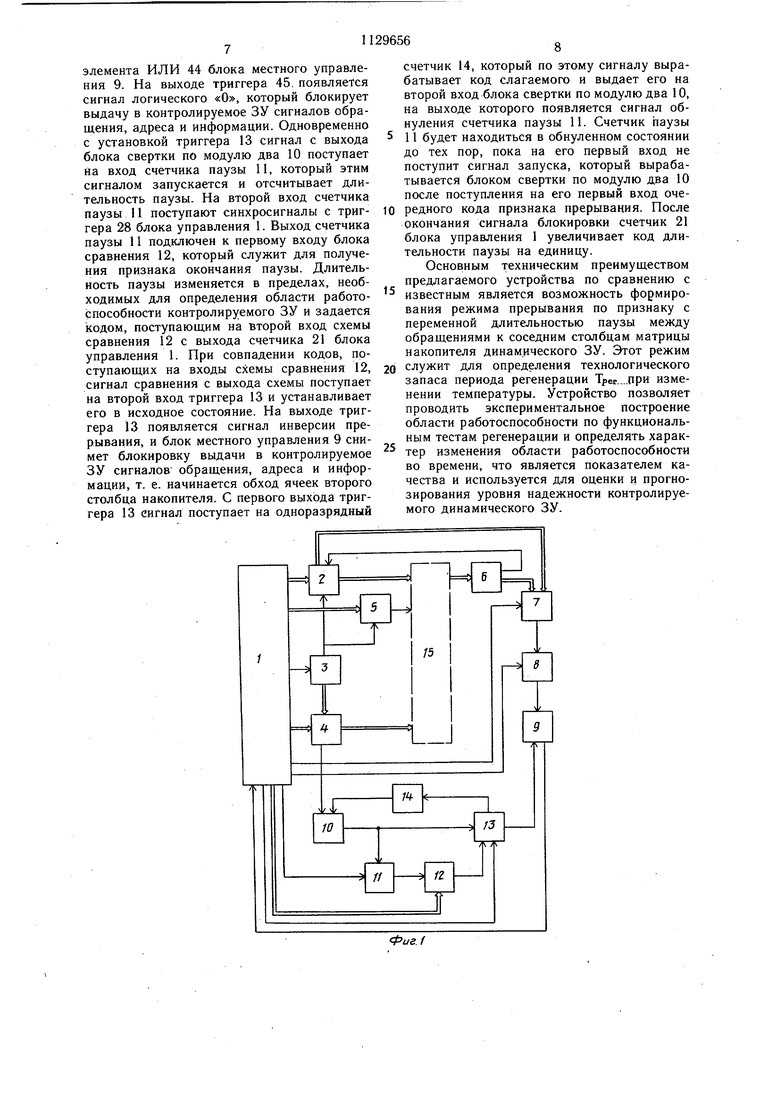

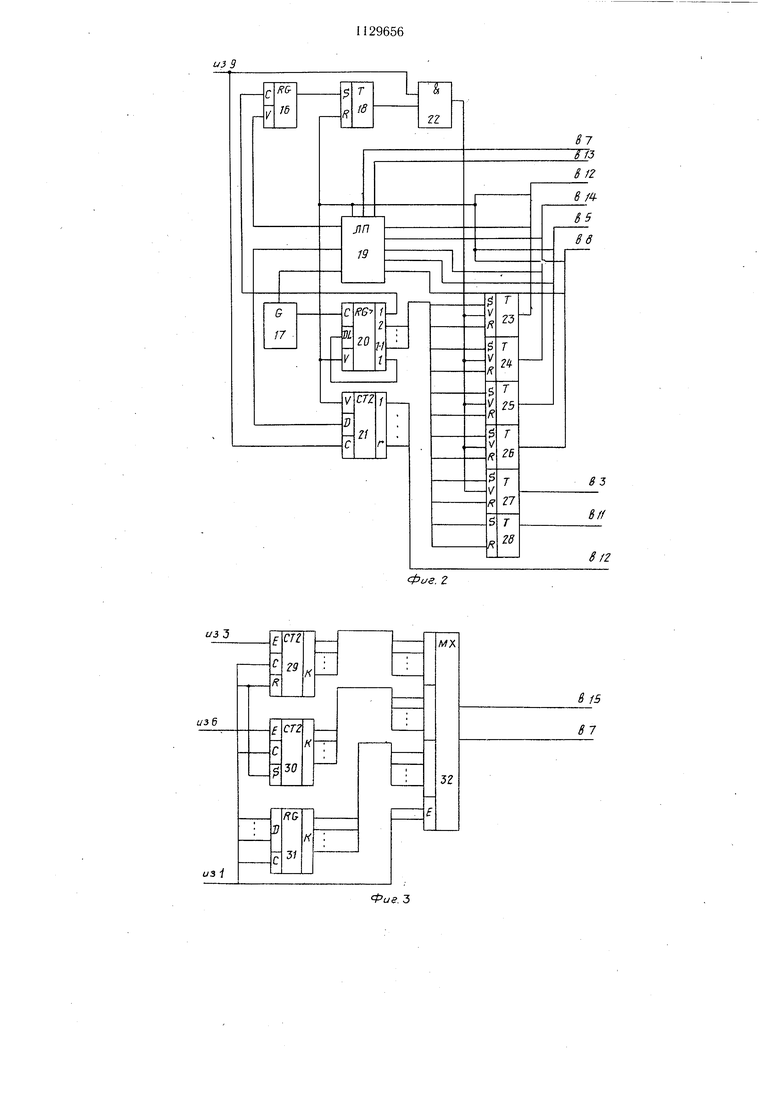

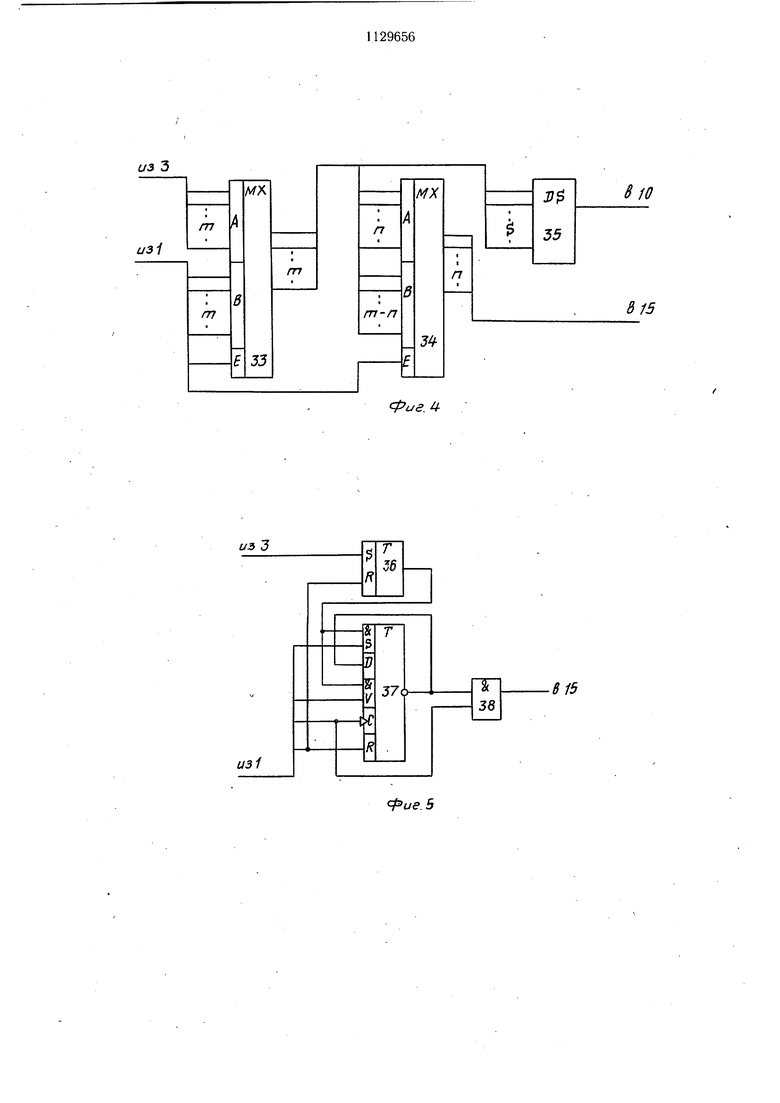

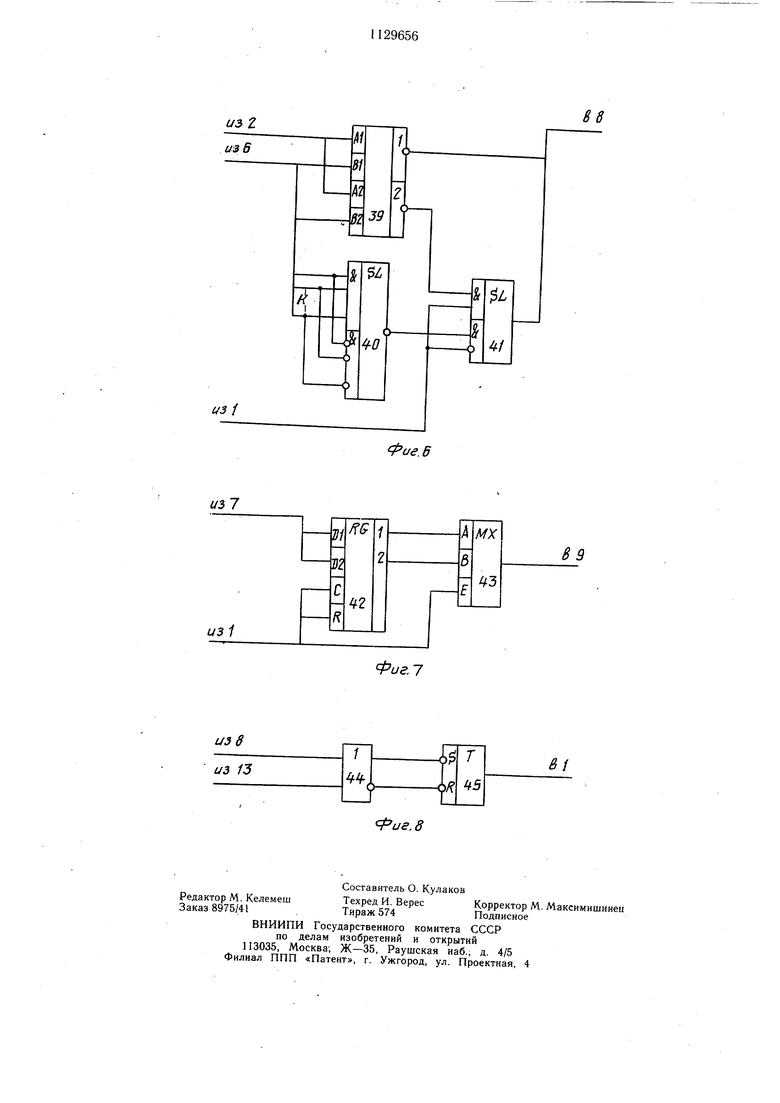

На фиг. 1 изображена структурная схема предложенного устройства для контроля памяти; на фиг. 2 - функциональная схема блока управления; на фиг. 3 - то же, формирователя тестовых сигналов; на фиг. 4 - то же, формирователя адресных сигналов; на фиг. 5 - то же, формирователя сигналов записи и считывания; на фиг. 6 - то же, блока сравнения; на фиг. 7 - то же, блока останова; на фиг. 8 - то же, блока местного управления.

Устройство для контроля памяти (фиг. 1) содержит блок управления 1, формирователь тестовых сигналов 2, первый счетчик 3, формирователь адресных сигналов 4, формирователь сигналовзаписи и считывания 5, регистр числа б, блок сравнения 7, блок останова 8, блок местного управления 9, блок свертки по модулю два 10, второй счетчик 11, дополнительный блок сравнения 12, триггер 13, третий счетчик 14.

Вход и выходы устройства контроля подключены к контролируемому ЗУ 15.

Блок управления 1 (фиг. 2) состоит из регистра сдвига 16, генератора 17, триггера 18, лицевой панели 19, регистра сдвига 2D, счетчика 21, элемента И 22, триггеров 23-28.

Формирователь тестовых сигналов 2 (фиг. 3) состоит из счетчиков 29 и 30, регистра 31 и мультиплексора 32.

Формирователь адресных сигналов 4 (фиг. 4) состоит из мультиплексоров 33, 34 и дешифратора 35.

Формирователь сигналов записи и считывания 5 (фиг. 5) состоит из триггеров 36, 37 и элемента И 38.

Блок сравнения 7 (фиг. 6) состоит из схемы сравнения 39, селектора 40 и селектора 41.

Блок останова 8 (фиг. 7) состоит из регистра 42 и мультиплексора 43.

Блок местного управления 9 (фиг. 8) состоит из элемента ИЛИ 44 и триггера 45.

Устройство работает следующим образом.

Генератор 17 блока управления 1 запускается одновременно с включением электропитания на лицевой панели управления 19. Опорная частота с генератора 17 поступает на сдвиговый регистр 20. При поступлении установочного сигнала- с лицевой панели управления 19 на вход регистра 20 в нем осуществляется запись начального кода, т. е. запись единицы в первый разряд и нулей во все остальные разряды. По окончании установочного сигнала под воздействием опорной частоты с генератора 17 в регистре 20 осуществляется постоянный циклический сдвиг единицы в сторону старщего разряда. Таким образом на выходах сдвигового регистра 20 появляются последовательности сдвинутых относительно друг друга синхроимпульсов. Синхроимпульсы с первого выхода регистра 20 поступают на синхровход сдвигового регистра 16, который осуществляет сдвиг единицы в сторону старщих разрядов при появлении на его управляющем входе сигнала с лицевой панели управления 19. С появлением единицы на определенном выходе регистра 16 производится установка триггера 18 в единичное состояние. Сигнал с выхода триггера 18 через элемент И 22 поступает на управляющие входы триггеров 23-28. На выходах последних появляются синхросигналы, дли0 тельность и время появления которых определяются последовательностью синхросигналов, поступающих на установочные входы этих триггеров с выходов сдвигового регистра 20.

Работа триггеров может блокироваться сигналом, поступающим из блока местного управления 9 на второй вход элемента И 22. Код выбранного теста с лицевой панели 19 блока управления 1 поступает в формирователь тестовых сигналов 2 на управ0 ляющие входы мультиплексора 32, с выхода которого информация поступает на запись в объект контроля 15 и на сравнение в блок сравнения 7. Работа счетчиков 29 и 30 и запись в регистр 31 осуществляется под

5 воздействием синхросигналов, поступающих с выхода триггера 23 блока управления 1 на входы счетчиков 29, 30 и регистра 31. Данные для записи в регистр 31 задаются на лицевой панели 19 блока управления 1. На.выход Е счетчика 29 поступает Сигнал

0 переноса с второго выхода счетчика адреса 3. а на вход Е счетчика 30 поступает разряд информации с второго выхода регистра числа 6. Сигнал установки с лицевой панели 19 блока управления 1 поступает на вход R счетчика 29, устанавливая его в нулевое

состояние, и на вход S счетчика 30, устанавливая его в единичное состояние.

Счетчик адреса 3 под воздействием синхросигналов с выхода триггера 27 блока управления 1 осуществляет перебор адресов

0 контролируемого ЗУ 15. С первого выхода счетчика 3 т-разрядный код адреса поступает на группу входов А мультип.тексора 33 формирователя адресных сигналов 4. На группу входов В мультиплексора 33 поступает код адреса контролируемого ЗУ, устанавливаемый на лицевой панели управления 19 блока управления 1. Выбор группы А или В осуществляется сигналом управления, поступающим на вход Е мультиплексора 33 с лицевой панели 19 блока управQ ления 1. С выхода мультиплексора 33 п разрядов кода адреса поступает на группу входов А мультиплексора 34, а гп-п разрядов кода адреса поступает на группу входов В мультиплексора 34. Причем 2п т. В зависимости от состояния синхросигнала, посту5 пающего на вход Е мультиплексора 34 с выхода триггера 24 блока управления 1, в течение одного цикла обращения в контролируемое ЗУ 15 с выхода мультиплексоpa 34 поочередно передаются n младших и n старших разрядов т-разрядного кода адреса.

Сигнал установки, поступаюший с лицевой панели 19 блока управления 1 на входы R триггеров 36 и 37 формирователя сигналов записи и считывания 5, устанавливает эти триггеры в нулевое состояние, тем самым устанавливая режим записи информации в контролируемом ЗУ 15. Запись осуществляется по синхросигналу, поступающему на второй вход элемента И 38 с выхода триггера 25 блока управления 1, при наличии сигнала логической «1 на инверсном выходе триггера 37. При выборе теста 1 сигнал логической «1 поступает с лицевой панели 19 блока управления 1 на второй вход S триггера 37 формирователя сигналов записи и считывания 6. Таким образом, после переключения триггера 36 в единичное состояние триггер 37 по входу S устанавливается в единичное состояние. С инверсного выхода триггера 37 сигнал логического «О поступает на первый вход элемента И 38 и блокирует выдачу синхросигналов записи в контролируемое ЗУ 15. Таким образом устанавливается режим чтения информации из контролируемого ЗУ 15. При выборе теста 2 или теста 3 сигнал логической «1 поступает с лицевой панели 19 блока управления 1 на второй вход V..триггера 37 формирователя сигналов записи и считывания 5. Совпадение сигналов логической единицы на входах триггера 37 переводит данный триггер в счетный режим, так как инверсный выход триггера соединен с входом .D. Таким образом, при выборе теста 2 или теста 3 и после переключения триггера 36 в единичное состояние устанавливается режим чтениязаписи. Триггер 37 в этом режиме переключается под воздействием синхросигналов, поступающих на вход С данного триггера. Считываемая информация из контролируемого ЗУ 15 записывается и хранится в регистре числа 6. Считанная информация представляет собой двак-разрядных слова. Первое кфазрядное слово с выхода регистра числа 6 поступает на вход В1 схемы сравнения 39 блока сравнения 7 и при любом тесте сравнивается с эталонной информацией поступающей на вход А1 схемы сравнения 39 из блока формирования тестов 2. В случае несовпадения считанной и эталонной информации на первом выходе схемы сравнения 39 появляется сигнал ошибки, который поступает в блок останова 8. Второе к-разрядное слово с выхода регистра числа 6 поступает на вход В2 схемы сравнения 39 и на первый и второй элементы И селектора 40. При выборе первого или второго теста с лицевой панели 19 блока управления I сигнал ло нческой «1 поступает на элементы И селектора 41. В этом случае при несовпадении второго слова и эталонной информации сигнал ощибки с второго выхода схемы сравнения 39 поступает через выход селектора 41 в блок останова 8. На селекторе 40 производится проверка информации, содержащейся в втором слове, на однородность. При выборе третьего теста на входы элементов. И селектора 41 поступает сигнал логического «О. В этом случае при неоднородности информации второго слова сигнал ошибки с выхода селектора 40 поступает через селектор 41 в блок останова 8.

В блоке останова 8 сигналы ошибок первого и второго слова поступают соответственно на входы D1 и D2 регистра 42. Запись в регистр осуществляется по синхросигналу,

5 поступающему на вход С регистра 42 с выхода триггера 26 блока управления 1. На лицевой панели 19 блока управления 1 можно установить следующие виды контроля: контроль первого слова, контроль второго слова; контроль первого и второго слов;

работа с ЗУ без контроля информации. Соответствующий код с лицевой панели 19 блока управления 1 поступает на вход Е мультиплексора 43. Выбранный результат контроля информации с выхода мультиплексора 43

5 поступает на первый вход схемы 44 блока местного управления 9. В случае появления на первом входе элемента ИЛИ 44 сигнала ощибки происходит установка триггера 45 в нулевое состояние. Сигнал логического «О с выхода триггера 45 блока местного

0, управления поступает на первый вход элемента И 22 блока управления 1, в результате чего происходит блокировка триггеров 23-27 по ошибке в считанной из объекта контроля информации. Сигнал установки, поступающий с лицевой панели 19 блока

управления 1 на вход R регистра 42, записывает нули в разряды регистра, вследствие чего по описанной цепочке триггер 45 блока местного управления устанавливается в единичное состояние, и блокировка триггеров

0 23-27 снимается. При последовательном обходе ячеек контролируемого ЗУ 15 обращение к нему продолжается до появления адреса последней ячейки первого столбца. После того, как будет сформирован и выдан в объект контроля 15 адрес последней ячейки

первого столбца накопителя, с дешифратора 28 формирователя адресных сигналов 4 на второй вход блока свертки по модулю два 10 поступает код с выхода одноразрядного счетчика 14, который до этого момента

0 находился в обнуленном состоянии. Блок 10 производит сложение по модулю два кодов, поступивших на его входы. Результатом сложения является сигнал, который, поступая н.а первый вход триггера 13, установит его в состояние, определяемое наличием на

5 его третьем входе сигнала, поступающего с лицевой панели 19 блока управления 1. На втором выходе триггера 13 появляется сигнал, который поступает на второй вход

элемента ИЛИ 44 блока местного управления 9. На выходе триггера 45. появляется сигнал логического «О, который блокирует выдачу в контролируемое ЗУ сигналов обращения, адреса и информации. Одновременно с установкой триггера 13 сигнал с выхода блока свертки по модулю два 10 поступает на вход счетчика паузы 11, который этим сигналом запускается и отсчитывает длительность паузы. На второй вход счетчика паузы 11 поступают синхросигналы с триггера 28 блока управления 1. Выход счетчика паузы 11 подключен к первому входу блока сравнения 12, который служит для получения признака окончания паузы. Длительность паузы изменяется в пределах, необходимых для определения области работоспособности контролируемого ЗУ и задается кодом, поступающим на второй вход схемы сравнения 12 с выхода счетчика 21 блока управления 1. При совпадении кодов, поступающих на входы схемы сравнения 12, сигнал сравнения с выхода схемы поступает на второй вход триггера 13 и устанавливает его в исходное состояние. На выходе триггера 13 появляется сигнал инверсии прерывания, и блок местного управления 9 снимет блокировку выдачи в контролируемое ЗУ сигналов обращения, адреса и информации, т. е. начинается обход ячеек второго столбца накопителя. С первого выхода триггера 13 сигнал поступает на одноразрядный

счетчик 14, который по этому сигналу вырабатывает код слагаемого и выдает его на второй вход блока свертки по модулю два 10, на выходе которого появляется сигнал обнуления счетчика паузы 11. Счетчик паузы 5 11 будет находиться в обнуленном состоянии до тех пор, пока на его первый вход не поступит сигнал запуска, который вырабатывается блоком свертки по модулю два 10 после поступления на его первый вход оче0 редного кода признака прерывания. После окончания сигнала блокировки счетчик 21 блока управления 1 увеличивает код длительности паузы на единицу.

Основным техническим преимуществом предлагаемого устройства по сравнению с

известным является возможность формирования режима прерывания по признаку с переменной длительностью паузы между обращениями к соседним столбцам матрицы накопителя динамического ЗУ. Этот режим

0 служит для определения технологического запаса периода регенерации Трес....при изменении температуры. Устройство позволяет проводить экспериментальное построение области работоспособности по функциональным тестам регенерации и определять характер изменения области работоспособности во времени, что является показателем качества и используется для оценки и прогнозирования уровня надежности контролируемого динамического ЗУ.

Фие. г

. 4

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для контроля блоков памяти | 1981 |

|

SU970481A1 |

| Устройство для контроля и диагностирования электронных узлов | 1985 |

|

SU1415211A1 |

| Устройство для контроля оперативной памяти | 1981 |

|

SU980166A1 |

| Устройство для контроля оперативной памяти | 1981 |

|

SU1010660A1 |

| Устройство для обучения | 1987 |

|

SU1559366A1 |

| Устройство для контроля блоков оперативной памяти | 1981 |

|

SU957278A1 |

| Устройство для контроля памяти | 1985 |

|

SU1316052A1 |

| Динамическое оперативное запоминающее устройство | 1981 |

|

SU1003142A1 |

| Устройство для сопряжения цифровой вычислительной машины (ЦВМ) с абонентами | 1984 |

|

SU1234843A1 |

| Устройство для диагностирования периферийных устройств | 1990 |

|

SU1716518A1 |

УСТРОЙСТВО ДЛЯ КОНТРОЛЯ ПАМЯТИ, содержащее блок управления, формирователь тестовых сигналов, формирователь адресных сигналов, формирователь сигналов записи и считывания, регистр числа, блок сравнения, блок останова, блок местного управления, первый счетчик, причем первый, второй, третий, четвертый, пятый и шестой выходы блока управления подключены соответственно к первым входам формирователя тестовых сигналов, формирователя сигналов записи и считывания, первого счетчика, формирователя адресных сигналов блока сравнения и блока останова, вход. блока управления подключен к выходу блока местного управления, первый выход формирователя тестовых сигналов подключен к второму входу блока сравнения, третий вход и выход которого соединены соответственно с первым выходом регистра числа и вторым входом блока останова, выход которого подключен к первому входу блока местного управления, первый выход первого счетчика соединен с вторым входом формирователя адресных сигналов, а второй выход первого счетчика подключен к вторым входам формирователя тестовых сигналов и формирователя сигналов записи и считывания, третий вход формирователя тестовых сигналов соединен с вторым выходом регистра числа, вход которого является входом устройства, второй выход формирователя тестовых сигналов, выход формирователя сигналов записи и считывания и первый выход формирователя адресных сигналов являются выходами устройства, отличающееся тем, что, с целью расширения области применения за счет формирования режима прерывания для определения области работоспособности контролируемой памяти, оно содержит блок 8 $ свертки по модулю два, второй и третий (Л счетчики, блок сравнения, триггер, причем второй выход формирователя адресных сигналов соединен с первым входом блока свертки по модулю два, второй вход которого подключен к выходу третьего счетчика, вход которого соединен с первым выходом триггера, второй выход которого подключен к второму входу блока местного управления, выход блока свертки по модулю два подключен к первым входам триггера и второго счетчиto ка, выход которого соединен с первым выхосо дом блока сравнения, выход которого подО5 ключен к второму входу триггера, вторые входы второго счетчика и блока сравнения СП и. третий вход триггера соединены соответст05 венно с седьмым, восьмым и девятым выходами блока управления.

иъ 3

ue.5

иэ I

из1

Фие.В

Фиг.7

Bi

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Устройство для контроля памяти | 1977 |

|

SU739658A1 |

| Походная разборная печь для варки пищи и печения хлеба | 1920 |

|

SU11A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Устройство для контроля памяти | 1978 |

|

SU752499A1 |

| Походная разборная печь для варки пищи и печения хлеба | 1920 |

|

SU11A1 |

Авторы

Даты

1984-12-15—Публикация

1983-08-16—Подача