tc

о

со со

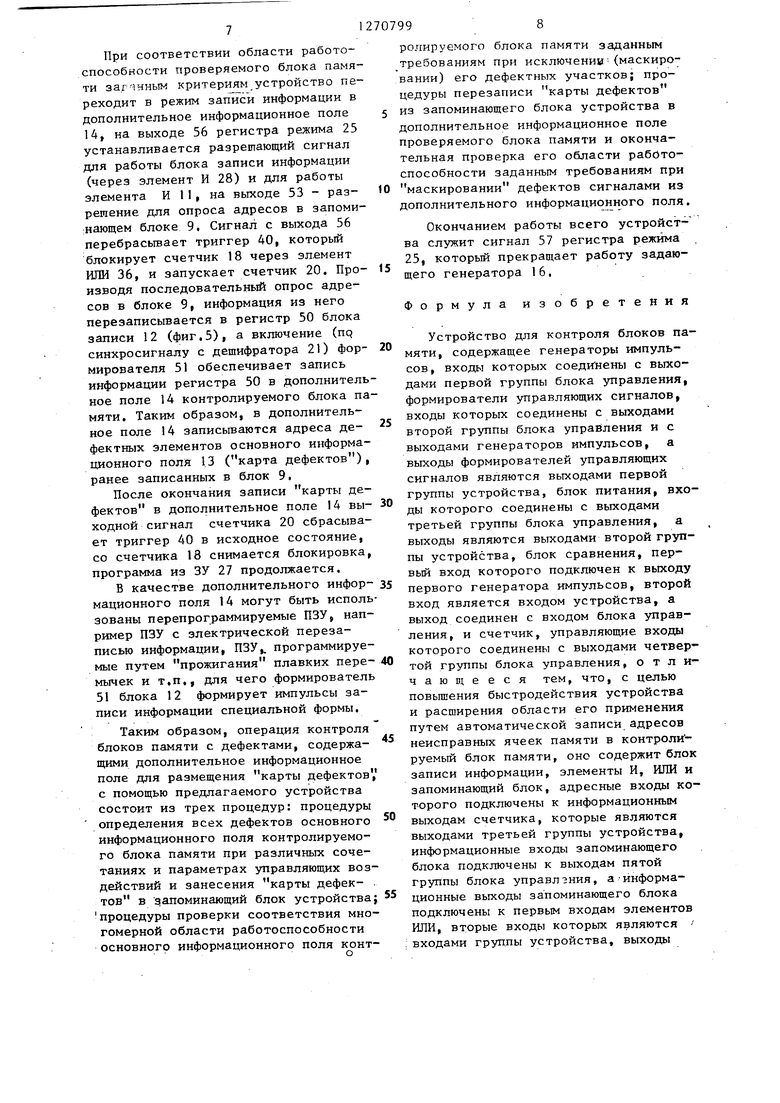

Изобретение относится к вычислительной технике и может быть использовано для контроля запоминающих устроств(полупроводниковых ЗУ, ферритовых ЗУ, доменных ЗУ и Ap.)t

Цель изобретения - повышение быстродействия устройства и распшрение области его применения путем автоматической записи адресов неисправных ячеек памяти в контролируемы){1 блок памяти.

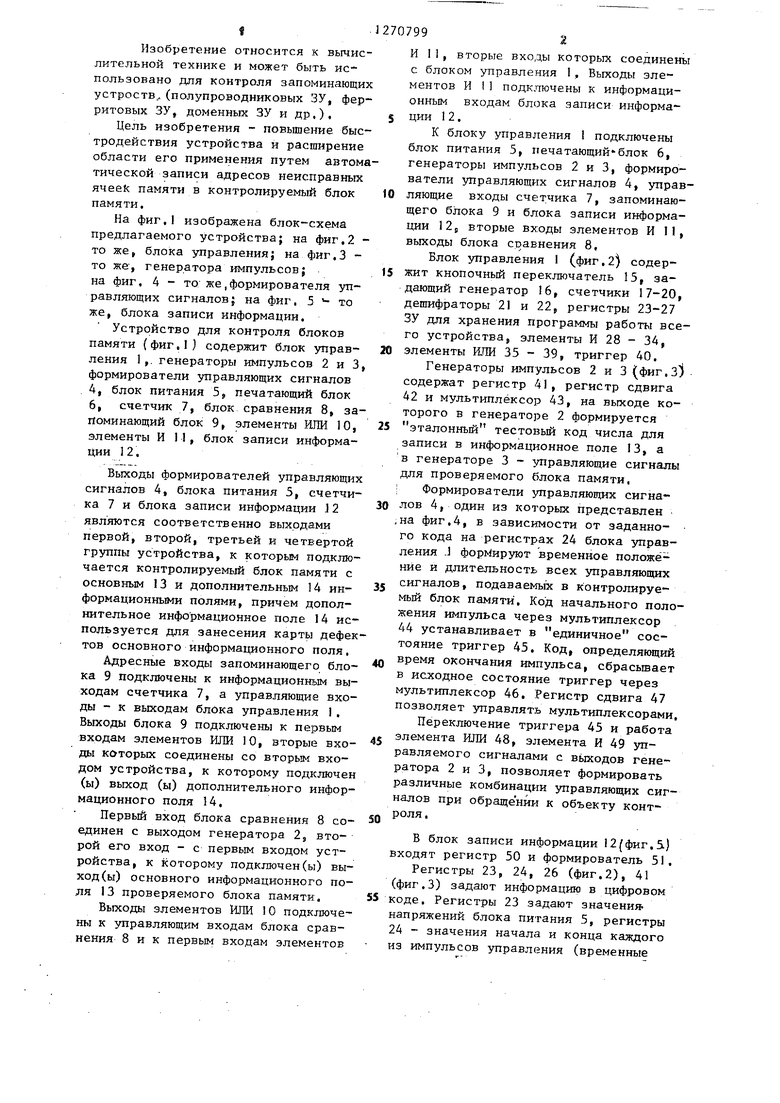

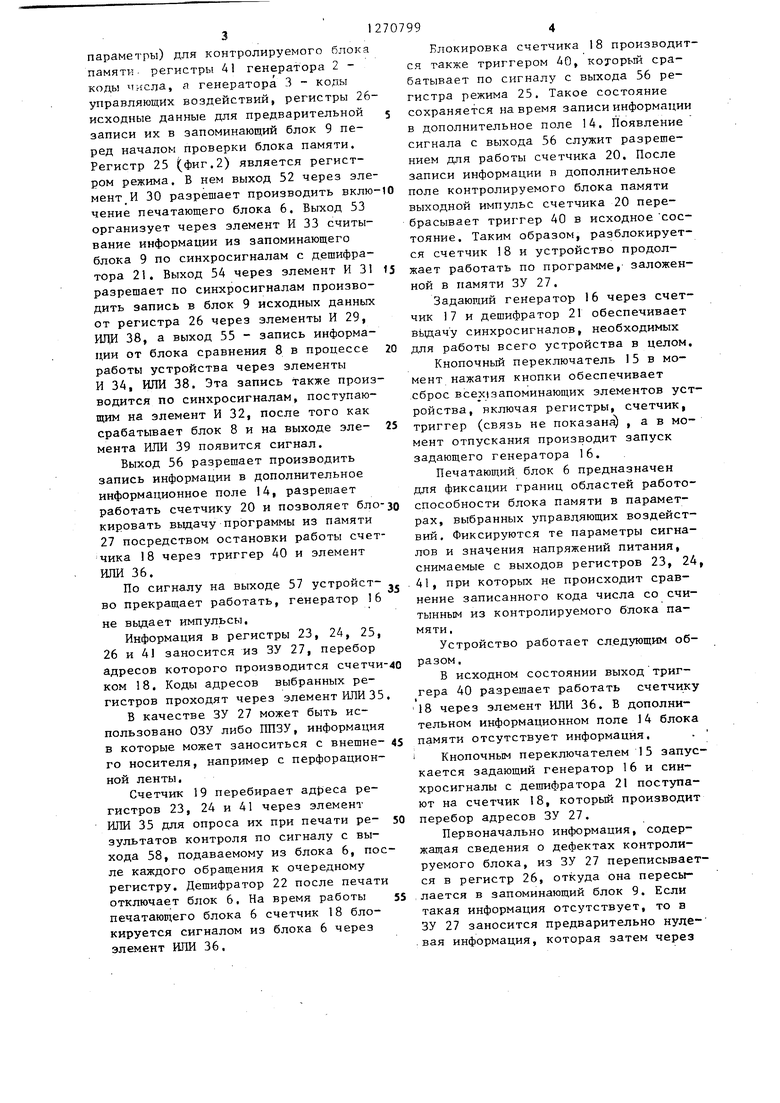

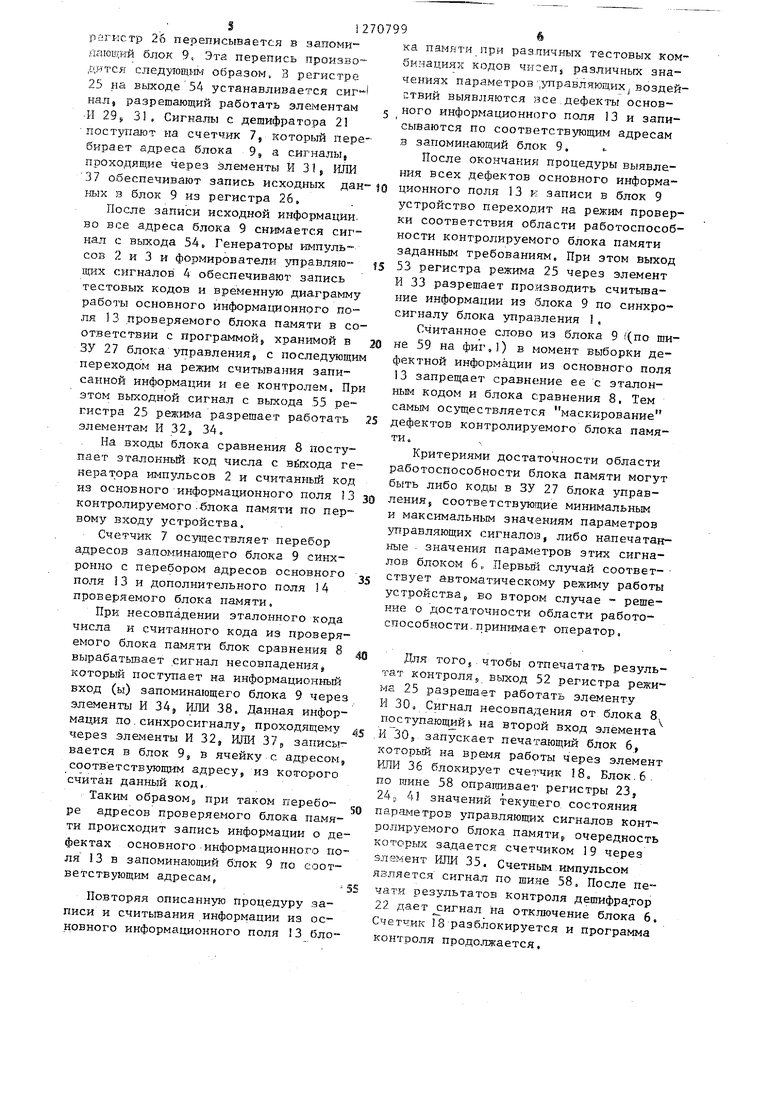

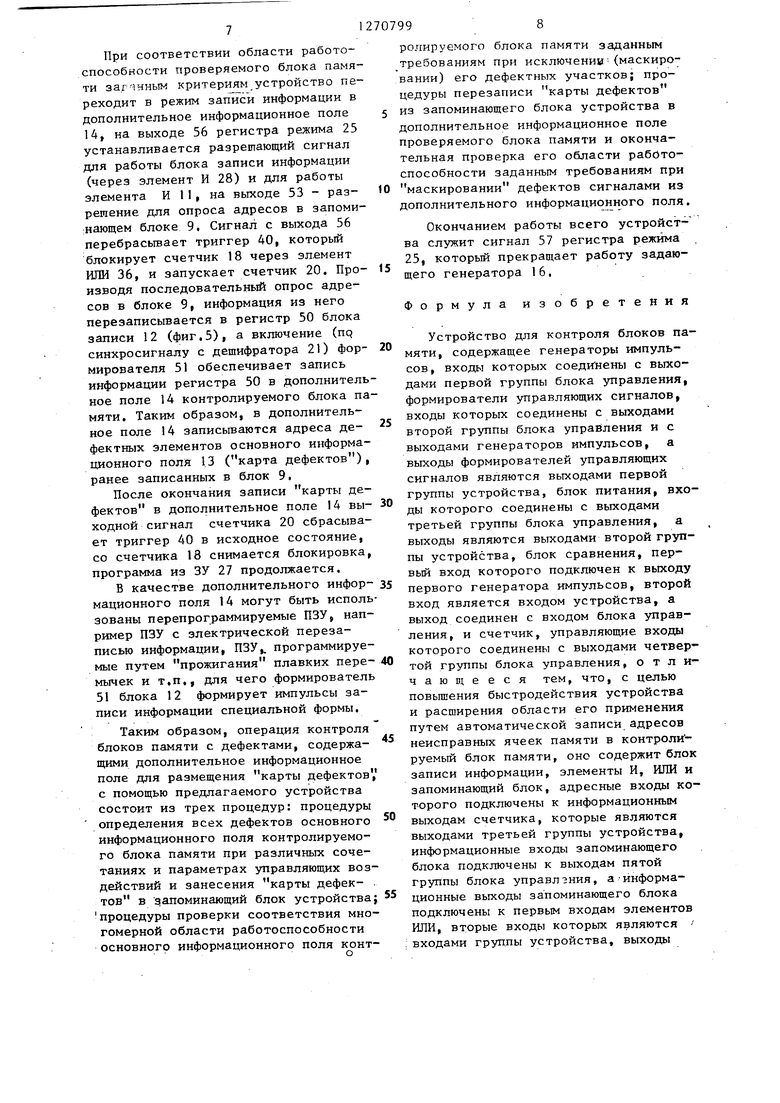

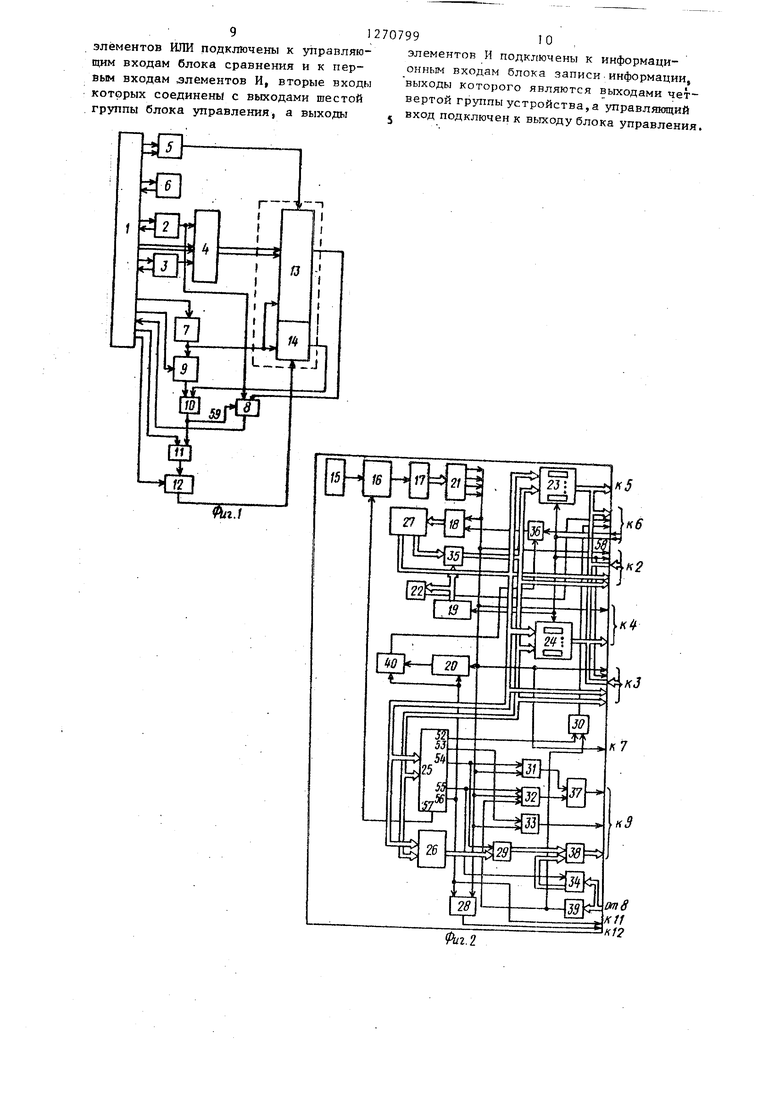

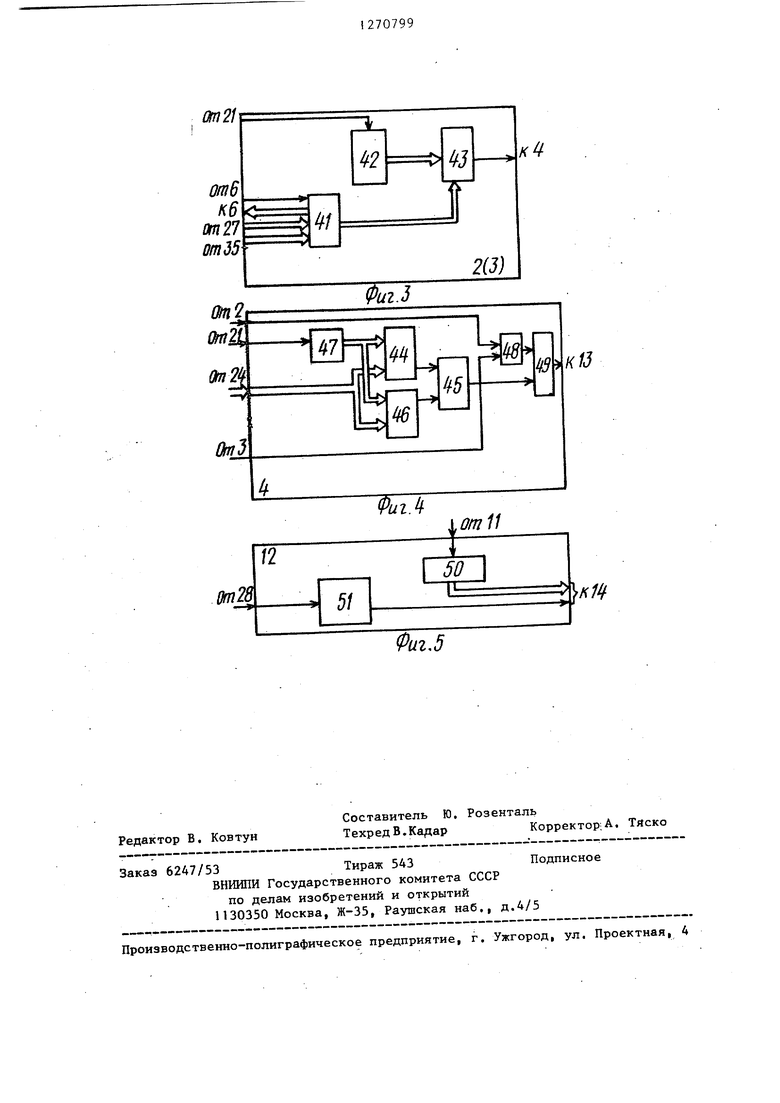

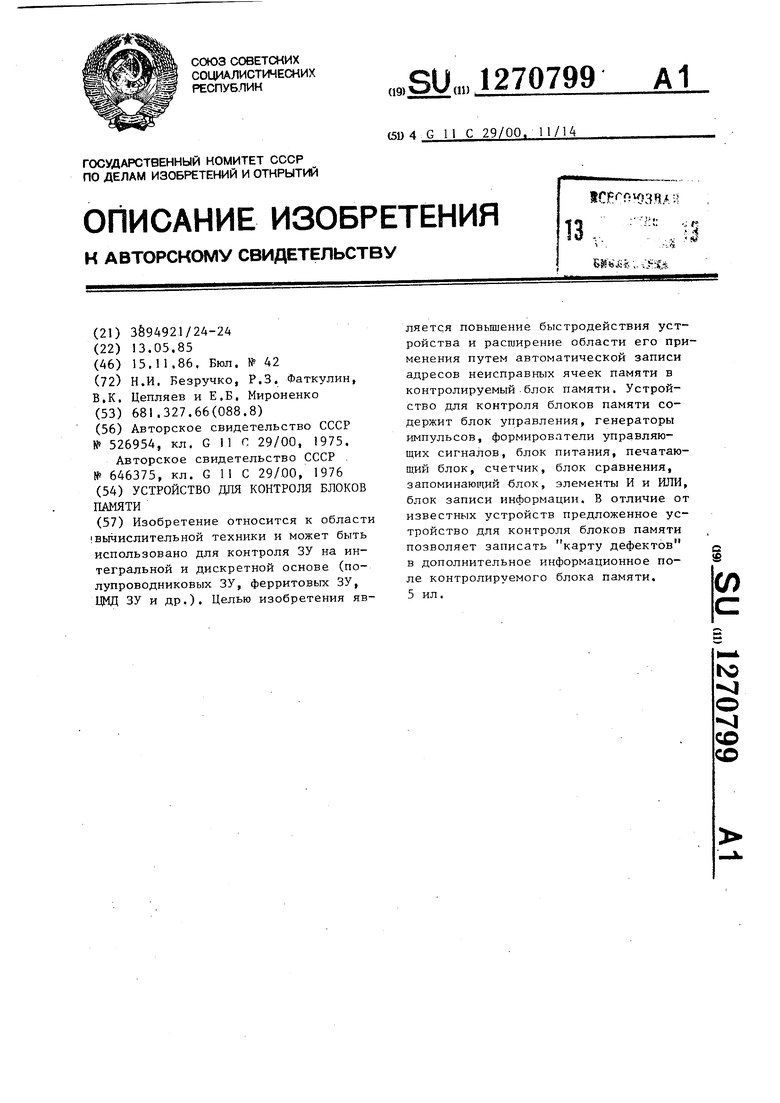

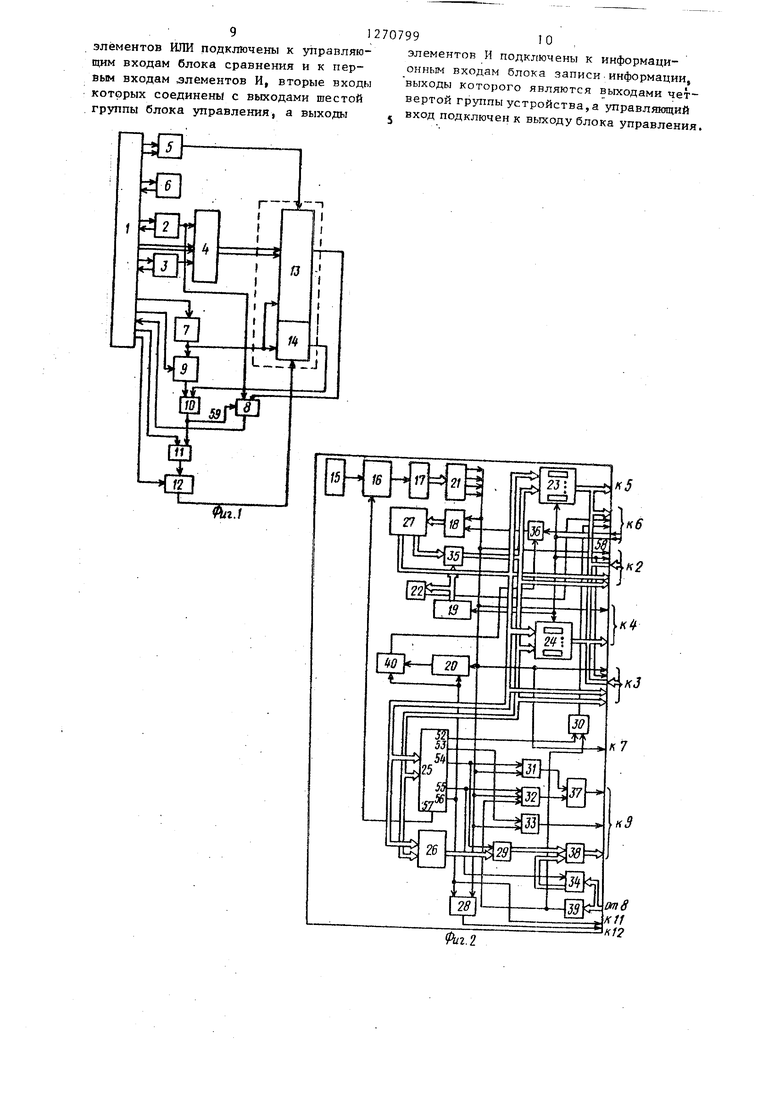

На фиг,1 изображена блок-схема предлагаемого устройства; на фиг,2 то же, блока управления; на фиг,3 то же, генератора импульсов; на фиг, 4 - то же,формирователя управляющих сигналов; на фиг, 5 - то же, блока записи информации.

Устройство для контроля блоков памяти (фиг,1} содержит блок управления 1,. генераторы импульсов 2 и 3 формирователи управляющих сигналов 4, блок питания 5, печатающий блок 6, счетчик 7, блок сравнения 8, запоминающий блок 9, элементы ИЛИ 1 О, элементы И 11, блок записи информации 12,

Выходы формирователей управляющих сигналов 4, блока питания 5, счетчика 7 и блока записи информации J 2 являются соответственно выходами первой, второй, третьей и четвертой группы устройства, к которым подключается контролируемый блок памяти с основным 13 и дополнительным 14 информационными полями, причем дополнительное информационное поле I4 используется для занесения карты дефектов основного информационного поля.

Адресные входы запоминающего блока 9 подключены к информационным выходам счетчика 7, а управляющие входы - к выходам блока управления 1, Выходы блока 9 подключены к первым входам элементов ИЛИ 10, вторые входы которых соединены со вторым входом устройства, к которому подключен (ы) выход (ы) дополнительного информационного поля 14,

Первый вход блока сравнения 8 соединен с выходом генератора 2, второй его вход - с первым входом устройства, к которому подключен(ы) выход (ы) основного информационного поля 13 проверяемого блока памяти,

Выходы элементов ИЛИ 10 подключены к управляющим входам блока сравнения 8 и к первым входам элементов

И I1, вторые входы которых соединены с блоком управления 1, Выходы элементов И I1 подключены к информационным входам блока записи информации 12,

К блоку управления 1 подключены блок питания 5, печатающий блок 6, генераторы импульсов 2 и 3, формирователи управляющих сигналов 4, управляющие входы счетчика 7, запоминающего бЛока 9 и блока записи информации 125 вторые входы элементов И П, выходы блока сравнения 8,

Блок управления I (фиг,2) содержит кнопочный переключатель 15, задающий генератор 16, счетчики 17-20, депшфраторы 21 и 22, регистры 23-27 ЗУ для хранения программы работы всего устройства, элементы И 28 - 34,

элементы ИЛИ 35 - 39, триггер 40,

Генераторы импульсов 2 и 3 (фиг,3) содержат регистр 41, регистр сдвига 42 и мультиплексор 43, на выходе которого в генераторе 2 формируется

эталонньй тестовый код числа для записи в информационное поле 13, а в генераторе 3 - управляющие сигналы для проверяемого блока памяти, : Формирователи управляющих сигналов 4, один из которых представлен ,на фиг,4, в зависимости от заданно- го кода на регистрах 24 блока управления .1 формируют временное положение и длительность всех управляющих

сигналов, подаваемых в контролируемый блок памяти. Код начального положения импульса через мультиплексор 44 устанавливает в единичное состояние триггер 45, Код, определяющий

время окончания импульса, сбрасьгоает в исходное состояние триггер через мультиплексор 46, Регистр сдвига 47 позволяет управлять мультиплексорами. Переключение триггера 45 и работа

элемента ШШ 48, элемента И 49 3 1равляемого сигналами с вьпсодов генератора 2 и 3, позволяет формировать различные комбинации управляющих сигналов при обращении к объекту контроля,

в блок записи информации ,5) входят регистр 50 и формирователь 51,

Регистры 23, 24, 26 (фиг,2), 41 (фиг,3) задают информацию в цифровом коде. Регистры 23 задают значениянапряжений блока питания 5, регистры 24 - значения начала и конца каждого из импульсов управления (временные 31 параметры) для контролируемого блока памяти, регистрь 41 генератора 2 коды мисла, а генератора 3 - коды управляющих воздействий, регистры 26исходные данные для предварительной записи их в запоминающий блок 9 перед началом проверки блока памяти. Регистр 25 (фиг.2) является регистром режима. В нем выход 52 через элемент И 30 разрешает производить вклю-Ю чение печатающего блока 6. Выход 53 организует через элемент И 33 считывание информации из запоминающего блока 9 по синхросигналам с дешифратора 21. Выход 54 через элемент И 31 разрешает по синхросигналам производить запись в блок 9 исходных данных от регистра 26 через элементы И 29, ИДИ 38, а выход 55 - запись информации от блока сравнения 8 в процессе работы устройства через элементы И 34, ИЖ 38. Эта запись также произ водится по синхросигналам, поступающим на элемент И 32, после того как срабатывает блок 8 и на выходе элемента ИЛИ 39 появится сигнал. Выход 56 разрешает производить запись информации в дополнительное информационное поле 14, разрешает работать счетчику 20 и позволяет бло-зо кировать вьщачу программы из памяти 27 посредством остановки работы счетчика 8 через триггер 40 и элемент ИЛИ 36. По сигналу на выходе 57 устройство прекращает работать, генератор 16 не вьщает импульсы. Информация в регистры 23, 24, 25, 26 и 41 заносится из ЗУ 27, перебор адресов которого производится счетчиком 18. Коды адресов выбранных регистров проходят через элемент ИЛИ 35 В качестве ЗУ 27 может быть использовано ОЗУ либо ПИЗУ, информация в которые может заноситься с внешне го носителя, например с перфорацион ной ленты. Счетчик 19 перебирает адреса регистров 23, 24 и 41 через элемент ИЛИ 35 для опроса их при печати результатов контроля по сигналу с выхода 58, подаваемому из блока 6, по ле каждого обращения к очередному регистру. Дешифратор 22 после печат отключает блок 6. На время работы печатающего блока 6 счетчик 18 блокируется сигналом из блока 6 через элемент ШШ 36. 99 Блокировка счетчика 18 производится также триггером ДО, который срабатывает по сигналу с выхода 56 регистра режима 25. Такое состояние сохраняется на время записи информации в дополнительное поле 14. Появление сигнала с выхода 56 служит разрешением для работы счетчика 20, После записи информации в дополнительное поле контролируемого блока памяти выходной импульс счетчика 20 перебрасывает триггер 40 в исходное состояние. Таким образом, разблокируется счетчик 18 и устройство продолжает работать по программе, заложенной в памяти ЗУ 27. Задающий генератор 16 через счетчик 17 и дешифратор 21 обеспечивает вьщачу синхросигналов, необходимых для работы всего устройства в целом. Кнопочный переключатель 15 в момент нажатия кнопки обеспечивает сброс всех)запоминающих элементов устройства, включая регистры, счетчик, триггер (связь не показан; , а в момент отпускания производит запуск задающего генератора 16. Печатающий блок 6 предназначен для фиксации границ областей работоспособности блока памяти в параметpax, выбранных управляющих воздействий. Фиксируются те параметры сигналов и значения напряжений питания, снимаемые с выходов регистров 23, 24, 41, при которых не происходит сравнение записанного кода числа со считынным из контролируемого блока памяти , Устройство работает следующим образом. В исходном состоянии выход триггера 40 разрешает работать счетчику 18 через элемент ИЛИ 36. В дополнительном информационном поле 14 блока памяти отсутствует информация. Кнопочным переключателем 15 запускается задающий генератор 16 и синхросигналы с дешифратора 21 поступают на счетчик 18, который производит перебор адресов ЗУ 27. Первоначально информация, содержащая сведения о дефектах контролируемого блока, из ЗУ 27 переписывается в регистр 26, откуда она пересылается в запоминающий блок 9. Если такая информация отсутствует, то в ЗУ 27 заносится предварительно нулевая информация, которая затем через рагистр 26 переписывается в запоми пающий блок 9, Эта перепись произво,г1ится следутощ -1М образом, 3 регистре 25 на выходе 54 устанавливается сиг нал, разрешающий работать элементам 41 29, 31. Сигналы с дешифратора 2 поступают на счетчик 7, который пере бирает адреса блока 9 а сигналы, проходящие через элементы И 31, ИЛИ 37 обеспечивают запись исходных дан ных в блок 9 из регистра 26, После записи исходной информации, во все адреса блока 9 снимается сигнал с выхода 54,, Генераторы импульсов 2 и 3 и формирователи управляющих сигналов 4 обеспечивают запись тестовых кодов и временную диаграмму работы основного информационного поля 13 проверяемого блока памяти в со ответствии с программой, хранимой в ЗУ 27 блока управления( с последующи переходом на режим считывания записанной информации и ее контролем, Пр этом вьгходной сигнал с выхода 55 ре гистра 25 режима разрешает работать элементам И 32, 34. На входы блока сравнения 8 поступает эталокньШ код числа с вьпсода ге нератора импульсов 2 и считанный код из основного информационного поля i3 контролируемого -блока памяти по первому входу устройства. Счетчик 7 осуществляет перебор адресов запоминающего блока 9 синхронно с перебором адресов основного поля 13 и дополнительного поля 14 проверяемого блока памяти При несовпадении эталонного кода числа и считанного кода из проверяемого блока памяти блок сравнения 8 вырабатьшает сигнал несовпадения, который поступает на. информационный вход (ы) запоминающего блока 9 через элементы И 34 ИЛИ 38. Данная информация по,синхросигналу, проходящему через элементы И 32, ИЛИ 37j записывается в блок 99 Б ячейку с адресом, соответствующим адресу, из которого считан данный код,. Таким образом, при таком переборе адресов проверяемого блока .памяти происходит запись информации о де фектах основного информационного по ля 3 в запоминающий блок 9 по соответствующим адресамf Повторяя описанную процедуру записи и считьшания информации из основного информационного поля 13 блока памяти при раз.пичных тестовых комбинациях кодов чиселд различных значениях параметров ,TIpaвл.я:ющиx воздействий выявляются все.дефекты основного информационного поля 13 и записываются по соответствующит- адресам в запоминающий блок 9, ь После окончания процедуры выявления всех дефектов основного информационного поля 13 и записи в блок 9 устройство переходит на режим проверки соответствия области работоспособности контролируемого блока памяти заданным требованиям. При этом выход 53 регистра режима 25 через элемент И 33 разрешает про.изводить считьшание информации из блока 9 по синхросигналу блока управления 1, Считанное слово из блока 9 (по шине 59 на фиг,1) в момент выборки дефектной информации из основного поля 13 запрещает сравнение ее с эталонньв4 кодом и блока сравнения 8, Тем самым осуществляется маскирование дефектов контролируемого блока памяти. Критериями достаточности области работоспособности блока памяти могут быть либо коды в ЗУ 27 блока управления соответствующие минимальным и максимальным значениям параметров управляющих сигналов, либо напечатанные - значения параметров этих сигналов блоком 6„ .Первый случай соответ- ствует автоматическому режиму работы устройства, во втором случае - решение о достаточности области работоспособности, прингдаает оператор. Для ТОГО; чтобы отпечатать результат контроля,, выход 52 регистра режима 25 разрещает работать элементу И 30, Сигнал несовпадения от блока 8 поступающей, на второй вход элемента И 30,, запускает печатающий блок 6, который на время работы через элемент ИЛИ 36 блокирует счетчик 18, Блок.6. по шине 58 опрагаивает регистры 23, 24р 41 значений текущего, состояния параметров управляющих сигналов конт ролнруемого блока памятИ;, очередность которых задается счетчиком 19 через элемент ИЛИ 35, Счетным.импульсом является сигнал по щи.не 58. После печати результатов контроля дещифра.тор 22 дает сигнал на отключение блока 6. Счетчик 18 разблокируется и программа контроля продолжается.

При соответствии области работоспособиости проверяемого блока памяти загтнным критериям устройство переходит в режим записи информации в дополнительное информационное поле 14, на выходе 56 регистра режима 25 устанавливается разрешающий сигнал для работы блока записи информации (через элемент И 28) и для работы элемента И 11, на выходе 53 - разрешение для опроса адресов в запоминающем блоке 9. Сигнал с выхода 56 перебрасьгоает триггер 40, который блокирует счетчик 18 через элемент ИЛИ 36, и запускает счетчик 20. Производя последовательный опрос адресов в блоке 9, информация из него перезаписывается в регистр 50 блока записи 12 (фиг.5), а включение (nq синхросигналу с дешифратора 21) формирователя 51 обеспечивает запись информации регистра 50 в дополнительное поле 14 контролируемого блока памяти. Таким образом, в дополнительное поле 14 записываются адреса дефектных элементов основного информационного поля 13 (карта дефектов), ранее записанных в блок 9,

После окончания записи карты дефектов в дополнительное поле 14 выходной сигнал счетчика 20 сбрасывает триггер 40 в исходное состояние, со счетчика 18 снимается блокировка, программа из ЗУ 27 продолжается.

В качестве дополнительного информационного поля 14 могут быть использованы перепрограммируемые ПЗУ, например ПЗУ с электрической перезаписью информации, ПЗУ,, программируемые путем прожигания плавких перемычек и т.п., для чего формирователь 51 блока 12 формирует импульсы записи информации специальной формы.

Таким образом, операция контроля блоков памяти с дефектами, содержащими дополнительное информационное поле для размещения карты дефектов, с помощью предлагаемого устройства состоит из трех процедур: процедуры определения всех дефектов основного информационного поля контролируемого блока памяти при различных сочетаниях и параметрах управляющих воздействий и занесения карты дефек- . тов в запоминающий блок устройства; процедуры проверки соответствия многомерной области работоспособности

основного информационного поля конт о

ролируемого блока памяти заданным требованиям при исключении (маскировании) его дефектных участков; процедуры перезаписи карты дефектов из запоминающего блока устройства в дополнительное информационное поле проверяемого блока памяти и окончательная проверка его области работоспособности заданным требованиям при маскировании дефектов сигналами из дополнительного информационного поля.

Окончанием работы всего устройства служит сигнал 57 регистра режима 25, который прекращает работу задающего генератора 16,

Формула изобретения

Устройство для контроля блоков памяти, содержащее генераторы импульсов , входы которых соединены с выходами первой группы блока управления, формирователи управляющих сигналов, входы которых соединены с выходами второй группы блока управления и с выходами генераторов импульсов, а выходы формирователей управляющих сигналов являются выходами первой группы устройства, блок питания, входы которого соединены с выходами третьей группы блока управления, а выходы являются выходами второй группы устройства, блок сравнения, первый вход которого подключен к выходу первого генератора импульсов, второй вход является входом устройства, а выход соединен с входом блока управления, и счетчик, управляющие входы которого соединены с выходами четвертой группы блока управления, отличающееся тем, что, с целью повьшения быстродействия устройства и расширения области его применения путем автоматической записи адресов неисправных ячеек памяти в контролируемый блок памяти, оно содержит блок записи информации, элементы И, ИЛИ и запоминающий блок, адресные входы которого подключены к информационным выходам счетчика, которые являются выходами третьей группы устройства, информационные входы запоминающего блока подключены к выходам пятой группы блока управлэния, а-информационные выходы запоминающего блока подключены к первым входам элементов ИЛИ, вторые входы которых являются входами группы устройства, выходы 1 элементов ШШ подключены к управляющим входам блока сравнения и к первым входам элементов И, вторые входы которых соединены с выходами шестой группы блока управления, а выходы 99 элементов И подключены к информационным входам блока записиинформации, выходы которого являются выходами четвертой группы устройства, а управляющий вход подключен к выходу блока управления,

Й/z.J

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство управления для доменной памяти | 1982 |

|

SU1152035A1 |

| Устройство для контроля памяти | 1983 |

|

SU1129656A1 |

| Запоминающее устройство | 1982 |

|

SU1084903A1 |

| Устройство для контроля интегральных микросхем памяти | 1983 |

|

SU1144154A1 |

| Запоминающее устройство с частичным резервированием | 1986 |

|

SU1434503A1 |

| Устройство для коррекции ошибок в блоках памяти с последовательным доступом | 1987 |

|

SU1510014A1 |

| Программируемый контроллер | 1981 |

|

SU1001012A1 |

| Запоминающее устройство | 1982 |

|

SU1295447A1 |

| Устройство для контроля цифровых узлов | 1985 |

|

SU1238085A2 |

| РАДИОЛОКАЦИОННАЯ СТАНЦИЯ | 1993 |

|

RU2037842C1 |

Изобретение относится к области вычислительной техники и может быть использовано для контроля ЗУ на интегральной и дискретной основе (полупроводниковых ЗУ, ферритовых ЗУ, ЩЦ ЗУ и др.). Целью изобретения является повьшение быстродействия устройства и расширение области его применения путем автоматической записи адресов неисправных ячеек памяти в контролируемый.блок памяти. Устройство для контроля блоков памяти содержит блок управления, генераторы импульсов, формирователи управляющих сигналов, блок питания, печатающий блок, счетчик, блок сравнения, запоминающий блок, элементы И и ИЛИ, блок записи информации, В отличие от известных устройств предложенное устройство для контроля блоков памяти позволяет записать карту дефектов i в дополнительное информационное поле контролируемого блока памяти. (Л 5 ил.

ФигЛ

Фиг,5

| Устройство для контроля блоков памяти | 1975 |

|

SU526954A1 |

| Походная разборная печь для варки пищи и печения хлеба | 1920 |

|

SU11A1 |

| Авторское свидетельство СССР | |||

| Устройство для контроля блоков памяти | 1976 |

|

SU646375A1 |

| Походная разборная печь для варки пищи и печения хлеба | 1920 |

|

SU11A1 |

Авторы

Даты

1986-11-15—Публикация

1985-05-13—Подача