(5) УСТРОЙСТВО ДЛЯ ОБРАБОТКИ РАДИОСИГНАЛОВ

| название | год | авторы | номер документа |

|---|---|---|---|

| Вычислительная система "Антикон" для предотвращения столкновения судов | 1983 |

|

SU1136178A1 |

| Устройство для отображения информации на экране телевизионного индикатора | 1986 |

|

SU1695372A1 |

| Устройство для операций над матрицами | 1985 |

|

SU1292008A1 |

| Логический анализатор | 1986 |

|

SU1432527A1 |

| Устройство для решения систем линейных алгебраических уравнений | 1986 |

|

SU1325508A1 |

| Устройство для обработки элементов сканерных изображений | 1983 |

|

SU1134945A1 |

| Устройство для возведения в п-ую степень | 1982 |

|

SU1132287A1 |

| Устройство для распознавания элементов треков | 1983 |

|

SU1161969A1 |

| Устройство для ввода информации | 1983 |

|

SU1109732A1 |

| Устройство для отображения информации | 1983 |

|

SU1193722A1 |

1

Изобретение относится к вычислительной технике и может использоваться в качестве приставки к электроннЙм вычислительным машинам (ЭВМ) при решении различных задач цифровой обработки радиосигналов в реальном масштабе -времени.

Известны универсальные ЭВМ, которые способны решать задачи .цифровой обработки радиосигналов, поступающих с выхода аналого-цифровых преобразователей О .

Однако эти ЭВМ имеют, как правило, один процессор, обеспе1 1вающий недостаточное быстродействие, большую (сотни килобайт) оперативную память.

Для решения задач цифровой обработки радиосигналов в реальном масштабе времени требуется более высокое быстродействие (несколько десятков миллионов операций в секунду) и сравнительно небольшая память (единицы килобайт), поэтому решение указанных

задач в реальном масштабе времени с помощью одной ЭВМ оказывается,-в ряде случаев, невозкГожным, а создание комплекса из нескольких ЭВМ - эюоноNjyчески невыгодным.

Известно устройство, содержащее многополюсник, регистр адреса, буферный регистр 2 .

Оно позволяет увеличить быстродействие вычислительного комплекса за счет выполнения таких операций, которые в ЭВМ из-за программного метода вычислений требуют больших за.трат машинного времени.

Наиболее близким по технической

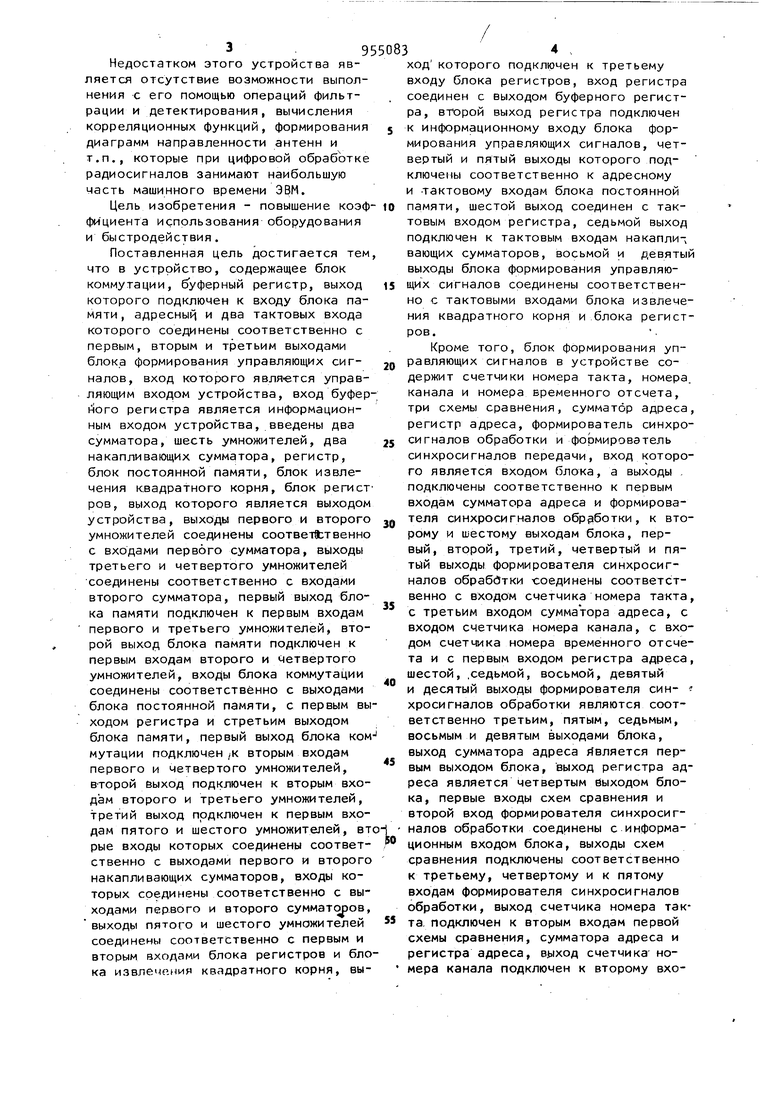

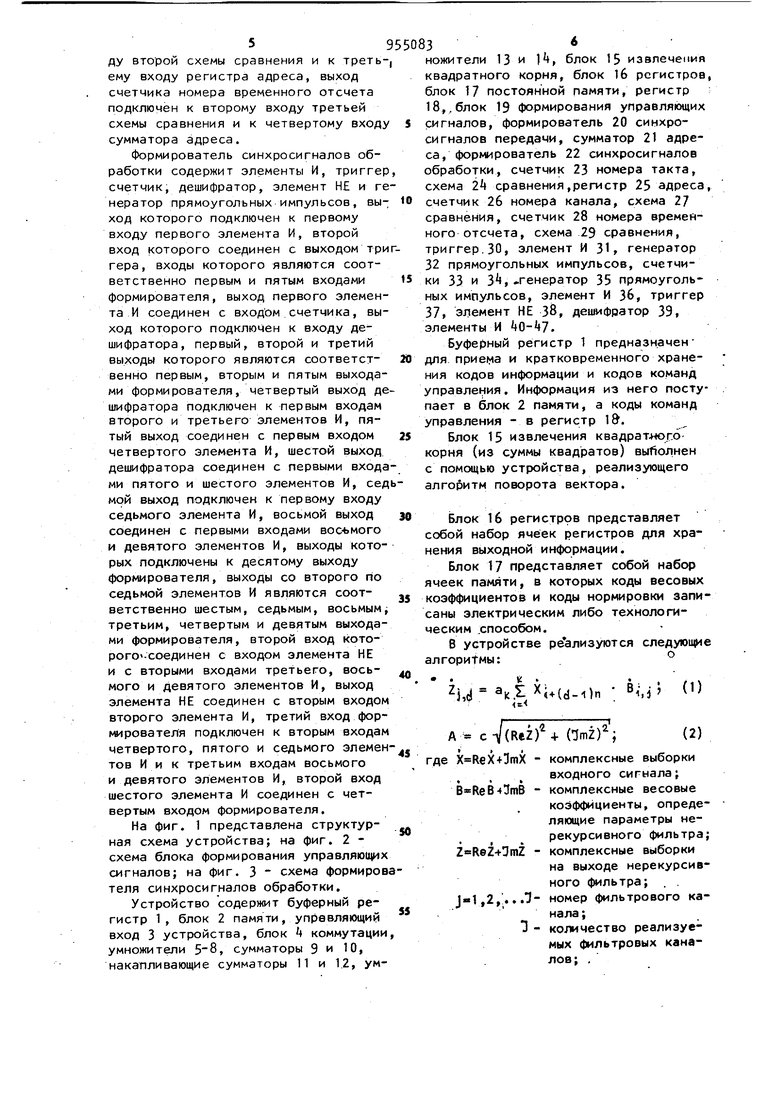

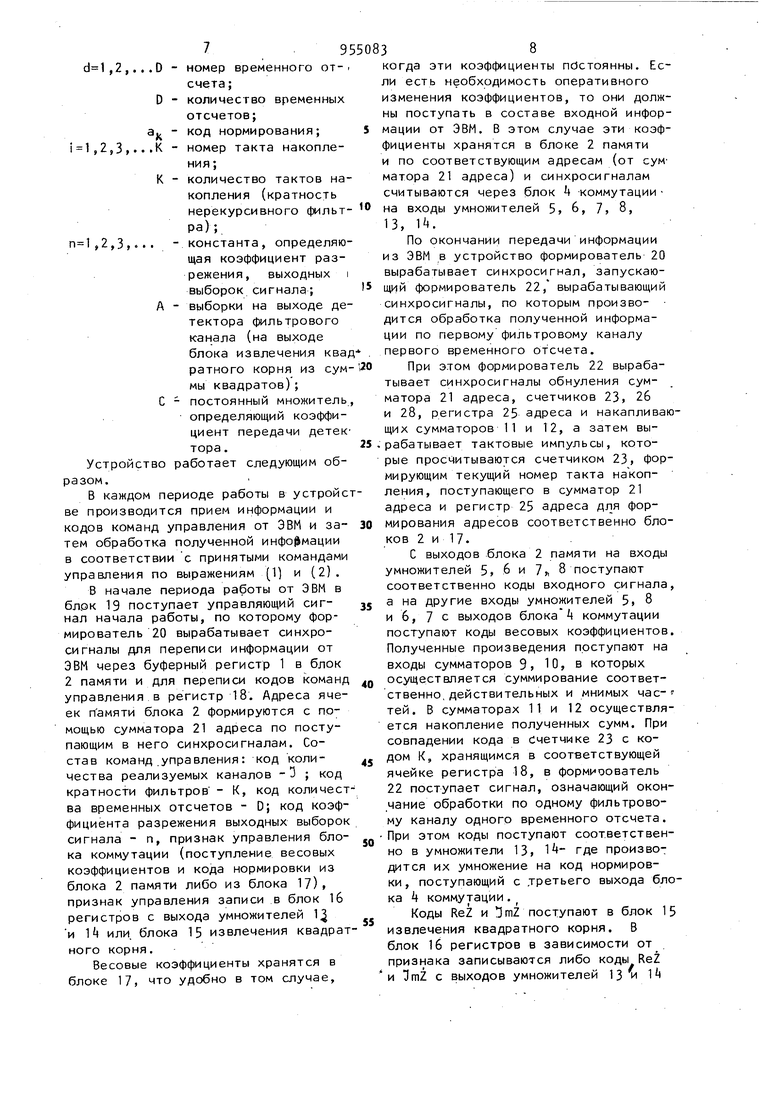

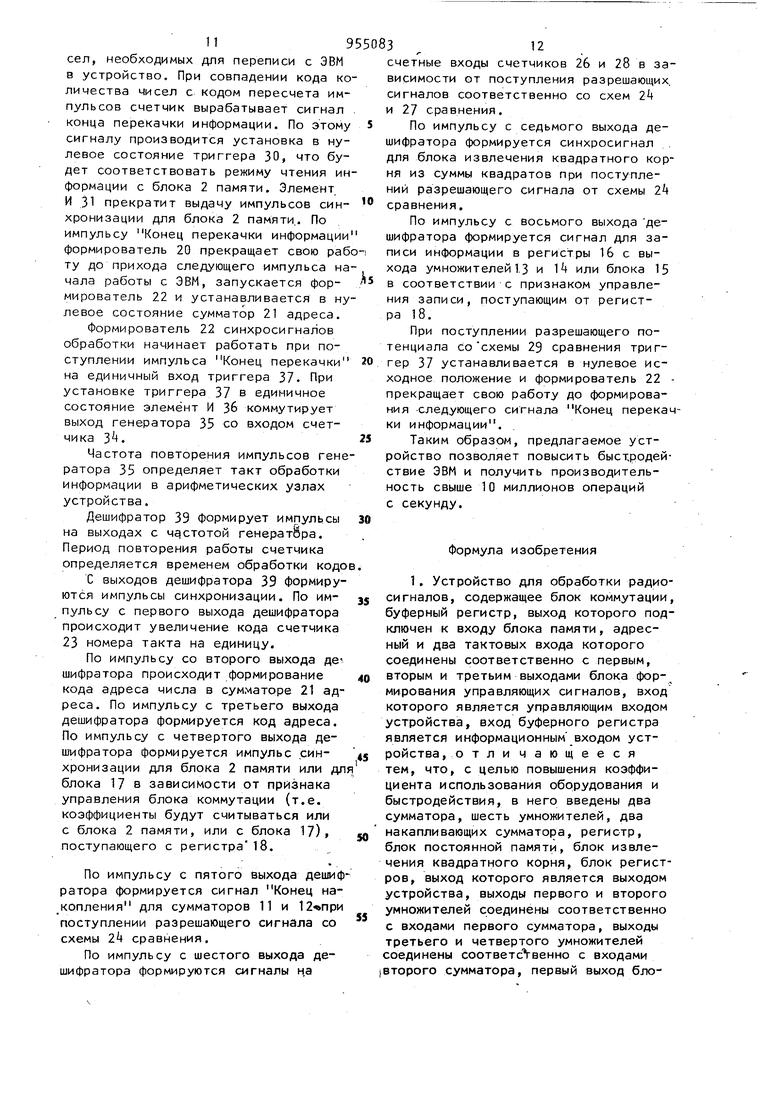

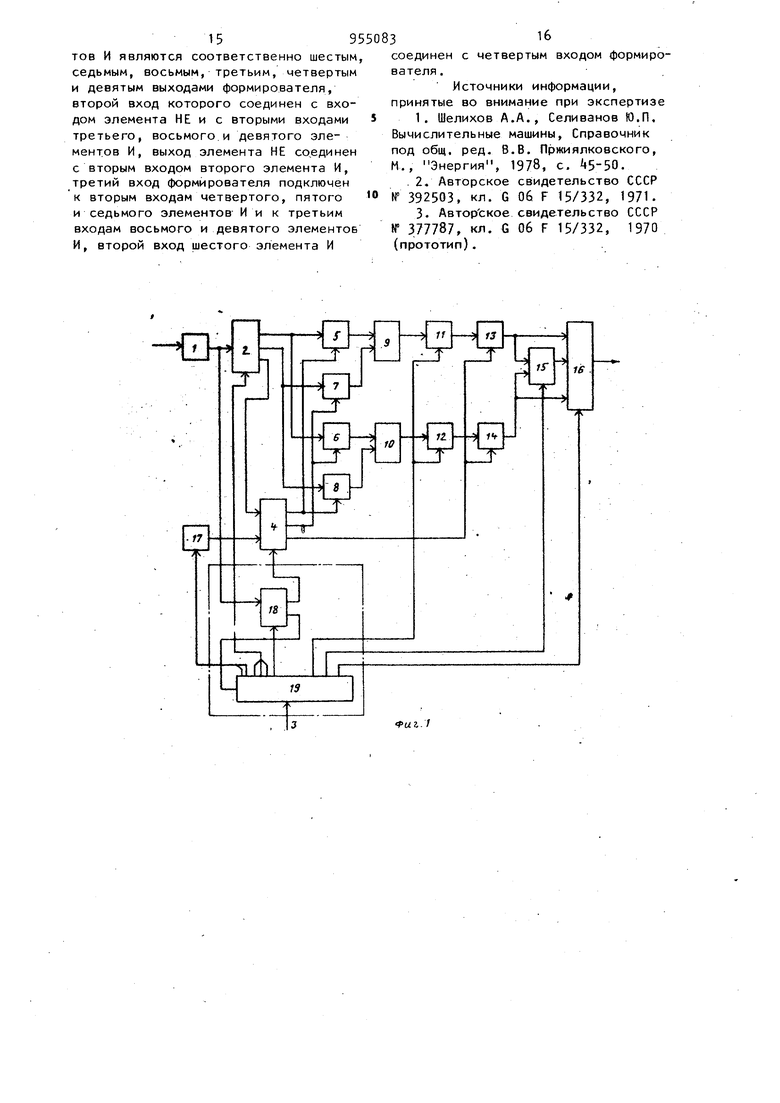

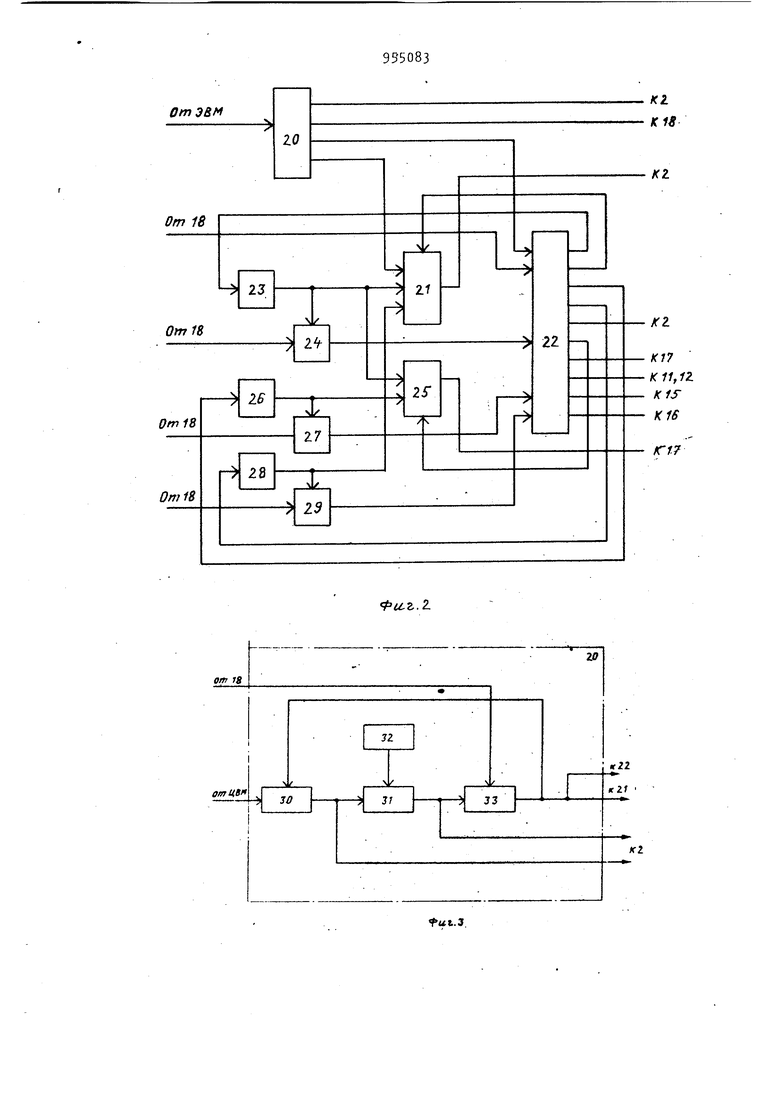

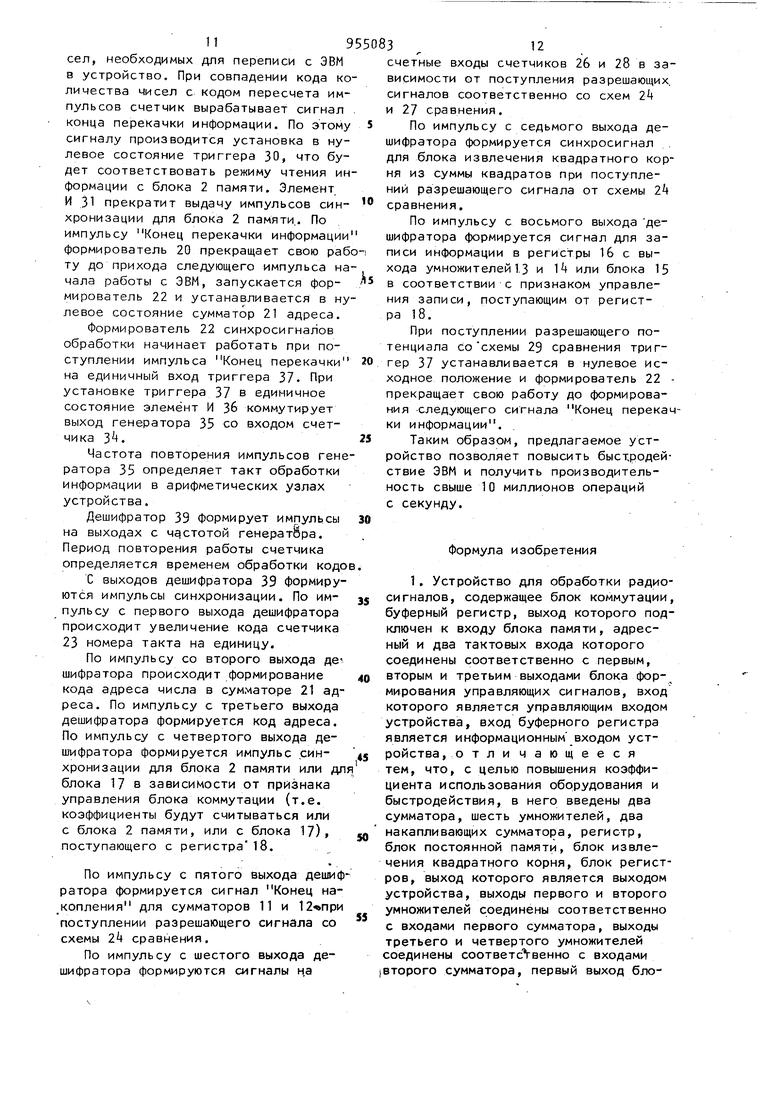

15 сущности к изобретению является устройство, в котором входное устройство подключено к блоку памяти, выходы последнего через два вероятностных элемента соединены с логической схе20мой И, а выходы блока управления соединены непосредственно и через блок коммутации с блоком памяти 3j. Недостатком этого устройства является отсутствие возможности выполнения с его помощью операций фильтрации и детектирования, вычисления корреляционных функций, формирования диаграмм направленности антенн и т.п., которые при цифровой обработке радиосигналов занимают наибольшую часть машинного времени ЭВМ. Цель изобретения - повышение коэф фициента использования оборудования и быстродействия. Поставленная цель достигается тем что в устройство, содержащее блок коммутации, буферный регистр, выход которого подключен к входу блока памяти, адресный и два тактовых входа которого соединены соответственно с первым, вторым и третьим выходами блока формирования управляющих сигналов, вход которого явля-ется управляющим входом устройства, вход буфер ного регистра является информационным входом устройства, введены два сумматора, шесть умножителей, два накапливающих сумматора, регистр, блок постоянной памяти, блок извлечения квадратного корня, блок регист ров, выход которого является выходом устройства, выходы первого и второго умножителей соединены соответЯЬтвенно с входами первого сумматора, выходы третьего и четвертого умножителей соединены соответственно с входами второго сумматора, первый выход блока памяти подключен к первым входам первого и третьего умножителей, второй выход блока памяти подключен к первым входам второго и Четвертого умножителей, входы блока коммутации соединены соответственно с выходами блока постоянной памяти, с первым вы ходом регистра и стретьим выходом блока памяти, первый выход блока ком мутации подключен ;К вторым входам первого и четвертого умножителей, второй выход подключен к вторым входам второго и третьего умножителей, третий выход подключен к первым входам пятого и шестого умножителей, вт рые входы которых соединены соответственно с выходами первого и второго накапливающих сумматоров, входы которых соединены соответственно с выходами первого и второго сумматоров, выходы пятого и шестого умножителей соединены соответственно с первым и вторым входами блока регистров и бло ка извлемегния квадратного корня, вы9ход которого подключен к третьему входу блока регистров, вход регистра соединен с выходом буферного регистра, второй выход регистра подключен к информационному входу блока формирования управляющих сигналов, четвертый и пятый выходы которого подключены соответственно к адресному и тактовому входам блока постоянной памяти, шестой выход соединен с тактовым входом регистра, седьмой выход подключен к тактовым входам накапли-, вающих сумматоров, восьмой и девятый выходы блока формирования управляющих сигналов соединены соответственно с тактовыми входами блока извлечения квадратного корня и блока регистров. Кроме того, блок формирования управляющих сигналов в устройстве содержит счетчики номера такта, номера, канала и номера временного отсчета, три схемы сравнения, сумматор адреса, регистр адреса, формирователь синхросигналов обработки и формирователь синхросигналов передачи, вход которого является входом блока, а выходы . подключены соответственно к первым входам сумматора адреса и формирователя синхросигналов обработки, к второму и шестому выходам блока, первый, второй, третий, четвертый и пятый выходы формирователя синхросигналов обработки соединены соответственно с входом счетчика номера такта, с третьим входом сумматора адреса, с входом счетчика номера канала, с входом счетчика номера временного отсчета и с первым входом регистра адреса, шестой, .седьмой, восьмой, девятый и десятый выходы формирователя синхросигналов обработки являются соответственно третьим, пятым, седьмым, восьмым и девятым выходами блока, выход сумматора адреса Является первым выходом блока, выход регистра адреса является четвертым выходом блока, первые входы схем сравнения и второй вход формирователя синхросигналов обработки соединены с информационным входом блока, выходы схем сравнения подключены соответственно к третьему, четвертому и к пятому входам формирователя синхросигналов обработки, выход счетчика номера такта, подключен к вторым входам первой схемы сравнения, сумматора адреса и регистра адреса, выход счетчика номера канала подключен к второму входу второй схемы сравнения и к треть ему входу регистра адреса, выход счетчика номера временного отсчета подключен к второму входу третьей схемы сравнения и к четвертому входу сумматора адреса. Формирователь синхросигналов обработки содержит элементы И, тригге счетчик, дешифратор, элемент Н и ге нератор прямоугольных импульсов, выход которого подключен к первому входу первого элемента И, второй вход которого соединен с выходом три гера, входы которого являются соответственно первым и пятым входами формирователя, выход первого элемента И соединен с входом счетчика, выход которого подключен к входу дешифратора, первый, второй и третий выходы которого являются соответственно первым, вторым и пятым выходами формирователя, четвертый выход де шифратора подключен к первым входам второго и третьего элементов И, пятый выход соединен с первым входом четвертого элемента И, шестой выход дешифратора соединен с первыми входа ми пятого и шестого элементов И, сед мой выход подключен к первому входу седьмого элемента И, восьмой выход соединен с первыми входами вос-ьмого и девятого элементов И, выходы которых подключены к десятому выходу формирователя, выходы со второго по седьмой элементов И являются соответственно шестым, седьмым, восьмымj третьим, четвертым и девятым выходами формирователя, второй вход которого -соединен с входом элемента НЕ и с вторыми входами третьего, восьмого и девятого элементов И, выход элемента НЕ соединен с вторым входом второго элемента И, третий вход фор 1poвaтeля подключен к вторым входам четвертого, пятого и седьмого элемен тов И и к третьим входам восьмого и девятого элементов И, второй вход шестого элемента И соединен с четвертым входом формирователя. На фиг. 1 представлена структурная схема устройства; на фиг. 2 схема блока формирования управляюи|их сигналов; на фиг. 3 схема формиров теля синхросигналов обработки. Устройство содержит буферный регистр 1, блок 2 памяти, управляющий вход 3 устройства, блок k коммутации умножители , сумматоры 9 и 10, накапливающие сумматоры 11 и 1.2, ум3ножители 13 и ), блок 15 извлечения квадратного корня, блок 1б регистров, блок 17 постоянной памяти, регистр 18,,блок 19 формирования управляющих сигналов, формирователь 20 синхросигналов передачи, сумматор 21 адреса, формирователь 22 синхросигналов обработки, счетчик 23 номера такта, схема 2 сравнения,регистр 25 адреса, счетчик 26 номера канала, схема 27 сравнения, счетчик 28 номера временного отсчета, схема 29 сравнения, триггер.30, элемент И 31, генератор 32 прямоугольных импульсов, сметчики 33 и 3,-генератор 35 прямоугольных импульсов, элемент И 36, триггер 37, элемент НЕ 38, дешифратор 39, элементы И . Буферный регистр 1 предназначен для приема и кратковременного хранения кодов информации и кодов команд управления. Информация из него поступает в блок 2 памяти, а коды команд управления - в регистр 1&. Блок 15 извлечения квадрат юг.о корня (из суммы квадратов) выполнен с помощью устройства, реализующего алгоритм поворота вектора. Блок 16 регистров представляет собой набор ячеек регистров для хранения выходной информации. Блок 17 представляет собой набор ячеек памяти, в которых коды весовых коэффициентов и коды нормировки записаны электрическим либо технологическим способом. В устройстве реализуются следующие алгоритмы: ixU(d-.)n B,iJ (1) А с-J(ReZ) 4- WmZ); где X R€X+3mX комплексные выборки входного сигнала; B ReB4tlmB комплексные весовые коэффициенты, определяющие параметры нерекурсивного фильтра; - комплексные выборки на выходе нерекурсивного фильтра; . . jel ,2,.. Л- номер фильтрового канала;количество реализуемых фильтровых каналов; , ,2,...D - номер временного отсчета;D - количество временных отсчетов; а, - код нормирования; 1 1,2,3,...К - номер такта накопления;К - количество тактов на копления (кратность нерекурсивного фильт ра);, ,2,3,... - константа, определяю щая коэффициент разрежения, выходных выборок сигнала; А - выборки на выходе де тектора фильтрового к-анала (на выходе блока извлечения ква ратного корня из сум мы квадратов) ; С - постоянный множитель определяющий коэффициент передачи детек тора . Устройство работает следующим образом. В каждом периоде работы в устройс ве производится прием информации и кодов команд управления от ЭВМ и затем обработка полученной информации в соответствии с принятыми командами управления по выражениям 1 и (2). В начале периода работы от ЭВМ в бл,ок 19 поступает управляющий сигнал начала работы, по которому формирователь 20 вырабатывает синхросигналы для переписи информации от ЭВМ через буферный регистр 1 в блок 2 памяти и для переписи кодов команд управления в регистр 18. Адреса ячеек памяти блока 2 формируются с помощью сумматора 21 адреса по поступающим в него синхросигналам. Состав команд .управления: код количества реализуемых каналов -3 ; код кратности фильтров - К, код количест ва временных отсчетов - D; код коэффициента разрежения выходных выборок сигнала - п, признак управления блока коммутации (поступление весовых коэффициентов и кода нормировки из блока 2 памяти либо из блока 17), признак управления записи в блок 16 регистров с выхода умножителей 1Д и ИЛИ. блока 15 извлечения квадрат ного корня. Весовые коэффициенты хранятся в блоке 17, что удобно в том случае, когда эти коэффициенты постоянны. Если есть необходимость оперативного изменения коэффициентов, то они должны поступать в составе входной информации от ЭВМ. В этом случае эти коэффициенты хранятся в блоке 2 памяти и по соответствующим адресам (от сум матора 21 адреса) и синхросигналам считываются через блок h коммутации 5, 6, 7, 8, на входы умножителей 13, 4. По окончании передачи информации из ЭВМ в устройство формирователь 20 вырабатывает синхросигнал, запускающий формирователь 22, вырабатывающий синхросигналы, по которым произво- дится обработка полученной информации по первому фильтровому каналу первого временного отсчета. При этом формирователь 22 вырабатывает синхросигналы обнуления сумматора 21 адреса, счетчиков 23, 26 и 28, регистра 25 адреса и накапливающих сумматоров 11 и 12, а затем вырабатывает тактовые импульсы, которые просчитываются счетчиком 23, формирующим текущий номер такта накопления, поступающего в сумматор 21 адреса и регистр 25 адреса для формирования адресов соответственно блоков 2 и 1 7. С выходов блока 2 памяти на входы умножителей 5, 6 и 7 8 поступают соответственно коды входного сигнала, а на другие входы умножителей 5 8 и 6, 7 с выходов блока А коммутации поступают коды весовых коэффициентов. Полученные произведения поступают на входы сумматоров 9, Ю, в которых осуществляется суммирование соответственно, действительных и мнимых частей. В сумматорах 11 и 12 осуществляется накопление полученных сумм. При совпадении кода в счетчике 23 с кодом К, хранящимся в соответствующей ячейке регистра 18, в формиоователь 22 поступает сигнал, означающий окончание обработки по одному фильтровому каналу одного временного отсчета. При этом коды поступают соответственно в умножители 13, Т где производится их умножение на код нормировки, поступающий с .третьего выхода блока k коммутации. Коды ReZ и jmZ поступают в блок 15 извлечения квадратного корня. В блок 16 регистров в зависимости от признака записываются либо коды ReZ и tImZ с выходов умножителей 13 i 1

либо код А с выхода блока 15. По синхросигналу коды- с выхода блока 16 регистров переписываются во внешнее усройство (например, ЭВМ),

По окончании описанных процессов формирователь 22 вырабатывает синхросигналы обнуления счетчика 23, регистра 25 адреса, накапливающих сумматоров 11 и 12 и вырабатывает тактовый импульс, который поступает в счетчик 26 номера канала, увеличивая его на 1, и процессы обработки информации по следующему фильтровому каналу повторяются аналогично вышеописанному.

При совпадении кодов в счетчиках 23 и 26 с кодами К и Т , хранящимися 8 соответствующих ячейках регистра 18, в формирователь 22 от схем сравнения и 27 поступают сигналы, означающие окончание обработки сигналов по всем фильтровым каналам одного временного отсчета. После этого формирователь 22 вырабатывает сигналы обнуления счетчиков 23 и 26, сумматора 21 адреса, регистра 25 адреса, накапливающих сумматоров 11 и 12 и вырабатывает тактовый импульс, который поступает в счетчик 28 номера временного отсчета, увеличивая его код на п единиц. При равенстве- кодов в счетчиках .23, 26 и 28 с кодами К, , D, хранящимися в соответствующих ячейках регистра 18, в формирователь 22 со схем сравнения 2, 27 и 29 по ступают сигналы, означающие оконча- . ние обработки по всем фильтровым каналам всех временных отсчетов. После этого формирователь 22 вырабатыэает синхросигналы конца обработки, поступающие из устройства на вход ЭВМ.

Коды адресов ячеек блока 2 формируются в сумматоре 21 адреса путем сложения кода счетчика 23 номера такта с кодом счетчика 28 номера временного отсчета.

Коды адресов блока 1.7 формируются в регистре 25 адреса путем записи в его младшие разряды кода счетчика 23 а в старшие разряды - кода счетчика 26 номера канала.

ЕС.ГМ весовые коэффициенты и код нормировки поступают на входы умножителей из блока 2 памяти , то соответствующие адреса ячеек памяти блока 2 формируются в сумматоре 21 путем добавления к коду константы из формирователя 22, определяющей начальный адрес ячеек памяти, где хранятся эти коэффициенты.

При поступлении в устройство от ЭВМ кода управления, задающего автокорреляционный способ обработки сигналов и кода П 0, процессы обработки информации осуществляются аналогично вышеописанному, за исключением того, что счетчик 26 находится всегд в нулевом состоянии, а коды адресов ячеек памяти для сигнала 1 и для сдвнутого сигнала i + (d-l)n3 формируются в сумматоре 21 адреса.

При поступлении в устройство от ЭВМ кода упвавления, задающего взаимнокорреляционный способ обработки, и кода О процессы обработки инфомации осуществляются аналогично вышеописанному, за исключением того, что счетчик 2б находится всегда в нулевом состоянии, а коды адресов ячеек памяти для первого сигнала i + (d-1)nj и коды адресов ячеек памяти для второго сигнала формируются в суммато;ре 21, причем коды адресов ячеек памяти второго сигнала формируются путем добавления к коду i4(d-l)n кода константы из фо эмирователя 22, определяющей начальный адрес ячеек памяти блока 2, в которых хранятся коды второго сигнала.

При поступлении в устройство от ЭВМ кода управления, задающего режим формирования диаграммы направленности антенны, и кодов tJ О и О 1 процессы обработки информации осуществляются аналогично работе при фильтрационном способе обработки сигналов, за исключением того, чтоосчетчики 26 и 28 находятся всегда в нулевЪм состоянии.

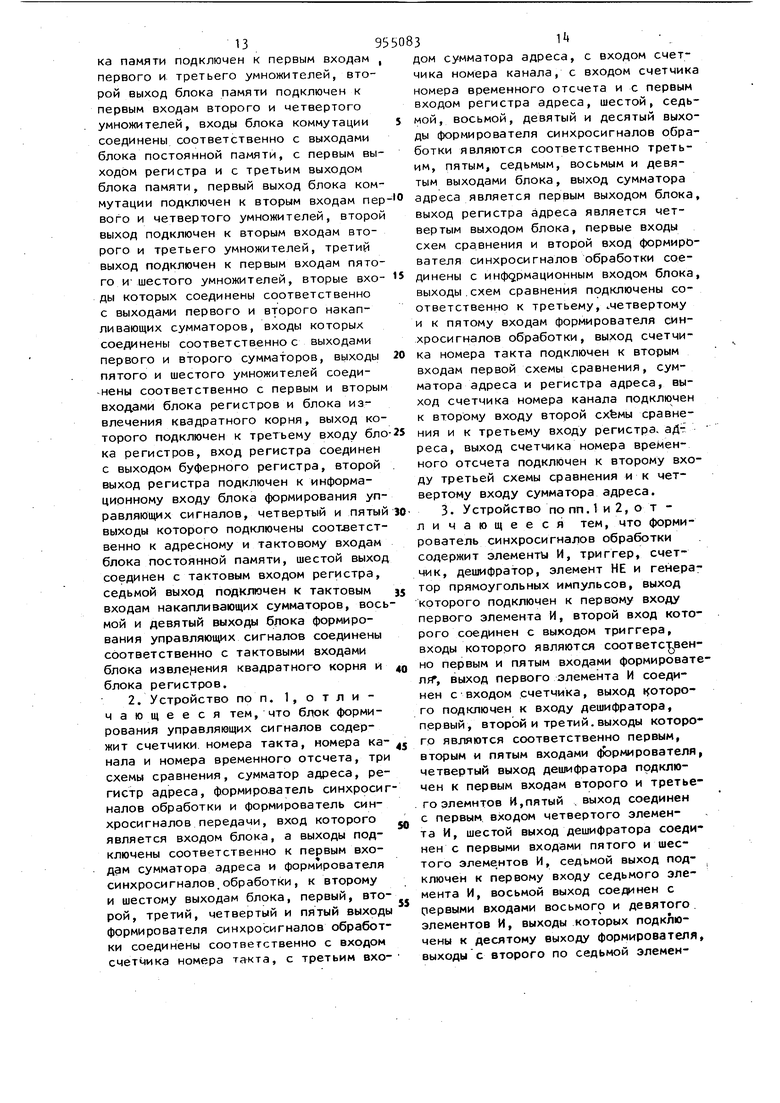

Формирователь 20 (фиг. 3)при перекачке информации работает следующим образом.

На первый вход триггера 30 поступает сигнал начала работы от ЭВМ, по которому триггер 30 устанавливается в единичное состояние. При этом на элемент И 31-подается разрешающий потенциал и на счетный вход счетчика 33 поступают импульсы тактовой частоты с генератора 32. Частота генератора 32 определяет темп приема информации от ЭВМ. На блок 2 памяти выдаются управляющий потенциал Признак записи информации с триггера .30 и импульсы синхронизации с выхода элемента И 31. На счетчик 33 с регистра 18 подается код количества чисел, необходимых для переписи с ЭВМ в устройство. При совпадении кода ко личества чисел с кодом пересчета импульсов счетчик вырабатывает сигнал конца перекачки информации. По этому сигналу производится установка в нулевое состояние триггера 30, что будет соответствовать режиму чтения ин формации с блока 2 памяти. Элемент И 31 прекратит выдачу импульсов синхронизации для блока 2 памяти.. По импульсу Конец перекачки информации формирователь 20 прекращает свою раб ту до прихода следующего импульса на чала работы с ЭВМ, запускается формирователь 22 и устанавливается в ну левое состояние сумматор 21 адреса. Формирователь 22 синхросигналов обработки начинает работать при поступлении импульса Конец перекачки на единичный вход триггера 37. При установке триггера 37 в единичное состояние элемент И Зб коммутирует выход генератора 35 со входом счетчика 3. Частота повторения импульсов гене ратора 35 определяет такт обработки информации в арифметических узлах устройства. Дешифратор 39 формирует импульсы на выходах с частотой генерат8ра. Период повторения работы счетчика определяется временем обработки кодо С выходов дешифратора 39 формируются импульсы синхронизации. По импульсу с первого выхода дешифратора происходит увеличение кода счетчика 23 номера такта на единицу. По импульсу со второго выхода де шифратора происходит формирование кода адреса числа в сумматоре 21 адреса. По импульсу с третьего выхода дешифратора формируется код адреса. По импульсу с четвертого выхода дешифратора формируется импульс синхронизации для блока 2 памяти или дл блока 17 в зависимости от признака управления блока коммутации (т.е. коэффициенты будут считываться или с блока 2 памяти, или с блока 17), поступающего с регистра18. По импульсу с пятого выхода дешиф ратора формируется сигнал Конец накопления для сумматоров 11 и поступлении разрешающего сигнала со схемы 2k сравнения. По импульсу с шестого выхода дешифратора формируются сигналы н.а счетные входы счетчиков 26 и 28 в зависимости от поступления разрешающих, сигналов соответственно со схем 2k и 27 сравнения. По импульсу с седьмого выхода дешифратора формируется синхросигнал . для блока извлечения квадратного корня из суммы квадратов при поступлений разрешающего сигнала от схемы 24 сравнения. По импульсу с восьмого выхода дешифратора формируется сигнал для записи информации в регистры 16 с выхода умножителей 13 и 1 или блока 15 в соответствии с признаком управления записи, поступающим от регистра 18. При поступлении разрешающего потенциала сосхемы 29 сравнения триггер 37 устанавливается в нулевое исходное положение и формирователь 22 прекращает свою работу до формирования следующего сигнала Конец перекачки информации. Таким образом, предлагаемое устройство позволяет повысить быстродействие ЭВМ и получить производительность свыше 10 миллионов операций с секунду. Формула изобретения 1. Устройство для обработки радиосигналов, содержащее блок коммутации, буферный регистр, выход которого подключен к входу блока памяти, адресный и два тактовых входа которого соединены соответственно с первым, вторым и третьим выходами блока формирования управляющих сигналов, вход которого является управляющим входом устройства, вход буферного регистра является информационным входом устройства, отли чающееся тем, что, с целью повышения коэффициента использования оборудования и быстродействия, в него введены два сумматора, шесть умножителей, два накапливающих сумматора, регистр, блок постоянной памяти, блок извлечения квадратного корня, блок регистров, выход которого является выходом устройства, выходы первого и второго умножителей соединены соответственно с входами первого сумматора, выходы третьего и четвертого умножителей соединены соответс венно с входами Второго сумматора, первый выход блока памяти подключен к первым входам , первого и третьего умножителей, второй выход блока памяти подключен к первым входам второго и четвертого умножителей, входы блока коммутации соединены соответственно с выходами блока постоянной памяти, с первым выходом регистра и с третьим выходом блока памяти, первый выход блока коммутации подключен к вторым входам вого и четвертого умножителей, второ выход подключен к вторым входам второго и третьего умножителей, третий выход подключен к первым входам пято го и- шестого умножителей, вторые вхо ды которых соединены соответственно с выходами первого и второго накапливающих сумматоров, входы которых соединены соответственное выходами первого и второго сумматоров, выходы пятого и шестого умножителей соеди-нены соответственно с первым и вторым входами блока регистров и блока извлечения квадратного корня, выход которого подключен к третьему входу бло ка регистров, вход регистра соединен с выходом буферного регистра, второй выход регистра подключен к информационному входу блока формирования управляющих сигналов, четвертый и пятый выходы которого подключены соответственно к адресному и тактовому входам блока постоянной памяти, шестой выход соединен с тактовым входом регистра, седьмой выход подключен к тактовым входам накапливающих сумматоров, вось мой и девятый выходы блока формирования управляющих сигналов соединены соответственно с тактовыми входами блока извле| ения квадратного корня и блока регистров. 2. Устройство по п. 1, о т л и чающееся тем, что блок формирования управляющих сигналов содержит счетчики номера такта, номера канала и номера временного отсчета, три схемы сравнения, сумматор адреса, регистр адреса, формирователь синхросиг налов обработки и формирователь синхросигналов передачи, вход которого является входом блока, а выходы подключены соответственно к первым входам сумматора адреса и формирователя синхросигналов,обработки, к второму и шестому выходам блока, первый, второй, третий, четвертый и пятый выходы формирователя синхросигналов обработки соединены соответственно с входом счетчика номера такта, с третьим вхо9531 . дом сумматора адреса, с входом счетчика номера канала, с входом счетчика номера временного отсчета и с первым входом регистра адреса, шестой, седьмой, восьмой, девятый и десятый выходы формирователя синхросигналов обработки являются соответственно третьим, пятым, седьмым, восьмым и девятым выходами блока, выход сумматора адреса является первым выходом блока. выход регистра адреса является четвертым выходом блока, первые входы схем сравнения и второй вход формирователя синхросигналов обработки соединены с информационным входом блока, выходы.схем сравнения подключены соответственно к третьему, четвертому и к пятому входам формирователя синхросигналов обработки, выход счетчика номера такта подключен к вторым входам первой схемы сравнения, сумматора адреса и регистра адреса, выход счетчика номера канала подключен к второму входу второй сравнения и к третьему входу регистра, аДт реса, выход счетчика номера временного отсчета подключен к второму входу третьей схемы сравнения и к четвертому входу сумматора адреса. 3. Устройство по ПП.1 и 2, о т ли чающееся тем, что формирователь синхросигналов обработки содержит элементы И, триггер, счетчик, дешифратор, элемент НЕ и генератор прямоугольных импульсов, выход которого подключен к первому входу первого элемента И, второй вход которого соединен с выходом триггера, входы которого являются соответс венно первым и пятым входами формирователя, выход первого элемента И соединен с входом счетчика, выход которого подключен к входу дешифратора, первый, второй и третий.выходы которого являются соответственно первым, вторым и пятым входами (|юрмирователя, четвертый выход дешифратора подключен к первым входам второго и третьего злемнтов И,пятый .выход соединен с первым входом четвертого элемента И, шестой выход дешифратора соединен с первыми входами пятого и шестого элеме нтов И, седьмой выход подключен к первому входу седьмого элемента И, восьмой выход соединен с с:1ервыми входами восьмого и девятого элементов И, выходы которых подключены к десятому выходу формирователя, выходы с второго по седьмой элементов и являются соответственно шестым седьмым, восьмым, третьим, четвертым и девятым выходами формирователя, второй вход которого соединен с входом элемента НЕ и с вторыми входами третьего, восьмого.и девятого элементов И, выход элемента НЕ со,единен с вторым входом второго элемента И, третий вход формирователя подключен к вторым входам четвертого, пятого и седьмого элементов И и к третьим входам восьмого и девятого элементов И, второй вход шестого элемента И

соединен с четвертым входом формирователя.

Источники информации, принятые во внимание при экспертизе

. 2. Авторское свидетельство СССР № 392503, кл. G Об F 15/332, 1971.

От ЭВМ

От 18

Фи.г.2.

Авторы

Даты

1982-08-30—Публикация

1980-09-23—Подача