(54)

ЦИФРОВОЙ СПЕКТРАЛЬНЫЙ АНАЛИЗАТОР

| название | год | авторы | номер документа |

|---|---|---|---|

| Цифровой анализатор спектра | 1982 |

|

SU1126892A1 |

| Усреднитель-анализатор спектра Фурье | 1980 |

|

SU955086A1 |

| ЦИФРОВОЙ АНАЛИЗАТОР СПЕКТРА | 1994 |

|

RU2099720C1 |

| Цифровой анализатор энергетического спектра | 1978 |

|

SU769443A1 |

| Цифровой спектроанализатор | 1979 |

|

SU859950A1 |

| Многоканальный цифровой коррелометр | 1982 |

|

SU1040492A1 |

| КОРРЕЛЯЦИОННЫЙ АНАЛИЗАТОР ЧАСТОТНЫХ СВОЙСТВ ЛИНЕЙНОЙ СИСТЕМЫ | 2003 |

|

RU2242013C2 |

| Цифровой спектроанализатор | 1982 |

|

SU1092518A1 |

| Устройство для быстрого преобразования Фурье | 1984 |

|

SU1206802A1 |

| Цифровой спектроанализатор | 1976 |

|

SU634289A1 |

I

Изобретение относится к измерительной технике г в частности к многоканальным анализаторам спектра для получения текущих оценок спектральной плотности случайных процессов и выявления скрытых периодичностей, начало и длительность которых неизвестны

В технике спектрального анализа известнымногоканальные аналоговые спектроанализаторы, содержащие усилители, избирательные фильтры, детекторы и фильтры нижних частот ij.

Эти анализаторы достроены с использованием средств аналоговой техники, что вызывает значительные технические трудности при их реализации, особенно в области инфранизких частот. К недостаткам таких спектроанализаторов относятся нестабильность параметров, йизкая точность, необходимость применения большого объема оборудовакия ДЛ8 анализаторов, работакядих в широком диапазоне частот.

Известны также цифровые спектроанализаторы, основанные .на применении дискретного и быстрого преобразований Фурье. Один из таких анализаторов |2 является наиболее близким по техническому решению V. изобретению. Анализатор содержит 6jtojc оператйЁной памяти,

2

первый вход которого соединен с выходом арифметического блока, а выход подключен к входу блока сглаживания, выход которого является выходом анализатора, а управляющий вход соединен с первым выходом блока управления, второй выход которого подключен к управляющим входам арнфмети геского блока и блока оперативной памяти, а третий выход - к управляющему входу блока определения текущей фазы, инфор мационвый вход которого является ;первым входом анализатора.

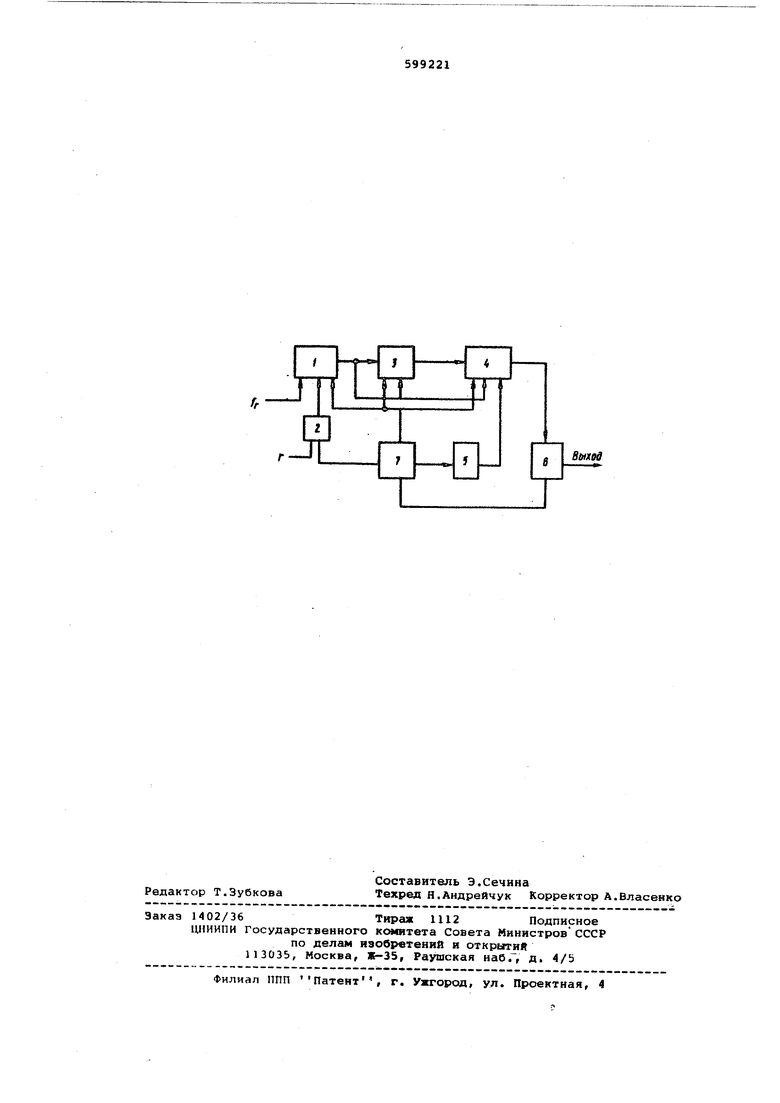

Вычислёйие оцейок спектральной плотности в такй8 ана лизаторах производится по отдельныь1 участкам реализации анализируемого процесса, что затрудняет, а при малых отношениях сигнал - шум делает невозможнЕлл выявление скрытой периодичности или других нестационарностей процесса, которые имеют конечную длительность и могут начинаться в произвольный момент времени. Более того, анализатор не пригоден для получения текущих оценок спектральной плотности в широком частотном диапазоне в реальном масштабе временя, так как расша&ение частотного диапазона в этом требует значительньЕя затрат оборудования для запомиианвя всей реализации исследуемого процесса усксрения операции умножения и увеличения числа коэффициентов разложения. Цель изобретения - расширение частотного диапазона анализатора, обеспечивающее текущую оценку спектральной плотности в широком частотном диапазоне. Это достигается тем, что в анализа тор введены блок постоянной памяти и блок задержки установки адреса, вход которого соединен с четвертым выходом блока управления, а выход подключен ко второму входу блока оперативной памяти, второй выход которого соединен г первым и со вторым входами арифметического блока и с выходом блока постоянной памяти, первый вход которого являемся вторым входом анализатора, второй вход соединен с выходом блока определения текущей фазы, а управляющий входподключен ко второму выходу блока управления. На чертеже представлена структурная схема предлагаемого цифрового ана лизатора, Анализатор содержит блок 1 постоянной памяти, блок 2 определания теку щей фазы, арифметический блок 3, блок 4 оперативной памяти, блок 5 задержки установки адреса, блок 6 сглаживания и блок 7 управления. Выход блока сглаживания является выходом анализатора. На первый вход блока 1 постоянной памяти поступают отсчеты анализируемо го процесса в двоичном коде, а на вход блока 2 вычисления текущей фа,5№1 номер этого отсчета г . Период поступления входной информации TO равен периоду квантования процесса во времени. Текущая фаза гармонической функ ции f 1 вычисляется по формуле «f -ast-ifT -r.k ,СраЭ) , CI) где Af - минимальный шаг частотного анализа, определякиций интер вал между частотами настрой ки избирательных фильтров; k - номер гармонии (частотного канала). Счет величин г ведется по модулю 2. Значение Z является конструктивно ПОСТОЯННОЙ, определяемой числом разрядов соответствукадего регистра в бло ке 2 фазы. При k 1 и полном заполне нии регистра Фазы должно выполняться соотнсшение Af Тд т « 1, что соответствует периоду гармоничностей функция 2Л. Следовательно, Д/.То 2- fR-.(modZ)-K Выходной величиной блока 2 являет ся двоичный код числа Mk « 2()li с размерностью радиан, учитыаемой в блоке 1 постоянной памяти. ычисленная, таким образом, фаза, а акже величина f в двоичном коде обазует адрес обращения к блоку 1 посоянной памяти. Блок 1 выполнен на снове долговременного запоминающего устройства и содержит всевозможные произведения LfT.-ilTi(2iru|-To- -.k для фазы в пределах от О до аг/2, где - коэффициент, определяющий постоянную времени,осреднения и, соответственно, полосупропускания. Он выбирается конструктивно кратным целой отрицательной степени двойки,т.е. 1.. Величины произведений для фазы более 3t/2 отличаются только знаком, который определяется в блоке 7 управления на основе анализа соответствующих разрядов регистра фазы. Арифметический блок 3 вычисляет текущие значения коэффициента разложения по алгоритмук,г °K.,. 23tAf tgrk, K.,r.r4,. Произведение L-f - os{2i3lTo4 k Af ) определяется с помощью блока 1 путем формирования в блоке 2 фазы, отличающейся от фазы синуса на /2. Выходной величиной блока 2 при этом является двоичный код Mki Mkf 2. Величины и Ь j выбираются из определенных Лчеек блока 4 оперативной памяти, адрес которых зависит от k , и подаются на второй вход, а также на младшие разряды первого входа арифметического блока, чем обеспечивается вычисление произведений .j и ЬЬц. путем сдвига-вправе на tj разрядов. Из выражения (2) следует зависимость между минимальными шагом частотного анализа и периодом квантования (4) Выражение х.-,-, ч вычисляемое в блоке 6, моделирует выходное напряжение избирательного Фильтра, частота настройки которого равна afk , а полоса пропускания t jfV Для упрощения аппаратурной реализации фильтров величина выбирается равной 5) Б спектроанализаторах полоса пропуска Ния f и шаг частотного анализа &f должны быть равны, поэтому из выражений (4) и (5) следует, что 2 - Ц+2(6) Выражение (6) определяет связь МёЖду конструктивными постоянными анёшизатора. Работой всех устройств анализа тора при выполнении операции вычисле ния фазы, обращения к блокам 1 и 4, вычисления коэффициентов с1-к,г/Ьк,, синхронизирует блок 7 управления. Пусть на вход анализатора поступи очередной г-и отсчет анализируемог процесса f. Блок 2 вычисляет фазу начальной (первой) гармоники T,e. . По адресу, составленно му из двоичных кодов, из блока 1 пос тоянной памяти выбирается произведение , L-J -smC2dtuf.Vr.k,), а из блока 4 оперативной памяти по адресу, например А, выбирается значе ние коэффициента а-к,г-1/ и арифметичес кий блок 3 определяет величину о-цгг которая запоминается в блоке 4 опера тивной памяти по адресу Aj. Для опре деления величины Ь из блока 1 постоянной памяти по адресу, составленному из двоичных кодов ff М ( / вы бирается произведение в bLnC2Jruj-TorKi+-«/2b;fTork), а из блока 4 оперативной памяти по другому адресу А - значение коэффициента -i, арифметический блок определяетвеличину Ьцт которая запо минается по адресу А. Далее блок 2 вычисляет фазу синус и косинуса второй гармоники HMki-Mki Z ; а из блока 1 выбира. ются произведения по адресам, составленным из двоичных кодов f ,Mk2 и , . Из блока 4 оперативной памя ти по адресам А 1 и А i выбираются величины O-n.jr-i и 6к-г«-1И арифметический блок 3 определ ет величины к и БК,/ которые запоминаются по адресам AI- и . Пусть в процессе вычисления in-ой и m+1-ой гармоник адрес ячейки блока 4 оперативной памяти сохранился постоянным и равным AI ). При этом произойдёт двойное обращение к одной и той же ячейке памяти за величинами а Kni,r-i и Ь -- /что приведет к уменьшению постоянной времени осреднения и расширению полосы в 2 раза. Управление адресами обращения к блоку 4 оперативной памяти осуществляет блок 5 в зависимости от номера гармоники k. Например, коэффициенты разложения от k, до k могут вычисляться и храниться в индивидуальн ячейках памяти от k до h :JB одной ячейке два коэффициента от kl„,дo в одной ячейке три коэффициента. Это приводит к тому, что полоса пропускания моделируемых избирательных фильтров будет равна соответственно Щ/ 2Bf г 39f Частотный диапазон анализа лР определяется как дР ( ) uf ) 6т af , а число занятых оперативных ячеек памяти равнопри этом Зт. Величина Ск,.к.,,., являющаяся оценкой спектральнойплотности, вычисляется в блоке 6, где происходит также сглаживание этой оценки. Период обращения к блоку 4 оперативной памяти при вычислении коэффициентов С ,. больше TO , так как а и Ь измеЕ1яются медленнее, чем входнойпроцесс. После завершения вычисления коэффициентов flj и 6ц у для г-го отсчета, через время Тоберется новый v + 1 отсче процесса f. и вычисляются коэффициенты ац и Ьк,гПФормула изобретения Цифровой спектральный анализатор, содержащий блок оперативной памяти, первый вход которого соединен с выходом арифметического блока, а выход подключен к входу блока сглаживания, выход которого является выходом анализатора, а управляющий вход соединен с первым выходом блока управления, второй выход которого подключен к управляющим входам арифметического блока и блока -оперативной памяти, а третий выход - к управляющему входу блока определения текущей фазы, информационный вход которого является первым входом анализатора, отличающийся тем , что, с целью расширения частотного диапазона анализатора, в него введены блок постоянной памяти и блок задержки установки адреса, вход которого соединен с четвертым выходом блока управления, а выход подключен ко второму входу блока оперативной памяти, второй выход которого соединен с первым и со вторым входами арифметического блока и с выходом блока постоянной памяти, первый вход которого является вторым входом анализатора, второй вход соединен с выходом блока определения текущей фазы, а управляющий вход подключен ко второму выходу блока управления. Источники информации, принятые во внимание при экспертизе: 1. Калинчук Б.А., Пиастро В.П. нализаторы инфразвуковых случайных роцессов. Л., Энергия, 1973, 2. Прикладной анализ случайных роцессов. Сборник научных трудов (Сибирское отделение АЯ СССР) Новосиирск, 1973.

Авторы

Даты

1978-03-25—Публикация

1975-02-18—Подача