1

Изобретение относится к импульсной технике.

Известен преобразователь частоты сигнала в цифровой код, содержащий делитель входной частоты, счетчик грубого отсчета, подсчитывающий число выходных импульсов этого делителя в течение фиксированного временного интервала, и счетчик, подсчитывающий число импульсов, необходимых для заполнения делителя входной частоты после окончания временного интервала 1. Недостатком такого преобразователя является его сложность.

Наиболее близким к изобретению является преобразователь, содержащий логический элемент И, один вход которого соединен со входом преобразователя и первым входом формирователя сигнала временного интервала. Второй вход формирователя соединен с первым выходом генератора эталонной частоты и первым входом второго логического элемента И. Второй вход второго элемента И подключен к первому выходу формирователя сигнала временного интервала, второй вход которого соединен со вторым входом первогоиз упомянутых логических элементов И. Выход первого элемента И соединен со входом счетчика, выход которого подключен к первому входу сумматора, причем второй выход генератора эталонной частоты соединен со входом делителя частоты 2. Этот преобразователь не обеспечивает достаточной точности.

Целью изобретения является повышение точности. Поставленная цель достигается тем, что в преобразователь введены реверсивный счетчик, логический элемент антисовпадения н дополнительный логический элемент И, входы которого соединены с выходом делителя частоты и третьим выходом формирователя сигнала временного интервала, а выход - с первым входом логического элемента антисовпадения, второй вход которого подключен к выходу реверсивного счетчика. Вход управления счетчика соединен с выходом первого логического элемента И, вход сложения - с выходом второго логического элемента И, а вход вычитания - с выходом логического элемента антисовпадення и вторым входом сумматора.

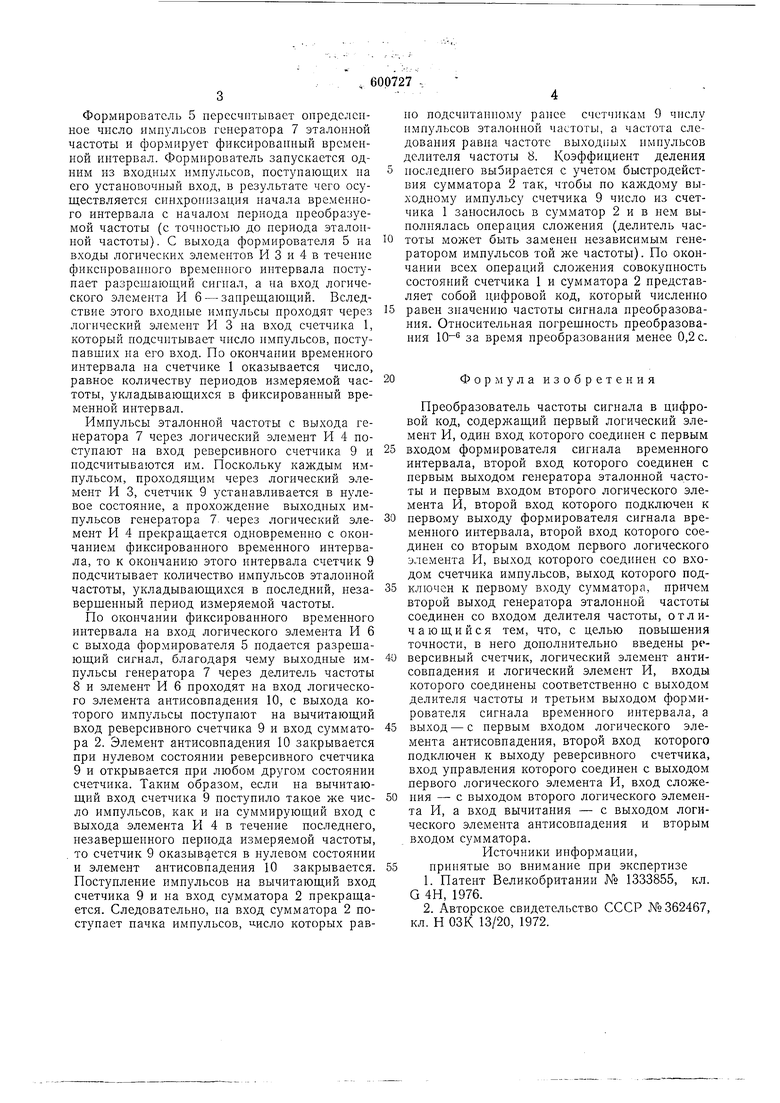

Структурная схема описываемого преобразователя приведена на чертеже.

Преобразователь содержит счетчик импульсов 1, сумматор 2, логические элементы И 3

н 4, формирователь 5 сигнала временного интервала, логический элемент И 6, генератор 7 эталонной частоты, делитель частоты 8, реверсивный счетчик 9 и логический элемент антисовпадения 10. Преобразуемый частотный снгнал подается на вход И.

Формирователь 5 пересчитывает определеииое число имиульсов генератора 7 эталонной частоты и формирует фиксироваииый временной интервал. Формирователь запускается одним из входных импульсов, поступающих на его установочный вход, в результате чего осуществляется синхронизация начала временного интервала с началом периода преобразуемой частоты (с точностью до периода эталонной частоты). С выхода формирователя 5 на входы логических элементов И 3 и 4 в течение фиксированного времеиного интервала поступает разрешающий сигнал, а на вход логического элемента И 6 - запрещающий. Вследствие этого входные импульсы проходят через логический элемент И 3 на вход счетчика 1, который подсчнтывает число импульсов, поступавших на его вход. По окончании временного интервала на счетчике 1 оказывается число, равное количеству периодов измеряемой частоты, укладывающихся в фиксированный временной интервал.

Импульсы эталонной частоты с выхода генератора 7 через логический элемент И 4 поступают па вход реверсивного счетчика 9 и подсчитываются им. Поскольку каждым импульсом, проходящим через логический элемент И 3, счетчик 9 устаиавливается в нулевое состояние, а прохождение выходных импульсов генератора 7 через логический элемент И 4 прекращается одновременно с окончанием фиксированного временного интервала, то к окончанию этого интервала счетчик 9 подсчитывает количество импульсов эталонной частоты, укладывающихся в последний, незаверщенный период измеряемой частоты.

По окончании фиксироваиного временного интервала на вход логического элемента И 6 с выхода формирователя 5 иодается разрешающий сигнал, благодаря чему выходные импульсы генератора 7 через делитель частоты

8и элемент И 6 проходят на вход логического элемента антисовпадения 10, с выхода которого импульсы поступают на вычитающий вход реверсивного счетчика 9 и вход сумматора 2. Элемент антисовнадения 10 закрывается при нулевом состоянии реверсивного счетчика

9и открывается при любом другом состоянии счетчика. Таким образом, если на вычитающий вход счетчика 9 поступило такое же число импульсов, как и на суммирующий вход с выхода элемента И 4 в течение последнего, пезаверщенного периода измеряемой частоты, то счетчик 9 оказывается в нулевом состоянии и элемент антисовпадения Ю закрывается. Поступление имнульсов на вычитающий вход счетчика 9 и на вход сумматора 2 прекращается. Следовательно, па вход сумматора 2 поступает пачка импульсов, число которых равпо подсчитанному ранее счетчикам 9 числу импульсов эталоиной частоты, а частота следования равна частоте выходных имнульеов делителя частоты 8. Коэффициент деления

последиего выбирается с учетом быстродействия сумматора 2 так, чтобы по каждому выходному импульсу счетчика 9 число из счетчика 1 заносилось в сумматор 2 и в нем выполнялась операция сложения (делитель частоты может быть замеиеп независимым генератором импульсов той же частоты). По окончании всех операций сложения совокупность состояний счетчика 1 и сумматора 2 представляет собой цифровой код, который численно

равен значению частоты сигнала преобразования. Относительная погрешность преобразования 10-° за время преобразования менее 0,2с.

Формула изобретения

Преобразователь частоты сигнала в цифровой код, содержащий первый логический элемент И, один вход которого соединен с первым

входом формирователя сигнала временного интервала, второй вход которого соединен с первым выходом генератора эталонной частоты и первым входом второго логического элемента И, второй вход которого подключен к

первому выходу формирователя сигнала временного интервала, второй вход которого соединен со вторым входом первого логического элемента И, выход которого соединен со входом счетчика импульсов, выход которого подключен к первому входу сумматора, причем второй выход генератора эталонной частоты соединен со входом делителя частоты, отличающийся тем, что, с целью повышения точности, в него дополнительно введены ррверсивный счетчик, логический элемент антисовпадения и логический элемент И, входы которого соединены соответственно с выходом делителя частоты и третьим выходом формирователя сигнала временного интервала, а

выход - с нервым входом логического элемента антисовпадения, второй вход которого подключен к выходу реверсивного счетчика, вход управления которого соединен с выходом первого логического элемента И, вход сложения - с выходом второго логического элемента И, а вход вычитания - с выходом логического элемента антисовпадения и вторым входом сумматора.

Источники информации,

принятые во внимание при экспертизе

1.Патент Великобритании № 1333855, кл. G 4Н, 1976.

2.Авторское свидетельство СССР 9 362467, кл. Н ОЗК 13/20, 1972.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство автоматической подстройки линейного закона частотной модуляции | 1984 |

|

SU1218463A1 |

| Преобразователь средней частоты в код | 1977 |

|

SU660245A1 |

| ПАТЕИНО-ТЕХННЧЕСИБИБЛИОТЕКА | 1971 |

|

SU316105A1 |

| Отметчик верхней мертвой точки поршня двигателя внутреннего сгорания | 1982 |

|

SU1076791A1 |

| Цифровой частотомер | 1980 |

|

SU940082A1 |

| Цифровой частотомер | 1980 |

|

SU1004905A1 |

| Цифровой частотомер | 1979 |

|

SU838602A1 |

| УСТРОЙСТВО ДЛЯ ОПРЕДЕЛЕНИЯ ПЛОТНОСТИ РАСПРЕДЕЛЕНИЯ ВЕРОЯТНОСТЕЙ СЛУЧАЙНОГО ПРОЦЕССА | 2000 |

|

RU2174706C1 |

| Аналого-цифровой преобразователь | 1981 |

|

SU1061260A1 |

| Устройство для измерения параметров радиоимпульсов | 1980 |

|

SU938206A1 |

Авторы

Даты

1978-03-30—Публикация

1975-12-17—Подача