управления формирователя дополнительных последовательностей импульсов, второй вход управления и вход «сброс которого соединены соответственно с выходами элемента равнозначности и ключа, а выход подключен ко входам счетных регистров через коммутатор, причем входы управления коммутатора соединены с выходами счетчика-распределителя импульсов, а выход источника опорного напряжения через последовательно соединенные преобразователи проводимости в напряжение постоянного тока подключен к одному из входов сумматора напряжений, другие входы которого соединены порознь с выходами отдельных преобразователей проводимости в напряжение постоянного тока, а выход сумматора напряжений подключен ко входу преобразователя напряжения в число-импульсный код.

Кроме того, указанная цель достигается также и тем, что в преобразователе средней частоты в код формирователь дополнительных последовательностей импульсов содержит последовательно соединенные реверсивный счетчик, регистр памяти и блок сравнения кодов, соединенный с оперативным счетчиком, ключ и элемент равнозначности, нричем первый вход реверсивного счетчика является входом «сброс формирователя, а второй вход реверсивного счетчика соединен с выходом элемента равнозначности, являющегося выходом формирователя, первый вход элемента равнозначности является первым управляющим входом формирователя, а второй вход соединен с выходом блока сравнения кодов и входом «сброс оперативного счетчика,первый вход которого является первым входом формирователя и подключен к первому входу ключа, а второй вход оперативного счетчика подключен к выходу ключа, второй вход которого является вторым управляющим входом формирователя и соединен со входом «перепись регистра памяти.

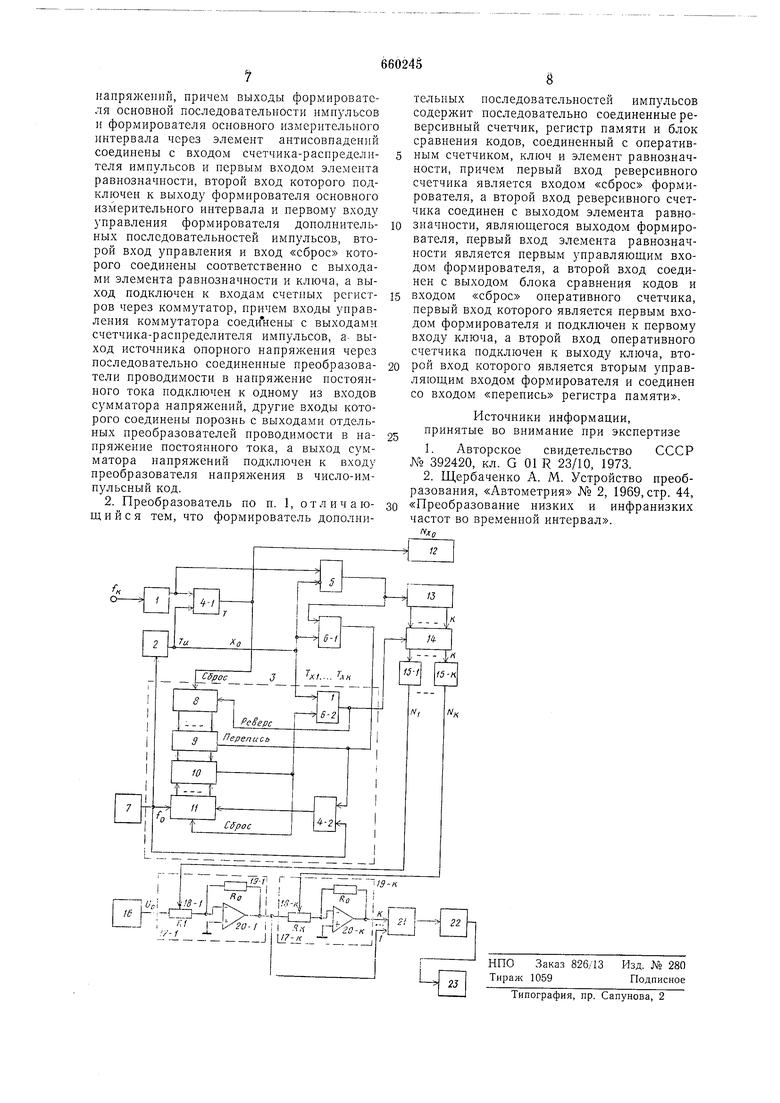

На чертеже показана функциональная электрическая схема преобразователя средней частоты в код.

Преобразователь средней частоты в код содержит формирователь 1 основной последовательности имиульсов (из периодов Гл-„ преобразуемой частоты /ж); формирователь 2 основного измерительного интервала 7ц (из опорной частоты /о); формирователь 3 дополнительных последовательностей импульсов NI ... NK ИЗ периодов Тх ... Тх преобраз)емой частоты, следующих за Гц; ключи 4-1, 4-2 (схемы совпадений); элемент 5 антисовпадений (НЕ-И); элементы равнозначности (ИЛИ) 6-1, 6-2, генератор опорной частоты; реверсивный счетчик 8; регистр памяти 9; блок 10 сравпения кодов; оперативный счетчик И; счетный регистр 12 старших разрядов выходного кода; счетчик-распределитель 13 импульсов, соответствующих периодам Гд ... 7а-,; коммутатор 14; дополнительные счетные регистры 15-1 - 15-к импульсных последовательностей ... NK, источник 16 опорного напряжения U(,; преобразователи 17-1 - 17-к проводимости в напряжение постоянного тока; кодоуправляемые резисторы () 18-1 - 18-к; образцовые резисторы (Ro) 19-1 - 19-к; операционные усилители 20-1 -

20-к; сумматор 21 напряжений; преобразователь 22 напряжения в число-импульсный код; счетный регистр 23 младщих разрядов выходного кода. Преобразователь работает следующим

образом.

В первом такте преобразования формируется основная носледовательность импульсов jV.v, - целое число периодов T.v, за измерительный интервал Гц, накопленмое в регистре 12. При этом каждым импульсом последовательности Лл-, сбрасывается накопленное в реверсивном счетчике 8 количество импульсов /о-Тл. Второй такт начинается с поступления заднего фронта

7,. При этом снимается сброс счетчика 8 н происходит (через элемент равнозначности 6-2) его реверсирование; одновременно через элемент равнозначности 6-1 поступает команда на перепись кода, соответствующего первому остаточному временному интервалу /о и-Лл-оТл-о из реверсивного счетчика 8 в регистр памяти 9. Далее код to сравнивается с кодом, накапливаемым в оперативном счетчике 11, и в момент их

равенства блок 10 сравнения кодов выдает импульс, сбрасывающий оперативный счетчик 11 и выполняющий (через элемент равнозначности 6-2) очередное реверсирование счетчика 8. Тем самым, в пределах

первого периода Гд-, примыкающего к интервалу Гп, через элемент равнозначности 6-2 и коммутатор 14 на вход первого дополнительного регистра 15-1 поступают импульсы, соответствующие количеству интервалов /о, укладывающихся в 7л-,, и в регистре 15-1 накапливается код определяемый из условия Гд , где i - второй остаточный временной интервал, выделенный по заднему фронту периода

Гд:, или переднему фронту периода Тх, Соответствующий импульс поступает с выхода элемента антисовпадений 5 на вход счетчика-распределителя 13, переводя его из исходного состояния «1, в состояние

«2. При этом управляющий сигнал появляется на втором входе коммутатора 14, и следовательно, выход формирователя 3 дополнительных импульсных последовательностей подключается к дополнительному

регистру 15-2. Тот же импульс через элемент равнозначности 6-1 выдает команду на перепись из реверсивного счетчика 8 в регистр памяти 9 кода второго остатка t. Далее аналогично подсчитывается количество интервалов t, укладывающихся во

втором после 1и периоде Т,, причем соотi3eTCTJsyiouj, чиСоТО-импульсный код поступает на вход дополнительного регистра 15-2 через элемент равнозначности 6-2; в момент окончания периода Тх, в дополнительпом регистре 15-2 формируется код Л2, соответствующий 4iKviy иптервалов ti, укладывающихся в Гд-. : Тх, N2t}- -t2, где 2 - третий остаточный временный интервал. В течение k следуюш,их за 7, периодов вырабатываются коды Л/1 ... jV, соответствуЮ1цие последовательным итерация; ;

T,N,f, + t, T,,:--N,t, + t,

Т, -- Л,к-1 + к.

Отсюда ясно, что в предлагаемом преобразователе общее время преобразования составляет , тогда как в известных преобразователях при том же колг честве итераций k и десятичном представлении общее время преобразования составляет Тп . Фактический выигрыщ в точности и быстродействии определяется сходимостью последовательных итераций. Если принять (в пренебрежении быстрымифлуктуациямипериода

Тх)Тх, Т,,, . . . TXK ТX,, то из приведенных выше соотношений получим результат й-го приближения средней частоты fx

A,z:zAA,. + AAA,r. A,,-f

I ( +(|)2к-1

Щ ЛГ,.,...

где - код младших разрядов, выделяемый в регистре 23. Преобразование кодов Л ... NK в код A.VK выполняется следующим образом. Сопротивления кодоуправляемых резистров 18-1 - 18-к пропорциональным кодам ... Лк соответственно, а выходные напряжения преобразователей 17-1 ... 17-к, благодаря их последовательному соединению, обратно пропорциональны произведениям ...

/; - Tf ° -)// р

.R.- ,

1

1

,... У-

:

0-п.о

NI-N, 1

(r,Rl

...

где К - коэффициент преобразования Ni в Ri. При на выходе сумматора 21 и, следовательно, на выходе преобразователя 22, выделяется сигнал, пропорциональный ДуУкАнализ приведенного итерационного алгоритма показывает, что он сходится как 1/(к+2), где к-число итераций. В сопоставлении со сходимостью известных итерационных способов и устройств, которая составляет (при десятичном представлении) 10-, ясно, что для получения сравнимой точности в предложенном устройстве необходимо использовать большее количество

итераций. Например, в нониусном способе или способе умножения остаточных временных интервалов для получения точности требуется две итерации, а в предложенном варианте - три итерации (1/5 1/120), соответственно для получения точности 10 в известных устройствах необходимо выполнить три итерации, а в предложеином - четыре(1/6 1/720).

В связи с более медленной сходимостью выигрыш в быстродействии при сравнимой точности несколько уменьшается. Например, если минимальной измеряемой частоте (fx) min соответствует максимальный период

Т(Тх)тах, то выбирая Г„ 10 (Гж) шах и нринимая результирующую точность измерения (/x)niin 10 получим общее время преобразования для известных устройств

Г„-- 10 (Г,) шах+20 (Гд.) шах-30 (Г J max,

а для предлагаемого устройства 7п 10(Г,.)тах + 3(Г:)(Гх)шах. Если (Га:) тах .)min 1 Тц, то указанный

выигрыш в быстродействии (13с вместо 30с) оказывается весьма существенным. При результирующей точности около 0,01% быстродействие предложенного и известных устройств составят (при тех же условиях) 14 с и 40 с соответственно.

В приведенном примере требования к точности определения ЛЛк невысоки (порядка 1%) и могут быть дополнительно снижены при увеличении Лл-„, однако при этом

уменьшается и выигрыш в быстродействии.

Ф о р м } л а изобретения

1. Преобразователь средней частоты в код, содержащий формирователь основной

последовательности имнульсов и формирователь основного измерительного интервала, выходы которых через ключ соединены с входом счетного регистра старших разрядов выходного кода, генератор опорной

частоты, выход которого подключен к первому входу формирователя дополнительных последовательностей импульсов и к входу формирователя основного измерительного интервала, источник опорного напряжения, счетные регистры, выходы которых подключены к входам управления преобразователей проводимости в напряжение постоянного тока, реализованных, например, на операционном усилителе собратной связью через образцовый резистор, к входу которого подключен кодоуправляемый резистор, и преобразователь напряжения в число-импульсный код, на выходе которого включен счетный регистр младщцх разрядов выходного кода, отличающ и с я тем, что, с целью повышения точности и быстродействия, в него дополнительно введены элементы антисовпадений, элемент равнозначности, счетчик-распределптель импульсов, коммутатор, сумматор

| название | год | авторы | номер документа |

|---|---|---|---|

| МНОГОКАНАЛЬНЫЙ ПРЕОБРАЗОВАТЕЛЬ АНАЛОГОВЫХ СИГНАЛОВ В ИМПУЛЬСНУЮ ПОСЛЕДОВАТЕЛЬНОСТЬ, МОДУЛИРОВАННУЮ ПО ВРЕМЕНИ | 2011 |

|

RU2471287C1 |

| Устройство для определения отношения двух напряжений | 1983 |

|

SU1151994A1 |

| Устройство для поверки цифровых измерителей девиации фазы | 1990 |

|

SU1781651A1 |

| Устройство для решения нелинейных задач теории поля | 1983 |

|

SU1149282A1 |

| Автоматическое устройство для поверки стрелочных электроизмерительных приборов | 1985 |

|

SU1320783A1 |

| Преобразователь активной энергии трехфазной сети в цифровой код | 1986 |

|

SU1363482A1 |

| Умножитель частоты | 1990 |

|

SU1797113A1 |

| Следящий преобразователь угла поворота вала в код | 1983 |

|

SU1116446A1 |

| Корреляционный дискриминатор времени транспортного запаздывания | 1983 |

|

SU1107130A1 |

| Устройство для оценки амплитуды узкополосного случайного процесса | 1987 |

|

SU1499375A1 |

Авторы

Даты

1979-04-30—Публикация

1977-02-07—Подача