1

Изобретение относится к вычислительной технике, в частности, к устройствам приоритетного обслуживания запросов и может быть использовано в системах обработки информации,о

Известно многоканальное устройство приоритета, содержащее элементы И, ИЛИ и НЕ li .

Однако такое устройство характеризуется малым быстродействием, обусловленным задержками сигнала запроса на элементах НЕ, возникновением ложных сигналов на выходах, отсутствием элементов памяти, что требует наличия внешних запоминающих элементов.

Наиболее близким к изобретению по технической сущности и достигаемому результату является многоканальное, устройство приоритета, содержащее в каждом канале триггер, первый и второй элементы И, первый и второй элементы НЕ, причем единичный вход триггера канала является соответствующим запросным входом устройства и соединен с первым входом первого элемента И канала, опросные входы вторых элементов И сое-

динены с опросным входом устройства, выход первого элемента НЕ канала соединен с сигнальным входом второго элемента И канала 2 .

Однако такое устройство характеризует значительная длительность шумов на выходе что приводит к ложному срабатыванию последующих устройств и, следовательно, снижает надежность самого многоканального устройства приоритета. Кроме того, известное устройство требует значительных затрат оборудования.

Цель изобретения - повышение надежвостя и сокращение оборудования.

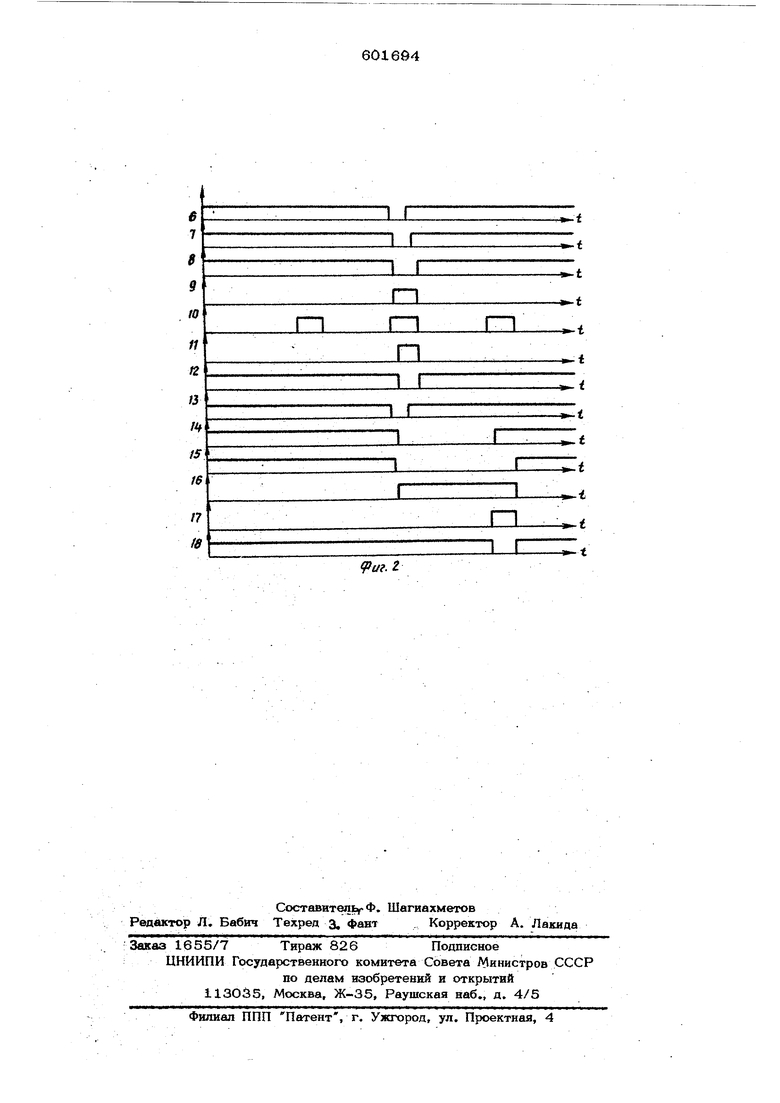

Для этого выход триггера канала соединен со вторым, входом первого элемента И канала, выход первого элемента И канала со входом первого элемента НЕ канала, выход второго элемента И канала через второй элемент НЕ канала соединен с 1Трет ьй1Й входом первого элемента И канала и с,нулевым входом триггера канала, другие сигнальные входы второго элемента И канала соединены с выходами первых элементов И предыдущих, каналов, а выходы вторых элементов и каналов являкхгся вы. ходами устройства. Структурная электрическая схема устройства приведена на фиг. 1, временная диа грамма его работы - на фиг. 2. Многоканальное устройство приоритета содержит в каждом канале (фиг. 1): триггер 1, первый элемент И 2, первый элемент НЕ 3, второй элемент И 4, втоуюй элемент И 4, второй элемент НЕ 5. Позициями 6, 7, 8, 9, 1О, 11 и 12 обозначены вход первого канала, единичшаЗ выход триггера, выходы первого элемента И, первого элемента НЕ, опросный вхрд устройства, выходы второго элемента И, второго элемента НЕ первого канала .соответственно, а яозвииями 13, 14, 15, 16, 17 и 18 обоаначены для второго канала вход и выходы соответствукицих элементов, аналогичных элементам первого канала. Устройство работает следуюпшм образом. Первоначально во всех триггерах 1 записаны нули. На их выходах 7 к 14, а так же на входах 6 и 1.3 и навыходах. 12 и 18 вторых элементов НЕ 5 действуют сигн лы с уровнем логзяческой единицы, совпадение которых на входах алементов И 2 приводит к формированию на их выходах 8 и 15 сигналов также с уровнем логической едйЙицы.| Тпоэтому на всех входах, кроме первого и второго, всех элементов И 4 дей ствуют сипкалы с уровнем лопадеской единицы. На первые входы элементое И 4 подаются сигналы со входа Ю.яИмеюшие уровень логической единицы.. На выхс/дах 9, 16 первых элементов НЕ 3 действуют сигн лы с уровнем логического нуля и сигналы на выходах 11 и 17 вторых элементов И 4 отсутствуют. При поступлении запросов на входы 6 н 13 на первых входах элементов И 2. и на выходах 8Ni 15 устанавливаетса уровен логического нуля, запрещающий формирование выходных сигналов 17 в каналах с : младшим приоритетом. Одновременно посту пившие запросы записываются в триггеры и на их выходах 7 и 14 также устанавлйва ется уровень логического нуля, подтвержда действие сигналов по входам 6 и 13 после окончания входного сигнала до момента его исполнения. Сигналы с уровнем логического нуля на выходах 8 и 15 первых элементов И 2 преобразуются элементами НЕ 3 в сигналы на выходах 9 и 16 с уровнем логической единицы, Теперь при поступлении сигналов по входу 1О на выходе 1.1. канала со старшим приоритетом сформируется сигнал с уровнем логи1еской единицы, который преобразуется элементом НЕ 5 в 60 4 игнал на выходе 12 с уровнем логическоо нуля. Последний переведет триггер 1 в сходное с.х;тояние и установит на его выходе 7 сигнал с уровнем логической едиицы, а|поступая на третий вход элемента 2 поддержит сигнал на выходе 8 на уровне логического нуля до окончания сигнала по входу Ю. Сигнал 17 на выходе второго элемента И 4 канала с младшим приоритетом не изменится, так как до окончания сигнала по входу 1О элемент И 4 заперт сигналом логического нуля с выхода 8 элемента И 2 старшего возбужденного канала. По окончании сигнала на взюде 1О, на входе 8 элемента И 2, на его выходе 8 и на выходах 7 и 12 установятся сигналы с уровнем логической единицы. Очередной сигнал по входу 1О произведет считывание заявки из следующего возбужденного канала. В известном устройстве предусмотрен запрет прямой трансляции заявок на выход устройства в случае, если хотя бы в одном, из триггеров 1 хранится ранее записаннай. заявка. Если же все триггеры 1 находятся Б нулевом СОСТОЯНИЙ, то сигнал запрета прямой трансляции будет сформирован через время, необходимое для записи заявки в триггер { TYU увеличенное на время прог хождения через элемент ИЛИ { t элемент НЕ ( tbAin, ) Если принять, что эти времена через среднее время гзадержки в одном элементе И выражаются- как времГЪадеряйс роваНия сигнала запрета прямой трансляции -«-t t будет равно tj зад.запр. тч .1«нв. . в течение этого времени несколько сигналов, поступивших одновременно на входы устройства приоритета, свободного от ранее поступивших заявок, беспрепятственно и одновременно транслируются на выходы. При этом длительность ложных сигналов на выходах й«жн. зо. Азедпр. достаточна для срабатывания следующих устройств. Кроме того, сигнал Запрета на элементы И 2 каналов с младшим приоритетом после записи зайвок в триггеры 1 также формируется с задерж- кой ijqAsanr HAH- MHB.a3tg,4TO приводит к еще большему увеличению длительности ложных сигналов на выходах известного устройства. В известном устройстве на каждый канал требуется триггеров -1, элементов НЕ - 2, элементов И -3, .элементов ИЛИ - 3, а его структура нерегулярна, что затрудняет реализашпо такого блока в ин.тегральном исполнении. В изобретении время формирования сигнала запрета на каналы с более низким приоритетом определяется задержкой в одном ©лементе И {И 2), т. еД огд-запр ь а время задержки сигнала в также прямой трансляции до входа тех же элементов И 4 определяется элементом И 2 и элементом НЕ3,T.e.t,. , 2 Оледова тельво при одновременном поступлении несколь ких Йадвок; запреты от каналов со старшим приоритетом поступят на входы соответствующих элементов И 4 на ,аА.смгн ior.jatip., раньше чем сами сиг налы, что исключает прохождение на выход уст ройства сигналов с младшим приоритетом. При этом на ОДИН канал изобретения требуется триггеров - 1, элементов НЕ - 2, элементов И - 2, . на четыре функциональных элемента (3 элемента ИЛИ и один элемент И) меньше, чем в известном устройстве, а ре гулярная структура облегчает его реализацию в интегральном исполнении. Таким образом, изобретение по сравнению с известным устройством обладает более высокой надежностью работы за счет отсутствия ложных сигналов на выходе, име ет меньший объем аппаратуры и более пригоден для реализации в. интегральном исполнении. Формула изобретения Т ногоканально, устройство приоритета, содержащее в каждом канале триггер, перЕый И второй элементы И, первый и второй элементы НЕ, причем единичный вход триггера канала является соответствующим запросным входом устройства и соединен с первым входом первого элемента И канала, опросные входы вторых элементов И соединены с опросным входом устройства, выход первого элемента НЕ канала соединен с сигнальным входом второго элемента И канала, отличающееся тем, что, с целью повьш1ения надежности и сокращения оборудования, выход триггера канала соединен со вторым входом первого элемен-. та И канала, выход первого элемента И канала соединен со входом первого элемента НЕ канала, выход второго элемента И канала через .второй элемент НЕ канала соединен с третьим входом первого элемента И канала и с нулевым входом триггера канала, другие сигнальные входы второго элемента И канала соедннены с выходами первых элементов И предыдущих каналов, а выходы вторых элементов И каналов являются выходами устройства. Источники информации, принятые во внимание при экспертизе: 1.Авторское свидетельство СССР кл. GO6F 9/18, № 377775, 1970. 2.Авторское свидетельство СССР, .кл. G06 F 9/18, NO 2О9049, 1968.

| название | год | авторы | номер документа |

|---|---|---|---|

| Многоканальное приоритетное устройство | 1983 |

|

SU1103237A1 |

| МНОГОКАНАЛЬНОЕ УСТРОЙСТВО ДЛЯ ПОДКЛЮЧЕНИЯ АБОНЕНТОВ К ОБЩЕЙ МАГИСТРАЛИ | 2011 |

|

RU2444780C1 |

| Многоканальное устройство приоритета | 1983 |

|

SU1148030A1 |

| Стохастический преобразователь | 1977 |

|

SU734766A1 |

| Многоканальное устройство приоритета | 1989 |

|

SU1644139A2 |

| Устройство для прерывания резервированной вычислительной системы | 1991 |

|

SU1824636A1 |

| Многоканальное устройство для приоритетного подключения источников информации к общей магистрали | 1976 |

|

SU636609A1 |

| Многорежимное устройство приоритета | 1990 |

|

SU1805469A1 |

| Многоканальная система управления распределением ресурсов в вычислительном комплексе | 1987 |

|

SU1432580A1 |

| Многоканальная система управления распределением ресурсов в вычислительном комплексе | 1982 |

|

SU1269142A1 |

10

11

12 /3 / /5 (6

/7 /S

m

n

±JL

.-

u:

n

i-J

Авторы

Даты

1978-04-05—Публикация

1976-01-05—Подача