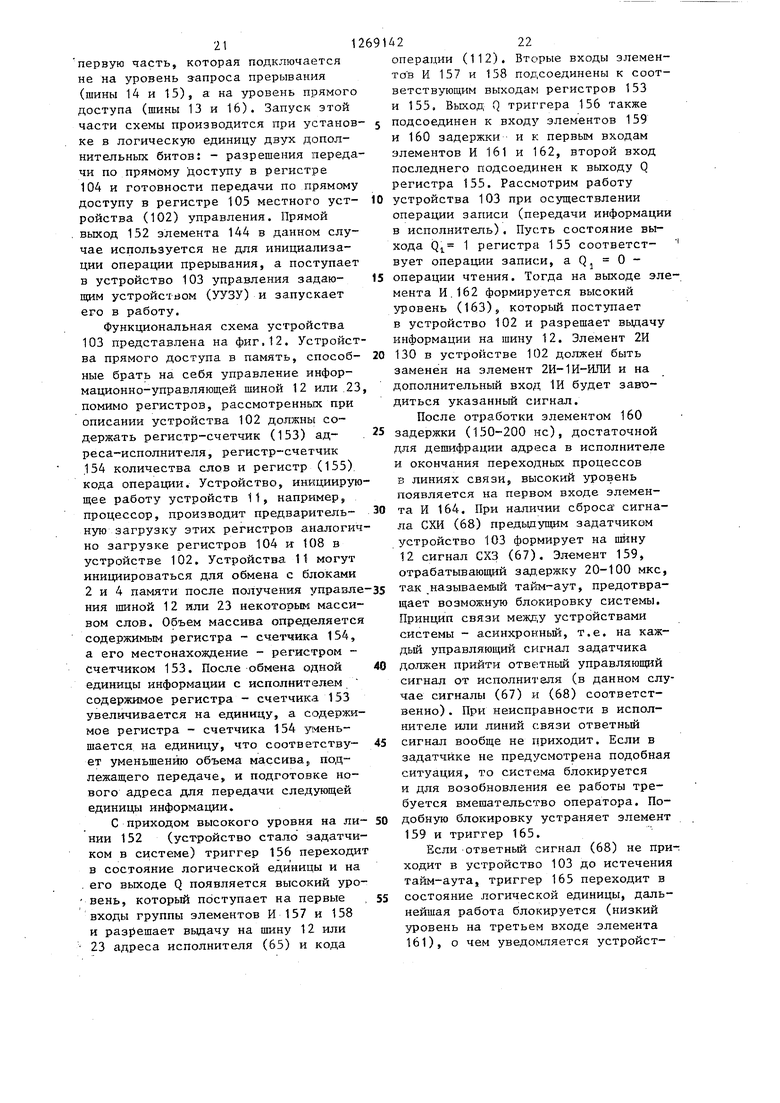

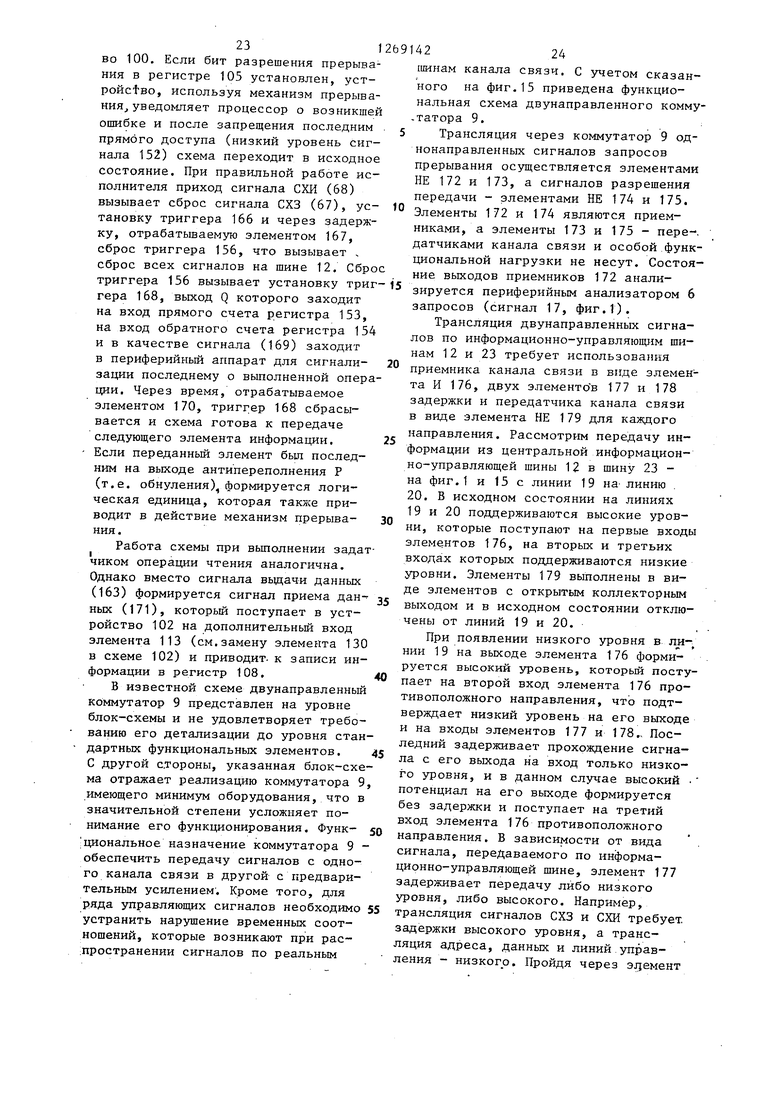

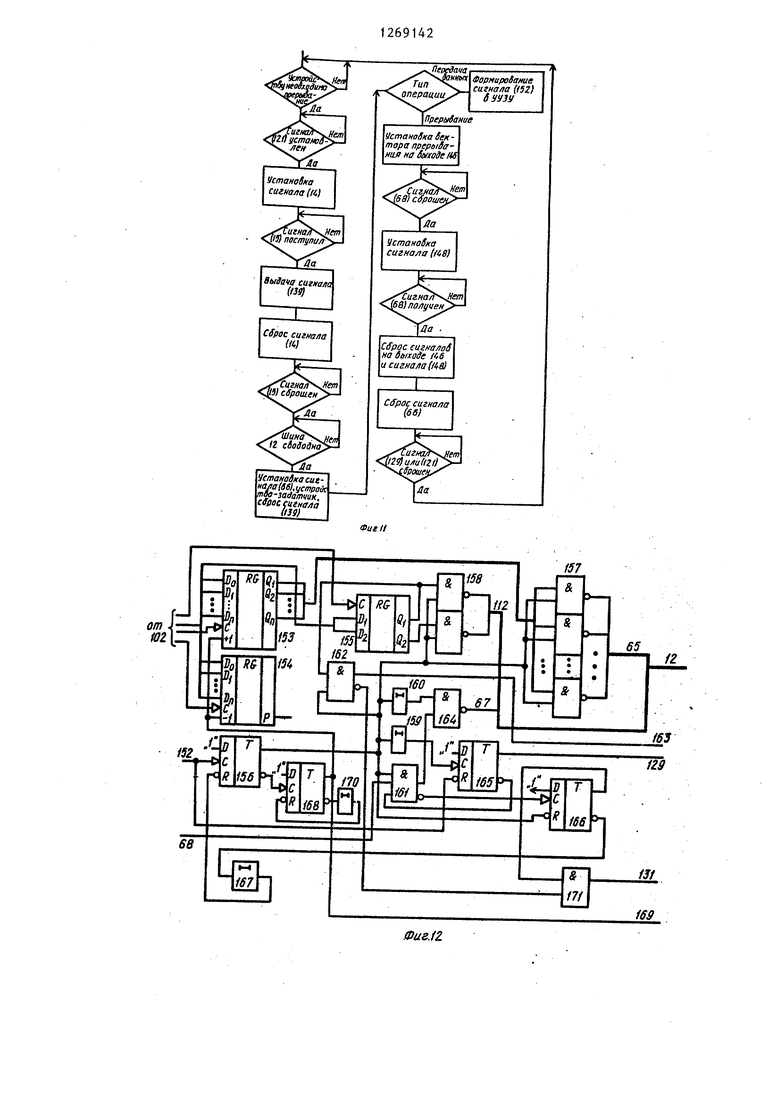

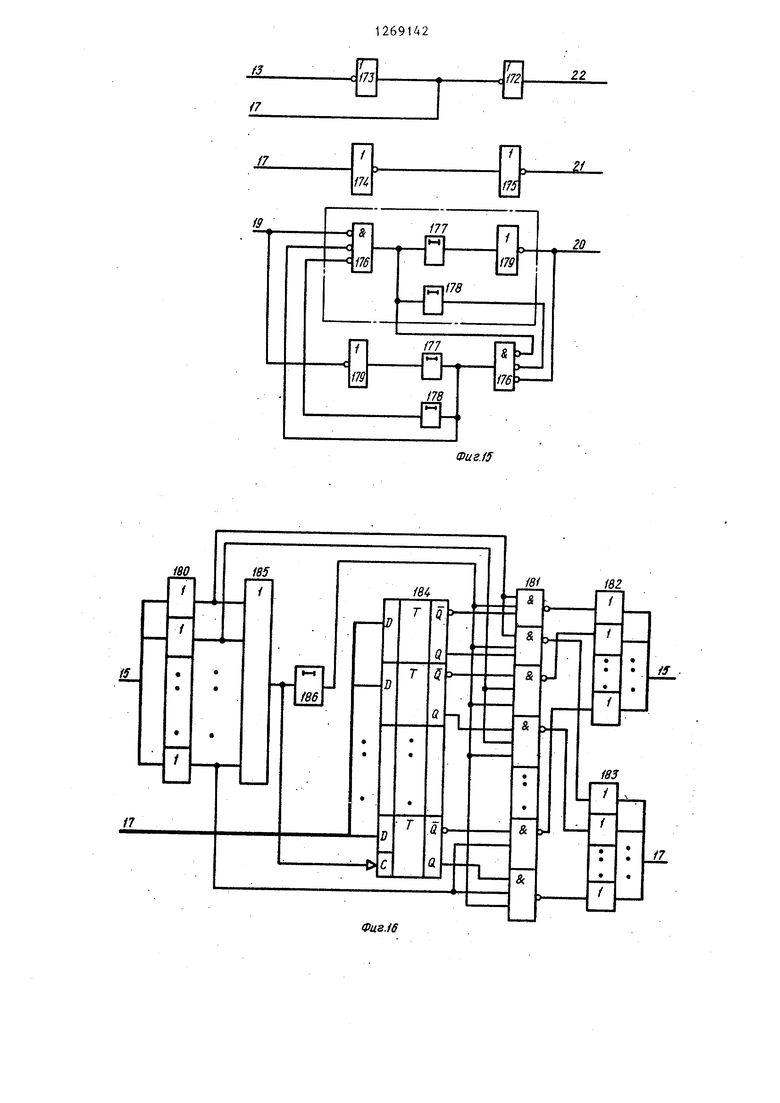

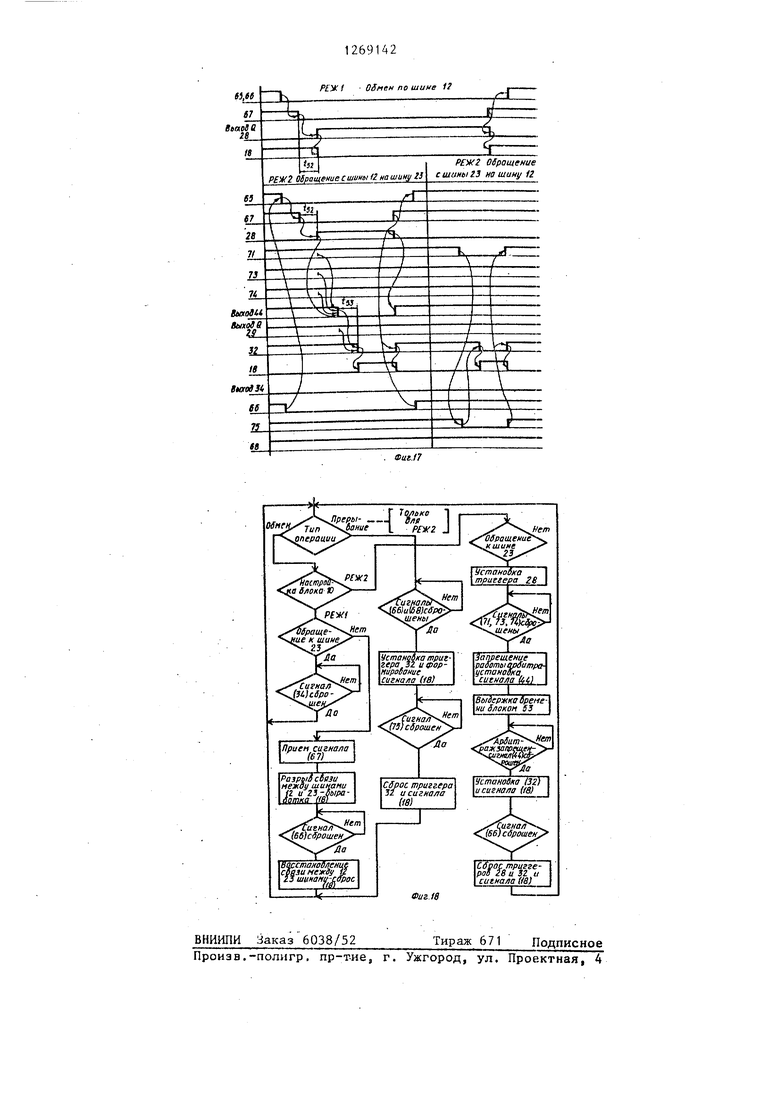

Изобретение относится к вычислительной технике, в частности к сложным цифровым системам обработки данных с множеством быстродействующих устройств ввода-вывода, Цель изобретения - повышение коэф фициента использования оборудования и надежности системы за счет отключения отказавшего канала от других работоспособных каналов, а также повышение производительности вычисли . тельного комплекса (ВК) за счет орга низации параллельной работы многих каналов системы и повышение реактив ности системы прерываний ВК, что спо собствует уменьшению вероятности сбоев в устройствах, критичных к времени доступа к ресурсам. На фиг.1 приведена схема предла-f, гаемой системы; на фиг.2 - функциональная схема блока реконфигурации каждого периферийного канала) .на фиг.3-5 - функциональная схема, временная диаграмма и блок-схема алгоритма работы анализатора запросо центрального канала; на фиг.6 - совмещенные блок-схемы блока памяти, устройства ввода-вывода и устройства прямого доступа; на фиг.7 и 8 функциональная схема и блок-схема алгоритма работы местного устройства управления; на фиг.9-11 - функциональная, схема, временная диаграмма и алгоритм работы устройства управления прерыванием; на фиг.12-14 функциональная схема, временная диаграмма и алгоритм работы устройства управления .задающим устройством; на; фиг.15 - функциональная схема двунаправленного коммутатора; на фиг.16 функциональная схема периферийного анализатора запросов; на фиг. 17 и 18 - временная диаграмма и блок-схема алгоритма работы блока реконфигурации. . Предлагаемая система управления осуществляет распределение ресурсов в вычислительном комплексе, рассре. доточенных по многим каналам - одном центральном и ряде периферийных. К центральномуканалу подключены ан лизатор 1 запросов, блок 2 памяти, группа блоков 3 ввода-вывода, а каж дый периферийньш канал содерзкит блок- 4 памяти, группу блоков 5 ввод вывода, периферийньй анализатор 6 запросов, первый 7 и второй 8 блоки элементов запрета, двунаправленньй коммутатор 9, блок 10 реконфигурации и устройство 11 прямого доступа. Обмен информацией между всеми устройствами и блоками, подсоединенными к центральному каналу, осуществляется по центральной информационно-управляющей шине 12, центральной шине 13 запросов прерывания, центральной шине 14 запросов прямого доступа, центральной шине 15 разрешения прерывания и по центральной шине 16 разрешения прямого доступа. Периферийный анализатор 6 запросов соединен с соответствующим двунаправленным коммутатором 9 двунаправленной шиной 17 запросов-разрешений , а блок 10 реконфигурации - с первым и вторым блоками 7 и 8 элементов запрета шиной 18 запрета, которые, в свою первой 19 и второй 20 информационно-управляющими шинами соединены с двунаправленным коммутатором 9 соответственно, В пределах каждого периферийного канала связь между его элементами осуществляется посредством периферийных шины 21 разрешения прерывания, шины 22 запросов прерывания, информационно-управляющей шины 23j шины 24 разрешения прямого доступа и шины 25 запросов прямого доступа. Блок 10реконфигурации (фиг.2) каждого периферийного канала содержит первую 26 и вторую 27 схемы сравнения, первый 28, второй 29 третий 30, четвертый 31 и пятый 32 триггеры, первый 33, второй 34 и третий 35 переключатели, первый 36 и второй 37 элементы 2И-ШШ, первый 38 второй 39, третий 40, ч :твертьй 41 и пятый 42 элементы ИЛИ; первый 43, второй 44, третий 45, четвертьй 46, пятый 47, шестой 48 и седьмой 49 элементы И, первый 505 второй 51, третий 52, четвертый 53 и пятьй 54 элементы задержки, первьй 55, второй 56, третий 57, четвертый 58, пятьй 59, шестой 60, седьмой 61, восьмой 62, девятьй 63 и десятый 64 элементы НЕ. Из центральной информационно- : управляющей шины 12 в блок 10 реконфигурации поступают следуюшзне сигналы: шина адреса 65; сигнал Занято 66, сигнал Синхронизация от задатчика (СХЗ) 67, сигнал Синхронизация от исполнителя (СХИ) 68 и сигнал Подготовка 69, а из периферийной информационно-управляющей шины 23 -« 3 шина адреса 70, сигнал Занято 71, сигнал СЗХ 72, сигнал СХИ 73, сигна Подтверждение выборки (ИВБ) 74 и сигнал Прерывание 75. Система работает следующим образом. В предлагаемой системе, в отличи от известной, за счет перераспредения всех ресурсов между отдельными каналами возможна одновременная работа нескольких задающих устройств одного на центральном канале и по одному на каждом периферийном канале Системы, Таким образом, количест во одновременно работающих задающих устройств в системе зависит от числа используемых периферийных канало После включения питания машины в централвной информационно-управляющей щине 12 процессором формируется сигнал Подготовка. Эта линия анализируется блоками 3,2 и 10, и появление на ней сигнала вызывает переход указанных блоков в исходное состояние. На щинах 18 запрета блоками 10 реконфигурации формируются высокие уровни, которые, поступая на управляющие входы первых и вторых блоков 7 и 8 запрета, разрешают трансляцию через них сигналов. В результате сигнал Подготовка через блоки 7-9 транслируется в периферийные информационно-управляющие шины 23, переводя устройства периферийных каналов в исходное состояние (4,5 и 11). В исходном состоянии в центральной и периферийных информационно управляющих шинах 12 и 23 и шинах 13,14,22 и 25 запросов передачи поддерживаются высокие уровни (отсутствие сигналов), а в однонаправленных шинах 15,16 21 и 24 разрешения передачи - низкие уровни (отсутствие сиг налов); После некоторого времени, достаточного для перехода в исходное состояние всех устройств системы, процессор снимает сигнал Подготовк и система готова к работе. Сам процессор не принимает участия в перераспределении ресурсов системы с целью организации одновременной работы нескольких задатчиков. Не требуется ни изменение режимов его работы, ни введение в состав программного обеспечения какой-либо программы, организующей такой режим. 424 Цель изобретения достигается введением дополнительной аппаратуры и изменением конфигурации системы. Поэтому сам процессор не входит в состав предлагаемой системы (для понимания работы в структуру системы введен анализатор 1 запросов центрального канала, являющийся его частью) . В рассматриваемой системе принцип связи между устройствами - асинхронньй. В каждый момент времени в системе могут обмениваться информацией только два устройства (в пределах одного канала). Одно устройство управляет передачей информации по каналу связи и является задающим (задатчик), другое устройство, привлекаемое к этой передаче, становится исполнительным устройством (исполнитель) . Каждый задатчик при работе с исполнителем формирует на соответствующей линии информационно-управляющих шин 12 и 23 сигнал Занято, информируя все устройства системы, что канал связи занят. Когда задатчик заканчивает обмен информацией с исполнителем, он сбрасывает сигнал Занято, и одно из устройств системы, имеющее самый высший приоритет в данный момент времени, среди прочих устройств, которым необходим канал связи, становится задатчиком. Задатчик помещает сигнал Занято на шину 12. Содержимое адресного регистра и регистра управления (заранее подготовленные) передаются на :соответствующие линии (шины) 12, а пройдя через блоки 7,9 и 8 - на линии шины 23, поступают на все селекторы адресов устройств системы, в которых фиксируется до начала применения определенный адрес устройства, отличающий его от других устройств системы. Селекторы адресов устройств производят сравнения адреса на шинах 12 и 23 с собственным адресом устройства. Через некоторое время. задатчик формирует на соответствующей линии 12 или 23 сигнал СХЗ. Устройство, адрес которого совпаает с адресом на шине, получает сигал СХЗ и узнает, что оно привлекаетя к передаче в качестве исполнитея. Устройство в соответствии с состоянием линий 12 и 23 управления либо принимает данные из канала связи, либо передает данные в канал связи и через некоторое время; отвечает сигналом СХИ. Задатчик, получая сигнал СХИ, либо сразу сбрасьюает сигнал СХЗ (операция передачи информции из задатчика в исполнитель - запись) , либо принимает данные,, а потом сбрасьшает СХЗ. Через некоторое время задатчик сбрасывает сигналы ад реса, управления и данных (при операции запись) и сигнал Занято,освобождая тем самым канал связи для других устройств. Исполнитель, восприняв сброс сигнала СХЗ,, сбрасывает. сигнал СХИ и Д (при операции чтения), В результате система приходит в исходное состояние. Если на сигнал СЗХ задатчиком не получен сигнал СХИ в течение некоторого времени (тайм-а.ут), то в задатчике фиксируется ошибка и им производится сброс ранее сформированных сигналов.

В предлагаемой системе д.ля организации параллельной работы высокопроизводительного процессора с медленно действующими блоками 3 и 5 вводавьшода и высокоскоростными устройствами 11 прямого доступа используется многоуровневая система прерываний Блоки 3 и 5 запрашивают по пмнам 13 и 22 прерывание работы процессора на обработку информации в своих регистрах. Устройства 11 запрашивают процессор об использовании канала связи. Запросы по шинам 13 и 14 постпают в анализатор 1 запросов, который производит их арбитраж -- выделение наиболее приоритетного .запроса. Устройствам 11 прямого доступа в память, способным выполнить пере дачу информации без использования процессора, присваивается наивысший приоритет - приоритет прямого доступа ,так как они требуют обсл:;щивания за ограниченный интервал времени, в противном случае в них может . происходить потеря информации, подготовленной к передаче. К каждому уровню приоритета может быть подключено достаточно большое (в архитектурном смысле неограниченное) число устройств.

Чтобы анализатор 1 запросов мог выделить из группы устройств, запрашивающих процессор по пшнам 13 и 14 запроса передачи и подключенных к данному уровню приоритета, устройство, имеющее высший приоритет на данном уровне приоритета, в систему вводят однонаправленные шины (линии) 15 и 16, число которых равно числу уровней приоритета. Эти линии последовательно проходят через все устройства, подключенные к данному уровню приоритета, причем, чем ближе в электрической цепи к процессору располагается устройство, тем более высокий приоритет на данном уровне оно имеет. Источником шин разрешения передачи является анализатор 1 запросов центргшьного канала.

Для обеспечения одновременной работы нескольких задатчиков конфигурация предлагаемой системы (состав оборудования) должна быть занесена в блоки 10 реконфигурации. Настройка блока 10 осуществляется до начала применения.

Аппаратный способ настройки блоко 10 реконфигурации предполагает занесение до начала применения в первую 26 и вторую 27 схемы сравнения информации о конфигурации системы. Их настройка производится аналогично настройке селектора адреса любого блока 3 и 5 ввода-вывода или любого устройства 11 прямого доступа. Первая схема 26 сравнения настраивается на адресную зону соответствующего периферийного канала, а схема 27 на адресные зоны центрального и всех других периферийных каналов.

Так же аппаратным способом производится настройка блока 10 реконфигурации Нс1 один из двух режимов. Есл предполагается, что устройство 11 прямого доступа в память, становясь задатчиком, может обращаться к любом устройству системы и к любому блоку оперативного запоминающего устройства, т.е. к зоне адресов всей системы то соответствующий блок 10 настраивается на первый режим работы РЕЖ1. Если же при организации прямого доступа устройством 11 предусматривается обращение только к зоне адресов своего периферийного канала, то блок 10 настраивается на второй режим работы - РЕЖ2.

Рассмотрим функционирование системы в РЕ;Ж1 . После включения питания машины и вьщачи процессором .сигнала Подготовка на шину 12 все устройства системы переходят в исходное состояние. Блоки 10 под дейг ствием сигнала Подготовка удержи вают на своей шине 18 запрета высо кий уровень, разрешая тем самым трансляцию сигналов через блоки 7 и 8 а значит и обмен сигналов меж ду центральной и периферийной инфор мационно-управляющими шинами 12 и Предположим, что устройство 11 запрашивает канал связи, формируя низкий уровень на периферийной шине 25 запросов передачи прямого доступа, который блоком 10 в РЕЖ1 пер дается на централЁную шину 14 запро сов прямого доступа. Низкий уровень распространяясь в шине 14, достигает анализатора 1 запросов, информируя его о том, что одному из уст.ройств 11 требуется канал связи. При соблюдении определенных условий анализатор 1 формирует высокий уровень ответного сигнала на шине 16,который достигает блока 10, находящегося первым к процессору в электрической цепи центральной однонаправленной шины 16 разрешения передачи прямого доступа. Блок 10 анализирует состояние шины 25 и, ес ли пришедший сигнал есть результат реакции анализатора 1 на запрос прямого доступа именно от этого периферийного канала, блок 10 запре щает дальнейшее распространение сиг нала в шине 16 и транслирует его на шину 24. Высокий уровень шины 24 достигае устройства 11, информируя его о том что оно выбрано в качестве будущего задатчика канала связи. Если бы устройство 11 не запрашивало канал связи (высокий уровень шины 25, то блок 10 передал бы высокий уровень линии 16 другому блоку 10 и та до тех пор, пока сигнал шины 16 раз решения передачи прямого доступа не достигнет инициатора сигнала шины 14 aaniiocoB прямого доступа, поступившего в анализатор 1. Устройство 11 в ответ на сигнал 24 сбрасывает сигнал на линии 25, а анализатор Iв ответ сбрасьюает сигнал на линии 16. Когда текущий задатчик освобождает канал связи, устройство I1формирует низкий уровень линии Занято на шине 23 и тем самым становится задатчиком канала связи, Блоками 8,9 и 7 низкий уровень- Занято передается в центральную инфо мационно-управляющую шину 12 и на все шины 23, расположенные после других блоков 7-9. Как и в известной системе пока все ресурсы остаются в распоряжеНИИ только одного задатчика. Предположим, что устройство 11 запрашивало канал связи для обращения к блоку 2 памяти центрального канала. Устройство 11 устанавливает на шину 23 адрес одной из ячеек блока 2 и другую информацию, необходимую для осуществления обмена. Сигналы шины 23 транслируются на шину 12 блоками 8,9 и 7 и одновременно поступают в блок 10. Вторая схема 27 сравнения блока 10, сравнивая адрес на шине 23 с адресами центрального и всех других периферийных каналов, на которые он настроен, и делает вывод, что обращение происходит в зоне адресов чужого канала. Блок 10 оставляет в силе разрешение трансляции сигналов через блоки 8 и 7, и таким образом, устройство 11 продолжает оставаться единственным задатчиком в системе и заканчивает обмен с блоком 2 как описано Bbmie. В данном случае предлагаемая система не дает вьшгрыша по сравнению с известной. Рассмотрим случай, когда устройство 11 запрашивает канал связи для обращения к блоку 4, расположенному на этом же периферийном канале связи. Вторая схема 27 сравнения, анализируя адрес, формируемый устройством 11 на шине 23, обнаруживает факт обращения по адресу, не принадлежащему зоне адресов центрального и всех других периферийных каналов связи. Она формирует на своем выходе низкий уровень. Блок 10 под действием этого сигнала и сигнала СХЗ, которым сопровождается адрес от устройства 115формирует низкий сигнал на шине 18. Блок 7 под действием этого сигнала сбрасьшает на шине 12 все сигналы, которые были ранее переданы на нее с шины 23. В результате с точки зрения уст- ройств центрального и остальных периферийных каналов канал связи становится свободным и может быть использован для других передач. Анализатор 1 запросов производит выборку будущего задатчика одновременно с обменом информацией между устройствами системы. Поэтому к моменту освобождения указанных каналов будущий задатчик подготовлен и с этого момента времени возможна одновременная работа устройства продолжение обмена между устройстBOM 11 и блоком 3 на соответствующем периферийном канале связи, который сейчас логически отключен от других каналов (не обменивается информаи юнно-управляющими сигналами) и начало обмена между новым эадатчиком и новым исполнителем. Если новый задатчик и исполнитель принадлежит одному каналу, то под действием соответствующего блока 10 происходит его логическое отключение от других каналов и т.д. Таким образом может быть организована одновременная работа нескольких пар устройств.

Устройство 11, заканчивая обмен информацией с блоком 4, снимает сигнал Занято с шины 23, что вызывает сня.тие блоком 10 низкого сигнала на его шине 18. В результате логическая связь данного кансша с другими каналами восстанавливается и система переходит в исходное состояние .

При указанной организации одновр менной работы нескольких задатчиков каждое устройство системы, становясь задатчиком в начале обмена, на какое-то время все-таки монополизи:рует все средства системы. Поэтому практически таким способом можно организовать одновременную работу только пяти-шести задатчиков, Как и в известной системе 1 при большой длине очереди, организуемой анализатором 1, время ожидания все-таки может быть велико. Указанные недостатки можно устранить, если прямой доступ устройств 11 организуется только в зоне адресов .своего периферийного канала связи, т.е. устройство 11, становясь задатчиком обращается только к блоку 4 своего канала. Практически это условие .вьшолняется загрузкой программ, под управлением которьгх работает ydTройство 11, в блок 4 памяти., расположенный в этом же канале. Это дает возможность настроить блок 10 в РЕЖ2- до начала применения.

В этом режиме сразу же после включения питания машины логическая связь между шинами 12 и 23 исключена под действием низкого уровня на выходной шине 18 блока 10 и запрещена трансляция сигналов между шинами 25 и 14. В этом случае арбитраж на уровне прямого доступа для устройств 11 производится не анализатором 1, а блоком 10 реконфигурации.

Обращение задатчика центрального канала к устройствам периферийного канала происходит следующим образом Задатчик помещает на шину 12 адрес одного из устройств периферийного канала и сопровоя цает его сигналом СХЗ. Первая схема 26 сравнения опознает факт обращения задатчика центрального канала к исполнителю периферийного канала. При этом блок 10 реконфигурации ожидает приход сигнала СХЗ с шины 12, анализирует состояние периферийного канала и, если он свободен, восстанавливает логическую связь между шинами 12 и 23. Таким образом происходит обращение задатчика центрального канала к исполнителю периферийного канала после завершения которого, блок 10 вновь исключает связь между-шинами 12 и 23. Устройство 11 при н еобходи мости организации прямого доступа устанавливает низкий уровень на шине 25. Блок 10 реконфигурации, если нет обращения к периферийному каналу со стороны устройств центральног канала, отвечает формированием высокого уровня на шине 24. В результате время предоставления ресурсов периферийного канала устройству 11 значительно сокращается. Во время работы устройства 11 им монополизируются только ресурсы соответствующего периферийного канала.

Если одному из блоков 5 периферийного канала требуется прервать работу процессора, то он помещает низкий уровень на шину 22, который транслируется через коммутатор 9, независимо от состояния блока 10. Сигнал разрешения передачи, формируемый анализатором 1 запросов центрального канала, на шину 15 проходи через блоки 3 и, если среди них не бьшо устройства, требующего прерывания, через анализатор 6 запросов и коммутатор 9 и достигает блока 5 по шине 21. Когда блок 5 становится задатчиком, ок формирует на шине 23 сигнал Прерывание, под действи11

ем которого блок 10 восстанавливает логическую связь между шинами 12 и 23. После завершения операции прерьшания логическая связь между шинами 12 и 23 разрывается,

Во втором режиме число одновремено работающих задатчиков практическ неограничено и лимитируется не пропускной способностью канала связи, а общей суммарной емкостью блоков 2 и 4 в соответствии с разрядностью адресной .сетки.

Предлагаемая система позволяет не только рационально использовать ресурсы, но и в случае настройки бл ков реконфигурации в РЕЖ2 позволяет существенно повысить надежность работы однопроцессорного комплекса. Повьшенная защищенность системы от катастрофического отказа обусловливаётся наличием логических разрядов между центральным и периферийными каналами в исходном Состоянии. В известной системе неисправность, возникающая в одном из каналов, автоматически проявляется (транслируется) и во всех других каналах, в результате чего работоспособность всей системы нарушается. В предлагаемой системе неисправность локали зуется только в пределах того канала, где она возникает, не нарушая работоспособность всех других каналов. Попытки обращений устройств задатчиков исправных каналов к исполнителям неисправных каналов могут привести либо к срабатыванию механизма тайм-аута, либо к фиксации устойчивого отказа. И в том, и в другом случае задатчик информирует анализатор 1 запросов, используя операцию Прерывание, в результате выполнения которой их обращени к устройствам отказавшего канала может быть запрещено.

Таким образом, достигается повьш1ение производительности однопроцессорного комплекса и увеличение его надежности. Степень детализации устройств в предлагаемой системе по костью соответствует степени их детализации в известной.

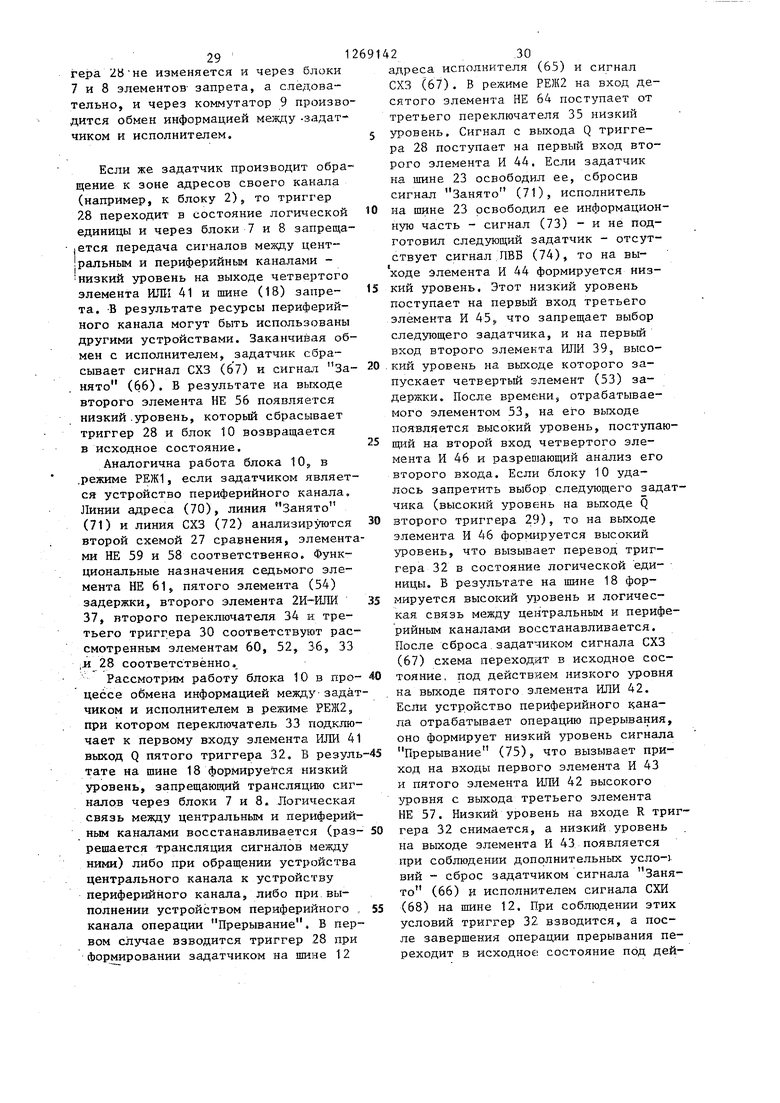

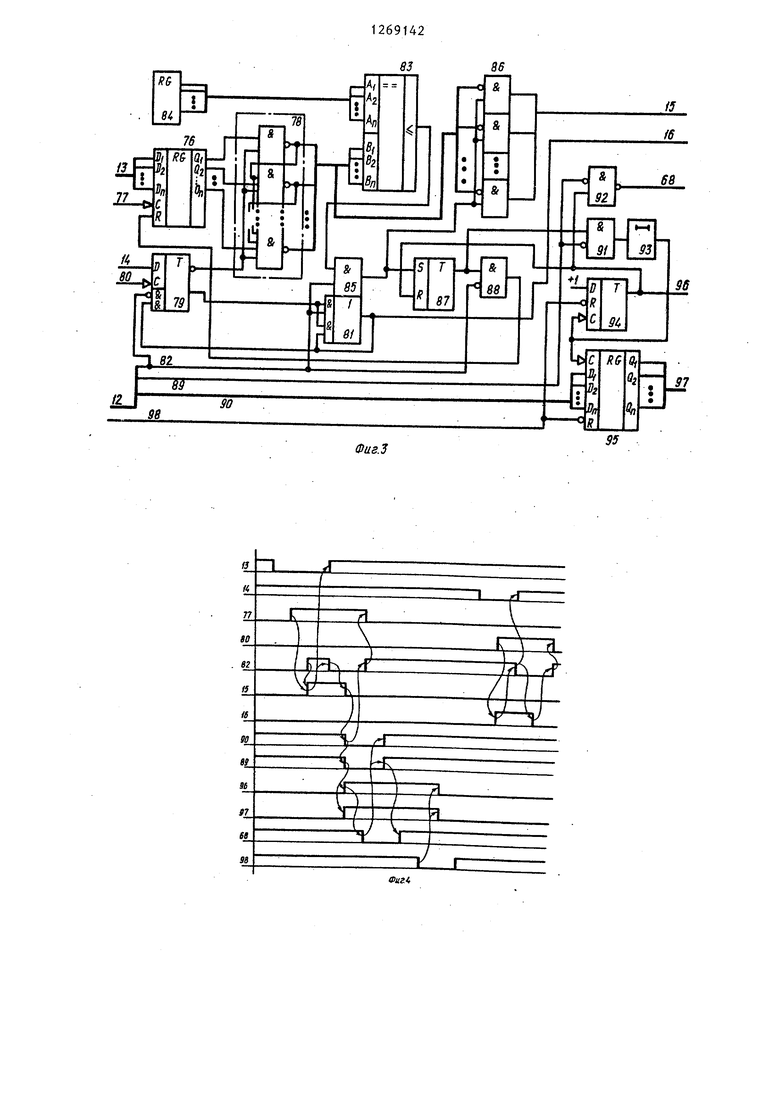

Функциональная схема анализатора 1, запросов центрального канала (фиг.З) является частью процессора, Сигналы-центральной шины 13 запросо передачи поступают на входы В,- В„ регистра 76 запросов прерьшаний.

142J2

С приходом строба опроса сигналов запросов передачи (77) от процессора состояние шины 13 фиксируется :в регистре 76, выходы которого подсоединены к схеме 78 сравнения, преставляющей собой схему выбора наиболее приоритетного запроса и выполненную на элементах И-НЕ. Все схмы И-НЕ подсоединены к выходу триггра 79, фиксирующего состояние центральной шины 14 запросов передачи прямого доступа (ЗЩО в момент прихода от процессора строба запроса передачи прямого доступа (80). Цепи и злементы, способствующие переводу анализатора 1 в исходное состояние при включении питания не показаны. В реальном арбитре эта процедура осуществляется под действием сигнала Подготовка в шине 12. При дальнейшем рассмотрении работы анализатора 1 предполагается, что его триггеры и регистры в исходном состоянии сброшены.

Рассмотрим работу анализатора 1 запросов в режиме арбитража по прямому доступу. С приходом строба опроса ЗДЦ (80) и при наличии сигнала в шине 14 триггер 79 переходит в сотояние логической единицы. Низкий уровень на выходе Q триггера 79 блокирует работу схемы 78 сравнения а сигнал с выхода Q поступает на первый вход элемента И-ИЛИ 81 и при отсутствии сигнала ПВБ (82) в центральной информационно-управляющей шине 12 формируется в шине 16 высокий уровень. В ответ на этот сигнал устройство (источник сигнала ЗДЦ) снимает сигнал на шине 14 и подтверлщает принятие сигнала с шины 16 формированием низкого уровня сигнала (82) Анализатор 1 запросов в ответ снимает высокий уровень в центральной шине 16 разрешения прямого доступа, в результате схема возвращается в исходное состояние.

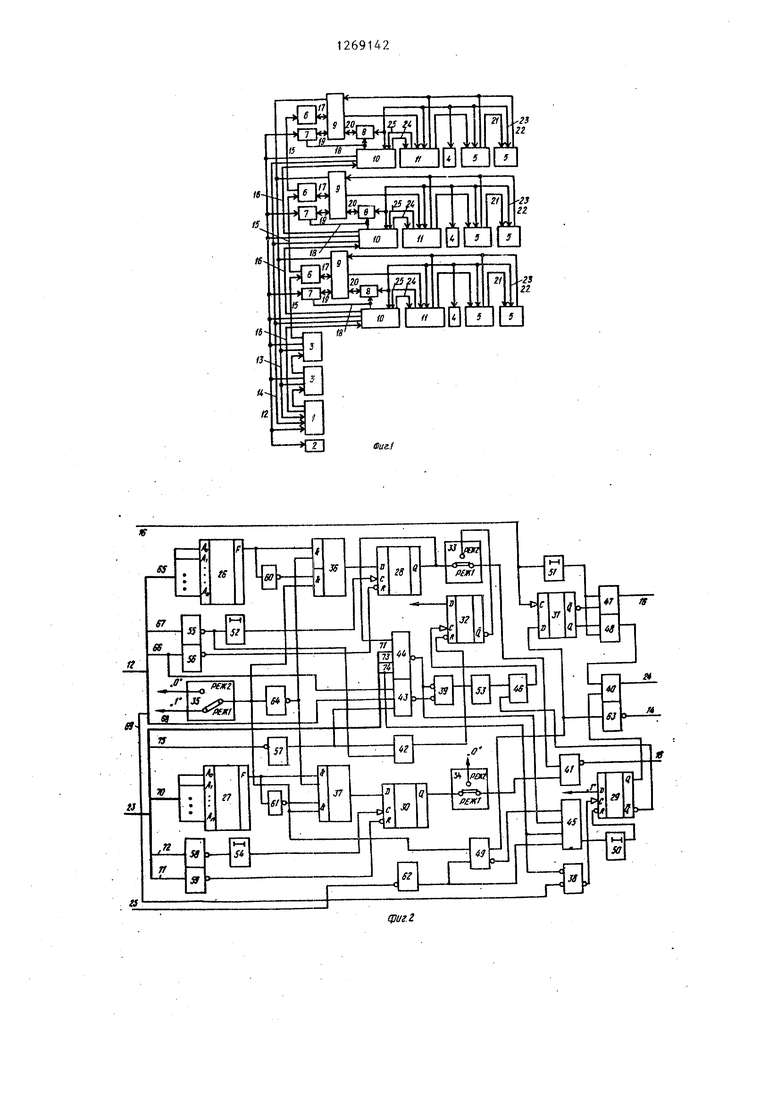

Рассмотрим процедуру арбитража для сигналов центральной шины 13 запросов передачи (ЗП). С приходом от процессора строба опроса ЗП (77) в регистр- 76 записывается состояние шины 13. Если схема 78 сравнения не блокирована триггером 79, то на одном из ее выходов, соответствующем наиболее приоритетному запросу на шине 13 в данный момент времени, формируется низкий уровень (логичес1312кая единица). Выходы схемы 78 сравнения соединены с второй группой входов компаратора 83, первая группа входов которого соединена с выходами разрядов регистра 84 команд и состоя НИИ процессора, в которых фиксируется приоритет программы, выполняемой процессором в текущий момент времени Компаратор 83 сравнивает приоритет процессора с наиболее приорите тным запросом гаины 13, Если приоритет про цессора ниже приоритета запрашивающего устройства, на выходе компаратора 83 формируется высокий уровень, который поступает на первьй вход схе мы И- 85. При отсутствии сигнала ПВБ (82) на выходе схемы И 85 появляет ся высокий уровень, который поступае на вторые входы схем 86 и на вход триггера 87. В результате триггер 87 переходит в состояние логической единицы, а на одном из выходов схем 86, соо.тветствующем наиболее приоритетному запросу, появляется высокий уровень, который поступает в шину 15 Устройство-источник соответствующего сигнала ЗП в ответ на приход сигнала разрешения передачи формирует в шине 12 сигнал ПВБ (82), который S центральном анализаторе поступает на второй вход схемы И 88, что приводит к появлению на ее выходе высокого уровня. В результате регистр 70 переходит в исходное состояние, а сигнал на центральной шине 15 разрешения передачи сбрасывается. Когда устройство - источник запроса становится задатчиком в системе, оно формирует на центральной информацронно-управляющей шине 12 сигнал Прерывание (89) и информацию на шине 9.0 данных. Сигнал (89) поступает на первые входы схем И 91 и 92 и через вре 1мя, отрабатьюаемое элементом. 93 задержки, высокий уровень поступает на управляющие входы триггера 94 и регистра 95, Триггер 94 фиксирует факт прихода сигнала Прерывание (89), а регистр 95 запоминает содержимое линий 90 данных в центральной информационно-управляющей шине 12« Устрой ство-задатчик по линиям 90 передает информацию, однозначно опред(гляю1цую устройство-источник прерывания. Выдержка времени элементом 92 необходима для завершения переходных процессов в канале и записи в регистр 95 достоверной информации. 2 Высокий уровень выхода триггера 94 вызывает сброс триггера 87 и формирование в шине 12 сигнала СХИ (68). После прихода в анализатор 1 запросов сброса сигнала (89) сигнал (68) также сбрасывается. На этом процедура арбитража и операция Прерывание в канале связи заканчивается. Информация о факте прерывания (96) и об источнике прерывания (97) поступает в процессор, который после ее обработки сбрасьтает триггер 94 и регистр -(95) сигналом (98), и схема возвращается в исходное состояние. В предлагаемой системе любому ее устройству (блок памяти, устройство ввода-вывода или устройство прямого доступа) присваивается определенный адрес, который позволяет отличать данное устройство от всех других устройств системы. Во всех устройствах системы имеется специальный блок, вьшолняющий функции опознавания своего адреса - схема 99 сравнения (фиг.6). В системе с одной магистралью в любой операции обмена информацией всегда участвуют два устройства, связанные между собой как задатчик (управляющее устройство) и исполнитель (управляемое устройство). В известной системе одновременно двух и более работающих на магистрали устройств быть не может. Все другие устройства, которым требуется магистраль для обмена, информируют об этом анализатор 1 запросов центрального канала по шинам запроса г ередачи. , Часть устройства, ответственная за формирование сигналов запросов передачи и обмена сигналами с анализатором 1 вплоть до того момента, когда устройство становится задатчиком, является устройством 100 управления прерыванием. Устройство вводавывода запрашивает канал связи только для уведомления процессора о завершении устройством операции, инициированной ранее процессором, или об об-, наруженной. ошибке в процессе операции. . Принцип связи между устройствами системы - асинхронный, что позволяет участвоват.ъ в обмене устройствами различного быстродействия. Однако, чтобы не занимать единственную магистраль надолго, каждое устройство имеет не менее одного буферного ре-15гистра 101 данных для быстрого прие ма и выдачи данных. Б ЭВМ с магистральной структурой управление устройствами выполняется с помощью адресуемых регистров устpoйctвa, отдельные разряды которых осуществляют требуемые операции управления. Эти регистры входят в сос тав местного устройства (102) управ ления, которое осуществляет выбор одного из регистров устройства, про изводит запись или считывание инфор мации в буферные регистры 101, а также инициирует ту или иную операцию в исполнительном механизме (пер ферийный аппарат). Устройства прямого доступа в память, кроме указанных операций, могут запрашивать шину для обмена информацией с оперативной памятью или любым другим устройством без помощи процессора. Эти устройства способны функционировать в режиме задатчика, т.е. имеют возможность управлять этим обменом самостоятельно. Эти функции ос5пцествляются устройством (103) управления задатчика. Блоки оперативных запоминающих устройств, кроме указанных функциональных частей, содержат запоминающую среду, состоящую из взаимо связанных запоминающих элементов. Уровень детализации функциональных частей блоков 2 и 4, за исключением схемы (99) сравнения, соответствует уровню стандартных функци нальных элементов и не требует даль нейшей конкретизации. Местное устройство (102) управления здесь выполняет роль дешифратора кодов операции, из которых основньми являются операции чтения и записи. Функции запоминающих устройств ограниче ны исключительно хранением информации в запоминающей среде. Схема (99) сравнения является распространенным функциональным зле ментом, который представляет собой .адресный дешифратор с усеченным числом выходов, в данном случае одним. Схема сравнения может быть выполнена различными способами, в частности схема сравнения блоков 3 и 5 ввода-вьшода устройств прямого доступа может быть выполнена на основе одноразрядного постоянного запоминающего устройства, адресные входы которого соединяются с адрес42 16 ными линиями информационно-управляющей шины. До начала применения логическая единица заносится аппаратно (путем прожига плавких перемычек в постоянном запоминающем устройстве) только в те ячейки, которые соответствуют адресу, выделенному для данного устройства. При этом логическая единица на выходе схемы 99 сравнения будет иметь место только при совпадении адреса, зафиксированного аппаратным путем, с адресом, пришедшим по информационно-управляющей шине 12. Функциональная схема местного устройства 102 управления представлена на фиг.7. После включения питания машины в информационно-управляющей шине 12 появляется сигнал Подготовка (69), переводящий все уст-ройства системы в исх 3й;-ное состояние. В местном устройстве (102) управления сигнал (69) заводится на установочные входы R регистра (104) команд и регистра (105) состояний, а также на первый вход схемы ИЛИ 106, выход которой подсоединен к установочному входу К триггера 107. В исходном состоянии указанные регистры и триггер сброшены. В предлагаемой системе управление работой устройства ввода-вывода осуществляется с помощью адресуемых регистров, в данном случае регистра 104. Установка в логическую единицуотдельных битов этого регистра возбуждает ту или иную операцию в устройстве. Такими операциями могут быть перемотка ленты, установка головки в исходное состояние, возврат каретки и другие, специфические для каждого устройства операции. Ряб битов имеет универсальное значение для всех устройств системы, например бит разрешения прерывания, бит запуска операции чтения (выводы информации из данного устройства), бит запуска операции записи и др. Рассмотрим операцию записи информации в устройство ввода-вьшода, которая представляет собой запись требуемой информации в буферный регистр 108 и установку бита запуска операции записи в регистре 104. Доступ к указанным регистрам может быть разрешен при совпадении логических единиц на входах схемы И 109. Первьй вход схемы И 109 соединен с выходом схемы (99) сравнения, второй вход - с сигналом синхронизации задатчика (67) в гаине 12, а третий с выходом Q триггера 107,, Если устройство свободно, адрес на шине 12 совпадает с адресом устройства (старшие значащие разряды адресньос линий) и приходит управляющий сигнал от задатчика, на выходе схемы И 109 появляется высокий уровень. Последний поступает на управляющие входы дешифратора (110) регистра и дешифратора 111 кода операции. Первый производит декодирование младших значащих разрядов адресных линий 65 и вБ1бор одного из регистров устройства, а второй - декодирование операции, затребованной задатчиком и определяемой линиями (112) управления в шине 12,

В рассматриваемом случае выход Вд дешифратора 110 соответствует регистру 108, а выход регистру 104. Аналогично выход BQ дешифратора 111 соответствует операции записи, а выход В, - операции чтения. При организации записи в регистр 108 на выходах БО дешифраторов 110 и 111 появляются высокие уровни и, как следствие, на выходе элемента И 113. С выхода элемента И 113 высокий уровень поступает на адресный вход А мультиплексора 114 и на вход элемента (115), задержки. Мультиплексор 114 настраивается на прием с шины 12 и п редает состояние линий данных (116) на вход буферного регистра 108. Чере некоторое время, отрабатьгааемое элементом 115 и достаточное для установки достоверной информации на информационных входах регистра 108, высокий уровень передается через элемент ИЛИ 117 и производит запись информации в регистр 108 по динамическому управляющему входу. Сигналы с выходов регистра 108 поступают на соответствующие первые входы элементов И 118, а также в периферийный аппарат 119, Аналогично производится запись в регистр 104 при формироваНИИ высокого уровня на выходе элемента И 120.

Сигналы с выходов Q регистра 104 поступают в периферийньл ацпарат 121.и возбуждают, спецнфичную для каждого устройства операцию, затребованную задатчиком. Сигнал с выхода схемы И 5 109 возбуждает элемент

(122) задержки, время срабатывания которого выбирается с учетом максимального времени выполнения операции чтения или записи, поСле истечения которого низкий уровень поступает на линию СХИ (68) шины 12 и через элемент НЕ 123 на управляющий вход триггера 107, что вызывает переход устройства в состояние Занято (установка триггера 107)« В ответ на сигнал (68) задатчик сбрасывает сигнал СХЗ (67), который вызывает сброс сигнала СХИ (68). Сбросом сигнала (68) заканчивается обмен информацией между задатчиком и исполнителем по шине 12. Установка триггера 107 вызывает блокировку устройства, т.е. запрещаются повторные обращения к устройству, вплоть до тех пор, пока устройство не выполнит операцию, затребованную задатчиком. Результат выполнения операции (124) заносится периферийным аппаратом в регистр 105 по сигналу (125) и устройство переходит в состояние Свободно - сброс триггера 107 по сигналу (126).

Возможны следующие результаты выполнения операции: устройство успешно завершило операцию, устройство не может выполнить операцию (не подключен носитель информации, на периферийном аппарате нет питания и т.д.) или в процессе вьшолнения операции была обнаружена ошибка. О результате выполнения операции задатчик может узнать двугуш способами. Можно произвести операцию чтения состояния регистра 105 посредством элементов И 127 и 128, после того как устройство перейдет в состояние Свободно. Второй способ заключается в использовании механизма прерывания. Состояния бита разревгения прерьшания (121) и битов завершения операции (129) анализируются устройством (100) управления прерьшанием. Считывание состояния буферного регистра 108 производится посредством элементов 130 и 118, запись в него информации (124) при инициативе периферийного аппарата производится под действием стробирующего сигнала (131).

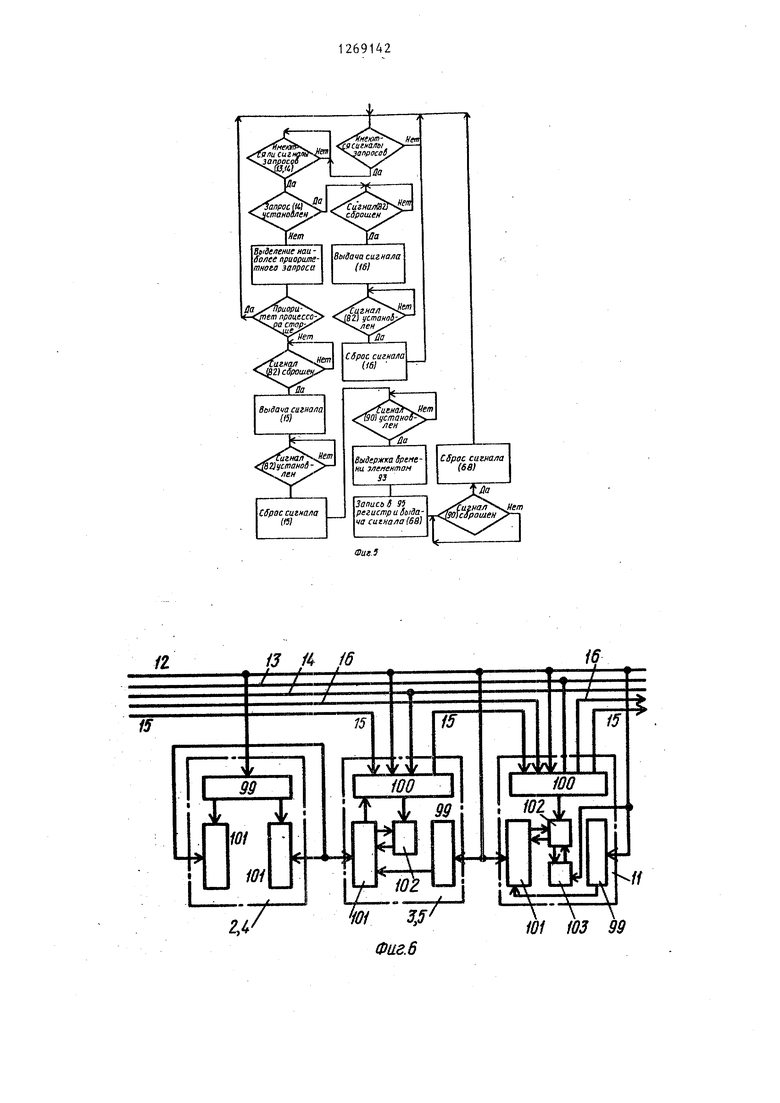

Устройство 100 управления прерыванием функционирует следующим образом (фиг.9-11). В исходном состоянии триггеры 132 и 133 сброшены. (Устройство (100) управления запускает,ся в работу при совпадении высоких 19 уровней на входах схемы И 134, первый вход которой .соединен с битом разрешения прерываний (121) местног устройства (102) управления, а второй вход - с выходом элемента Ю1И 135.На входы последнего приходят сигналы-(129) с вьпсодов регистра (105) состояний (установка которых говорит о факте завершения операции При совпадении этих условий элементом И 136 формируется низкий уровен на шине (14) запросов передачи. При ход от анализатора (1) запросов высокого уровня по центральной шине (15) разрешения прерывания приводит к установке триггера 132. Высокий ; уровень с выхода триггера 132 поступает на первый вход схемы ИЛИ-НЕ 137, что вызывает сброс сигнала на шине 14, на первый вход схемы , И-НЕ 138, что вызывает формирование сигнала ПВБ (139) в шине 12, и на первьй вход схемы И-НЕ 140, в резуль тате чего на ее выходе появляется низкий уровень. Этот низкий уровень поступает на первый вход элемента И i141 и подтверждает низкий уровень на его выходе, и через время, отрабатываемое элементом (142) задерж:ки, высокий уровень появляется на втором входе элемента И 141. Сигнал разрешения прерывания (15), источником которого является анализатор (1) запросов, последовательно проходит через все устройства системы, 1подключенные к данному уровню приори тета. Этот сигнал, поступая на вход первого устройства 3 или 11, подвергается анализу и в случае требования устройством обслуживания ему да,ется право пользоваться ресурсами системы (рассматриваемый случай), в противном случае сигнал разрешения прерывания поступает на продолжение центральной шины разрешения прерьшания (выход элемента И 141). Анализатор 1 запросов в ответ на сигнал ПВБ (139) сбрасывает сигнал на шине 15. Элемент И 143 отслеживает освобождение шины предьздущим задатчиком (сброс уровня на линии Занято 66)и сброс сигн ла (15) анализатором 1. При совпадении этих условий на выходе элемента И 143 формируется высокий уровень и триггер 133 переходит в соетояние логической единицы. В результате, сигнал ПВВ (139) сбрасьшается, 42 Занято сигнал Занято (66) устанавливается и устройство становится задатчиком. Высокий уровень на прямом выходе элемента И 144 поступает на первый вход элемента И 145 и на первые входы группы элементов И 146. Вторые входы элементов И 146 подсоединены к наборному полю вектора прерывания (147), перемычками которого распаивается адрес вектора прерывания дан ного устройства. Векторы прерывания по линиям данных (116) шины 12 поступают в анализатор 1 запросов и являются идентификатором устройства - источника прерывания. : При наличии сброса сигнала СХИ (68) от предьиущего исполнителя устройство 100 управления прерыванием сопровождает вектор прерывания сигналом прерывания (148). Анализатор 1 отвечает сигналом СХИ (68), под действием которого на выходе элемента И 149 формируется высокий уровень, на выходе элемента ИЛИ 150 низкий уровень и триггер (132) переходит в исходное состояние, В результате сигналы (66), (116) и (148) сбрасываются, что является окончанием операции Прерьшание по каналу связи. Устройство 100 управления находится в промежуточном состоянии (триггер 133 взведен), при котором сигналы на шины канала связи не формируются и сигналы по центральной шине (15) разрешения прерывания транслируются через устройство 100 без изменения его состояния (за счет элемента И 151). Перевод устройства 100 в исходное состояние может быть произведен только после сброса либо сигнала (121), либо (129), т,е, или после запрета разрешения прерьшания или после устранения причины прерывания. Устройство 100 управления прерыванием (УУП) функционально можно разбить на две части. Первая часть отрабатывает процедуру получения права использовать ресурсы системы (т.е, процедуру становления-устройством - задатчиком на шине), а вторая часть - собственно процедуру операции Прерывание. Устройство улравения прерыванием устройств 11 прямого доступа в память полностью включает УУП 100 блоков 3 или 5 вода-вывода плюс дополнительно его

первую часть, которая подключается не на уровень з-апроса прерывания (шины 14 и 15), а на уровень прямого доступа (шины 13 и 16). Запуск этой части схемы производится при установ ке в логическую единицу двух дополнительных битов: - разрешения передачи по прямому доступу в регистре 104 и готовности передачи по прямому доступу в регистре 105 местного устройства (102) управления. Прямой выход 152 элемента 144 в данном случае используется не для инициализации операции прерывания, а поступает в устройство 103 управления задающим устройством (УУЗУ) и запускает его в работу.

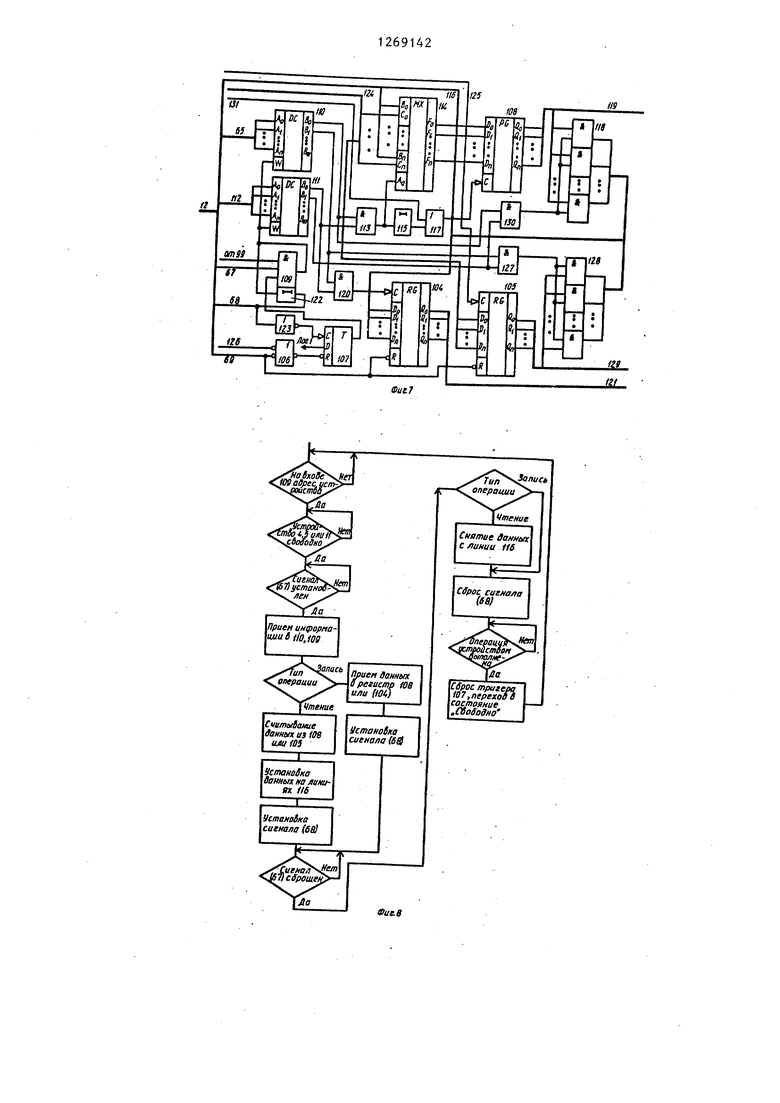

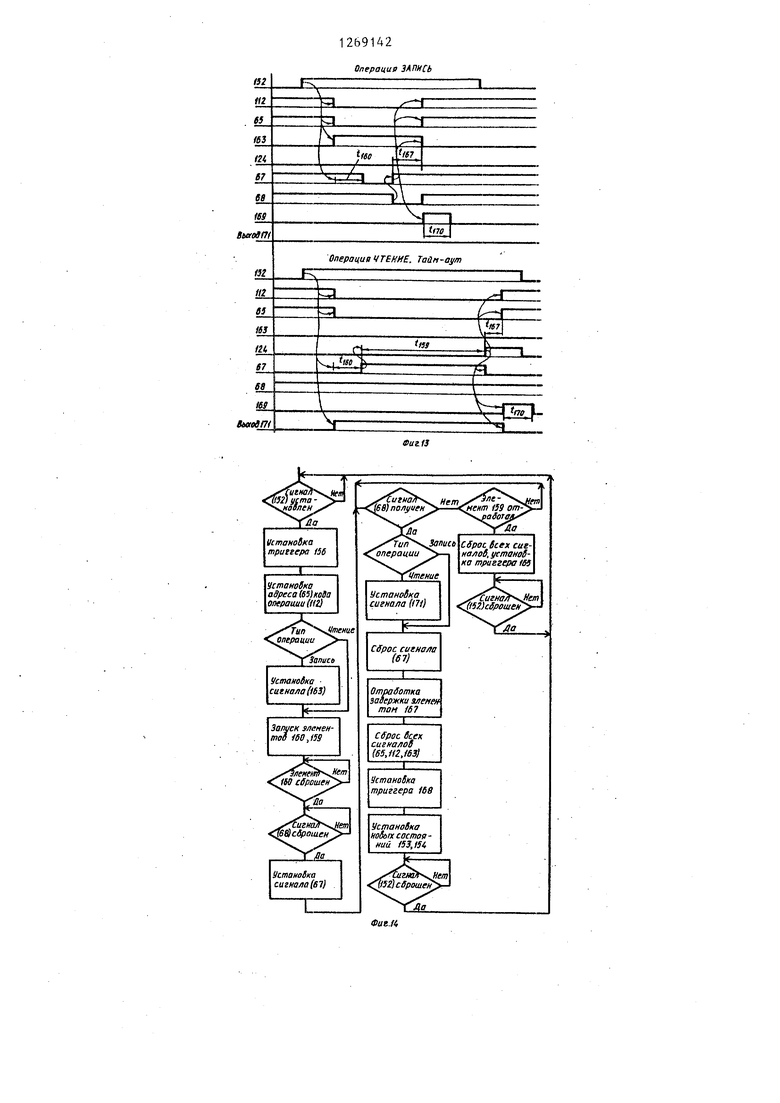

Функциональная схема устройства 103 представлена на фиг,12. Устройства прямого доступа в память, способные брать на себя управление информационно-управляющей шиной 12 или .23 помимо регистров, рассмотренньш при описании устройства 102 должны содержать регистр-счетчик (153) адреса-исполнителя, регистр-счетчик .154 количества слов и регистр (155) кода операции. Устройство, инициирующее работу устройств 11, например, процессор, производит предварительную загрузку этих регистров аналогично загрузке регистров 104 и 108 в устройстве 102, Устройства 11 могут инициироваться для обмена с блоками 2 и 4 памяти после получения управле кия шиной 12 или 23 некоторым массивом слов. Объем массива определяется содержимым регистра - счетчика 154, а его местонахождение - регистром счетчиком 153. После обмена одной единицы информации с исполнителем содержимое регистра - счетчика 153 увеличивается на единицу, а содержимое регистра - счетчика 154 у1меньшается на единицу, что соответству- ет уменьшению объема массива, подлежащего передаче, и подготовке нового адреса для передачи следующей единицы информации.

С приходом высокого уровня на лиНИИ 152 (устройство стало задатчиком в системе) триггер 156 переходит в состояние логической единицы и на . его выходе Q появляется высокий уро вень, который поступает на первые входы группы элементов И 157 и 158 и разрешает вьщачу на шину 12 или 23 адреса исполнителя (65) и кода

операции (112). Втсфые входы элементов И 157 и 158 подсоединены к соответствующим выходам регистров 153 и 155. Выход Q триггера 156 также подсоединен к входу элементов 159 и 160 задержки и к первым входам элементов И 161 и 162, второй вход последнего подсоединен к выходу Q регистра 155. Рассмотрим работу устройства 103 при осуществлении операции записи (передачи информации в исполнитель), Пусть состояние выхода Q 1 регистра 155 соответствует операции записи, а Qj О - операции чтения. Тогда на выходе элемента И.162 формируется высокий уровень (163), который поступает в устройство 102 и разрешает выдачу информации на шину 12. Элемент 2И 130 в устройстве 102 должен быть заменен на элемент 2И-1И-ИЛИ и на дополнительный вход 1И будет заводиться указанный сигнал.

После отработки элементом 160 задержки (150-200 не), достаточной для дешифрации адреса в исполнителе и окончания переходных процессов 3 линиях связи, высокий уровень появляется на первом входе элемента И 164. При наличии сброса сигнала СХИ (68) предыдуш 5м задатчиком устройство 103 формирует на шину 12 сигнал СХЗ (67), Элемент 159, отрабатывающий зад,ержку 20-100 мкс, так называемый тайм-аут, предотвращает возможную блокировку системы. Принцип связи между устройствами системы - асинхронньй, т.е. на каждьй управляющий сигнал задатчика должен прийти ответный управляющий сигнал от исполнителя (в данном случае сигналы (67) и (68) соответственно) . При неисправности в исполнителе или линий связи ответный сигнал вообще не приходит. Если в задатчйке не предусмотрена подобная ситуация, то система блокируется и для возобновления ее работы требуется вмешательство оператора. Подобную блокировку устраняет элемент 159 и триггер 165.

Если ответный сигнал (68) не приходит в устройство 103 до истечения тайм-аута, триггер 165 переходит в состояние логической единицы, дальнейшая работа блокируется (низкий уровень на третьем входе элемента 161), о чем уведомляется устройст23во 100, Если бит разрешения прерыва ния в регистре 105 установлен, устpoftctBo, используя механизм прерыва ния уведомляет процессор о возникше ошибке и после запрещения последним прямого доступа (низкий уровень сигнала 152) схема переходит в исходное состояние. При правильной работе исполнителя приход сигнала СХИ (68) вызывает сброс сигнала СХЗ (67), установку триггера 166 и через задержку, отрабатываемую элементом 167, сброс триггера 156, что вызывает , сброс всех сигналов на шине 12. Сбро триггера 156 вызывает установку триг гера 168, выход Q которого заходит на вход прямого счета регистра 153, на вход обратного счета регистра 154 и в качестве сигнала (169) заходит в периферийный аппарат для сигнализации последнему о выполненной опера ции. Через время, отрабатываемое элементом 170, триггер 168 сбрасывается и схема готова к передаче следующего элемента информации. Если переданный элемент бьш последним на выходе антипереполнения Р (т.е. обнуления), формируется логическая единица, которая также приводит в действие механизм прерывания. Работа схемы при вьшолнении задат чиком операции чтения аналогична, Однако вместо сигнала выдачи данных (163) формируется сигнал приема данных (171), который поступает в устройство 102 на дополнительньш вход элемента 113 (см.замену элемента 130 в схеме 102) и приводит, к записи информации в регистр 108. В известной схеме двунаправленный Коммутатор 9 представлен на уровне блок-схемы и не удовлетворяет требованию его детализации до уровня стан дартных функциональных элементов. С другой стороны, указанная блок-схе ма отражает реализацию коммутатора 9 имеющего минимум оборудования, что в значительной степени усложняет понимание его функционирования. Функ|циональное назначение коммутатора 9 обеспечить передачу сигналов с одного канала связи в другой с предварительньм усилением. Кроме того, для ряда управляющих сигналов необходимо устранить нарушение временных соотношений, которые возникают при рас;пространении сигналов по реальным 142 иинам канала связи. С учетом сказанного на фиг,15 приведена функциональная схема двунаправленного коммутатора 9. Трансляция через коммутатор 9 однонаправленных сигналов запросов прерывания осуществляется элементами НЕ 172 и 173, а сигналов разрешения передачи - элементами НЕ 174 и 175. Элементы 172 и 174 являются приемниками, а элементы 173 и 175 - пере-. датчиками канала связи и особой функциональной нагрузки не несут. Состояние выходов приемников 172 анализируется периферийным анализатором 6 запросов (сигнал 17, фиг.1). Трансляция двунаправленных сигналов по информационно-управляющим шинам 12 и 23 требует использования приемника канала связи в виде элемента И 176, двух элементов 177 и 178 задержки и передатчика канала связи в виде элемента НЕ 179 для каждого направления. Рассмотрим передачу информации из центральной информационно-управляющей шины 12 в шину 23 на фиг.1 и 15 с линии 19 на линию . 20. В исходном состоянии на линиях 19 и 20 поддерживаются высокие уровни, которые поступают на первые входы элементов 176, на вторых и третьих входах которых поддерживаются низкие уровни. Элементы 179 выполнены в виде элементов с открытым коллекторным выходом и в исходном состоянии отключены от линий 19 и 20, При появлении низкого уровня в линии 19 на выходе элемента 176 формируется высокий уровень, который поступает на второй вход элемента 176 противоположного направления, что подтверждает низкий уровень на его выходе и на входы элементов 177 и 178,, Последний задерживает прохождение сигнала с его выхода на вход только низкого уровня, и в данном случае высокий . потенциал на его выходе формируется без задержки и поступает на третий вход элемента 176 противоположного направления, В зависимости от вида сигнала, передаваемого по информационно-управляющей шине, элемент 177 задерживает передачу либо низкого уровня, либо высокого. Например, трансляция сигналов СХЗ и СХИ требует задержки высокого уровня, а трансяция адреса, данных и линий управения - низког р. Пройдя через 3j;jeMeHT

251

177, высокий уровень поступает на вход элемента 179, на выходе которого формируется низкий уровень„ Так происходит передача низкого уровня с линии 19 на линию 20.

При переходе линии 19 в состояние высокого потенциала на втором входе элемента 176 противоположного направления без задержки формируется низкий уровень, на линии 20 высокий уровень появляется с задержкой, отрабатываемой элементом 177 и вносимо элементом 179. На выходе элемента 178 низкий уровень должен появиться только после гарантированного появле НИН высокого уровня на линии 20. Из этих условий выбирается величина задержки, отрабатываемая элементом 178

При отсутствии элементов 178 и связи выхода элемента 176 одного направления с входом элемента 176 другого направления коммутатор 9 переходит B режим блокировки при передаче низкого уровня. В этом случае элементы 179 обоих направлений поддерживают низкие уровни и нормальная работа системы нарушается. При наличии обратной связи между элементами 176 двух направлений, но при отсутствии элементов 177 возникает генерация в коммутаторе 9, и следовательно в линиях 19 и 20 при снятии низкого уровня в линии 19. Таким образом, схема коммутатора, представленная на фиг,15, содержит минимальное коли чество функциональных элементов и функциональных связей между ними, необходимых для его правильной работы.

Первые и вторые блоки 7 и 8 элементов запрета представляют собой совокупность отдельных элементов запрета, являющихся стандартными функциональными элементами. Количество элементов запрета в каждом блоке 7 и 8 равно числу линий в информационно-управляющих шинах . 12 или 23. Информационные входы элементов запрета подсоединены к линиям информационно-управляющих шин, выходы -К узлам 19 трансляции отдельных сигналов в коммутаторах 9, а управляющие входы объединены и подсоединены к шине 18 запрета. При наличии низкого уровня на этом выходе через блоки 7 и 8 запрещена передача сигналов, а следовательно, и логическая связь

422ь

между первой и второй информационно-управляющими шинами 12 и 23.

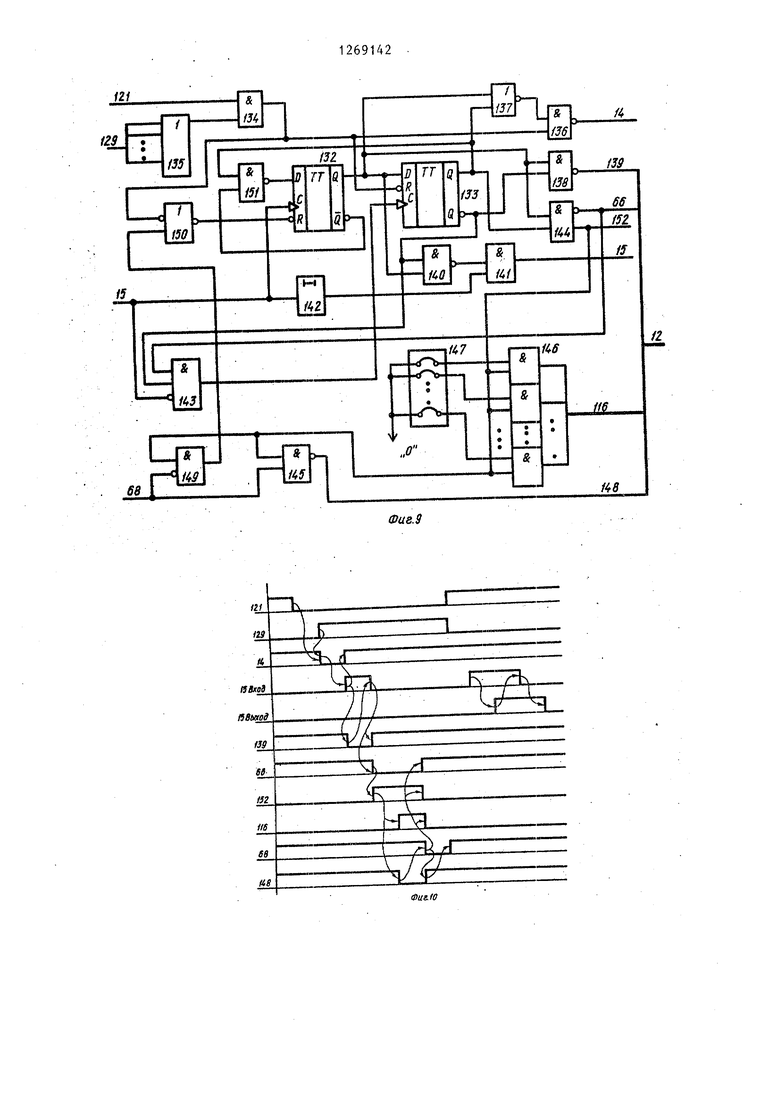

Рассмотрим принцип работы периферийного анализатора 6 запросов (фиг.16). В исходном состоянии отсутствуют сигналы на входах блока (180) приемников - удерживаются низкие уровни. Соответственно, нет сигналов и на первых входах элементов ЗИ блока 181 коммутатора, и вследствие этого отсутствуют сигналы на выходах первого 182 и второго 183 блоков передатчиков соответственно. Состояние информационных входов D регистра 184 запросов прерывания безразлично.

Предположим, что один из блоков 5 требует ресурсы системы, формируя сигнал на периферийной шине (22) запросов прерывания. Этот сигнал достигает коммутатора 9 и транслируется последним на центральную -шину (13) запросов прерывания (фиг.1). Одновременно сигналы с выходов приe никoв 172 в коммутаторе 9 поступают на информационные входы регигистра (184) запросов передачи. Сигнал Запрос прерывания, распространяясь в шине 13, достигает анализатора 1 запросов. Последний гфоизводи арбитраж (выделение запроса, имеющег высший приоритет) и, если позволяют условия, формирует сигнал на соответствующей линии центральной шины 15 разрешения прерывания, который достигает входа периферийного анализатора - входа блока (180) приемников. .Пройдя через блок (180) приемников, сигнал поступает на вход многовходовой схемы ИГШ 185 и на соответствующую пару связанных элементов ЗИ блока 181 коммутатора. Последний представляет собой совокупность элементарных коммутаторов (по количеству уровней-приоритета в системе), каждый из которых выполнен в виде двух элементов ЗИ.

Назначение элементарных коммутаторов - произвести коммутацию сигнала с выхода соответствующего приемника в периферийный канал 17 или в центральный канал 15. В каждьй момент времени анализатор (1) запросов формирует сигнал разрешения прерывания только в одной из линий шины 15, поэтому в блоке 181 будет подготовлен к работе только один из элементарных коммутаторов. Высокий уровень с выхода схемы ИЛИ 185 пост пает на вход элемента 186 задержки и производит запись информации в регистр 184, Через некоторое время, отрабатываемое элементом 186, н общем входе элементарных коммутатор блока 181 появляется высокий уровен разрешающий анализ выходов Q и Q того триггера, который связан с вхо дами ранее подготовленного элемента ного коммутатора. Если этот триггер установлен в состояние логической то сигнал Разрешение прерывания проходит через второй блок (183) передатчиков и затем транслируется через коммутатор 9 на периферийную шину (21) разрешения прерывания. Таким образом, периферийный анали затор (6) запросов запрещает дальней шее распространение сигнала в центральной шине 15 разрешения прерывания и производит его трансляцию в пе риферийную шину 21 разрешения прерьшания. Допустим, что источником сигнала Запрос прерывания, поступившим в анализатор (1) запросов, является один из группы блоков 5, ввода-вывода, подключенных к другому коммутатору 9, В этом случае к моменту записи в регистр (184) запросов передачи на его соответствующем информационном входе сохраняется уровень логического О (отсутствие сигнала Запрос прерывания). Поэтому соответствующий триггер устанавливается в состояние логического О и в этом случае сигнал Разрешение прерывания проходит на соответствующую линию выходной шины первого блока (182) передатчиков, В результате периферийный анализатор 6 осуществляет трансляцию сигнала разрешения прерывания к следующему периферийному анализатору (6) запросов. Число лини в соответствующих шинах анализатора 6, разрядность регистра 184 запросов прерывания, число приемников, передатчиков и элементарных коммутаторов в блоках 180, 182 или 183 и 181 соответственно равны числу уровней приоритетов в предлагаемой системе, В блоке (10) реконфигурации (фиг,2) первая 26 и вторая 27 сравнения вьшолнены на основе одноразрядного постоянного запоминающего устройства, адресные входы 65 и 70 которых соединены с адресными линиями информационно-управляющих шин 12 и 23 соответственно. Каждому устройству 5 и 11 и каждому блоку 4 памяти в схеме (26) сравнения отводится соответствующая ячейка, логическая единица заносится аппаратно (путем прожигания плавких перемычек)только в те ячейки, которым соответствуют устройства и блоки памяти, принадлежащие периферийной секции канала. Аналогично, схема (27) сравнения настраивается на адресные зоны центрального и всех других периферийных каналов. Установка схемы в исходное состояние производится под действием исходных состояний всех линий информационно-управляющих шин 12 и 23 - низкие уровни на входах R первого 28, второго 29, третьего 30и четвертого 31 триггеров и сброс пятого триггера 32 сигналом Подготовка (69), который поступает от процессора по шине 12 при запуске в работу системы. Настройка блока 10 на режим работы производится аппаратно с помощью первого 33, второго 34 и третьего 35 переключателей, Рассмотрим работу блока (10) реконфигурации в режиме РЕЖ1, Предположим, что одно из устройств центрального канала обращается к одному из устройств периферийного канала, Задатчик устанавливает на шине 12 адрес исполнителя (65), По данному адресу в схему 26 заносится логическая единица, поэтому на ее выходе F появляется высокий зфовень, а на выходе шестого элемента НЕ 60 - низкий уровень, В результате на выходе первого элемента 2И-ИЛИ 36 и информационном входе триггера 28 формируется низкий уровень. Через некоторое время задатчик сопровождает адрес устройства низким уровнем з правляющего сигнала СХЗ (67), На выходе второго элемента НЕ 56 появляется высокий уровень, который снимает низкий уровень на входе R триггера 28, запускается третий элемейт 52 задержки. Через время, отрабатываемое элементом 52 и достаточное для подготовки достоверной информации на входе триггера 28, производится запись в триггер 28 - высокий уровень на его динамическом входе С. В рассматриваемом случае состояние трйггера 2Ьне изменяется и через блоки 7 и 8 элементов- запрета, а следовательно, и через коммутатор 9 произво дится обмен информацией между -задатчиком и исполнителем. Если же задатчик производит обращение к зоне адресов своего канала (например, к блоку 2), то триггер 28 переходит в состояние логической единицы и через блоки 7 и 8 запреща1ется передача сигналов межд,у цент ральным и периферийным каналами низкий уровень на выходе четвертого элемента ИЛИ 41 и шине (1В) запрета. -В результате ресурсы периферийного канала могут быть использованы другими устройствами. Заканчивая обмен с исполнителем, задатчик сбрасывает сигнал СХЗ (67) и сигнал Занято (66). В результате на выходе второго элемента НЕ 56 появляется низкий .уровень, который сбрасывает триггер 28 и блок 10 возвращается в исходное состояние. Аналогична работа блока 10, в .режиме РЕЖ1, если задатчиком является устройство периферийного канала. Линии адреса (70), линия Занято (71) и линия СХЗ (72) анализируются второй схемой 27 сравнения, элемента ми НЕ 59 и 58 соответственно. Функциональные назначения седьмого элемента НЕ 61, пятого элемента (54) задержки, второго элемента 2И-ИЖ 37, второго переключателя 34 и третьего триггера 30 соответствуют рассмотренным элементам 60, 52, 36, 33 ,и 28 соответственно. Рассмотрим работу блока 10 в процессе обмена информацией межр,у- задат чиком и исполнителем в режиме РЕЖ25 при котором переключатель 33 подключает к первому входу элемента ИЛИ 4 выход Q пятого триггера 32, В резуль тате на шине 18 формируется низкий уровень, запрещающий трансляцию сигналов через блоки 7 и 8, Логическая связь между центральным и периферийным каналами восстанавливается (разрешается трансляция сигналов между ними) либо при обращении устройства центрального канала к устройству периферийного канала, либо прн выполнении устройством периферийного , канала операции Прерывание. В первом случае взводится триггер 28 при Формировании задатчиком на шине 12 1 2.30 адреса исполнителя (65) и сигнал СХЗ (67) , В режиме РЕЖ2 на вход десятого элемента НЕ 64 поступает от третьего переключателя 35 низкий уровень. Сигнал с выхода Q триггера 28 поступает на первый вход второго элемента И 44. Если задатчик на игане 23 освободил ее, сбросив сигнал Занято (71), исполнитель на шине 23 освободил ее информационную часть - сигнал (73) - и не подготовил следзтощий задатчик - отсутствует сигнал ПВБ (74), то на выходе Элемента И 44 формируется низкий уровень. Этот низкий уровень поступает на первый вход третьего элемента И 45,, что запрещает выбор следующего задатчика, и на первый вход второго элемента ИЛИ 39, высокий уровень на выходе которого запускает четвертьш элемент (53) задержки. После времени, отрабатываемого элементом 53, на его выходе появляется высокий уровень, поступающий на второй вход четвертого элемента И 46 и разрешающий анализ его второго входа. Если блоку 10 удалось запретить выбор следующего задатчика (высокий уровб;нь на выходе Q второго триггера 29), то на выходе элемента И 46 формируется высокий уровень, что вызывает перевод триггера 32 в состояние логической единицы, В результате на шине 18 формируется высокий у1эовень и логическая связь между центральным и периферийным каналами восстанавливается. После сброса.задатчиком сигнала СХЗ (67)схема переходит в исходное состояние, под действием низкого уровня на выходе пятого элемента ИЛИ 42, Если устройство периферийного канала отрабатывает операцию прерывания, оно формирует низкий уровень сигнала Прерывание (75), что вызывает приход на входы первого элемента И 43 и пятого элемента ИЛИ 42 высокого уровня с выхода третьего элемента НЕ 57, Низкий уровень на входе R триггера 32 снимается, а низкий уровень на выходе элемента И 43, появляется при соблюдении дополнительных усло-i ВИЙ - сброс задатчиком сигнала Занято (66) и исполнителем сигнала СХИ (68)на шине 12, При соблюдении этих условий триггер 32 взводится, а после завершения операции прерывания переходит в К1сходное состояние под дей311

ствием высокого уровня сигнала Прерывание (75) в шине 23.

Для полного описания работы блока 10 рассмотрим его функционирование при трансляции и формировании сигналов разрешения прямого доступа. Триггер 29 в РЕЖ1 всегда находится в состоянии логического нуля, и низкий уровень с его выхода Q поступает на первый вход третьего элемента ИЛИ 40 и разрешает его работу по второму входу. Совокупность второго элемента 51 задержки, четвертого триггера 31, пятого 47 и шестого 48 элементов И представляет собой одноразрядный периферийньй анализатор 6 запросов. Восьмой 62 и девятый 63 элементы НЕ являются приемником и передатчиком сигнала запроса прямого доступа. В исходном состоянии в шине 16 поддерживается низкий уровень

В функциональном плане работа рассматриваемой части блока 10 в РЕЖ1 не отличается от работы периферийного анализатора запросов 6. Если источником сигнала запроса прямого доступа является устройство на шине 25, то низкий уровень передается на шину 14, на что анализатор запросов центрального канала отвечает высоким уровнем сигнала (16). На выходе Q триггера (31) формируется высокий уровень, который переводит шину

24в состояние логической единицы. Если же с приходом высокого уровня на шину 16 на выходе седьмого элемента И 49 низкий уровень, то высокий уровень формируется на продолжении центральной шины 16. разрешения прерывания.

. В РЕЖ 2 исходное состояние . Сигнал запроса прерывания с шины

25теперь не транслируется в шину

14, а поступает на второй вход эле-мента И 45, на входе которого поддерживается высокий уровень, если нет обращения устройств из .центрального канала в периферийный канал. Если в шине 23 сброшен сигнал ПВБ (74) - разрешение проведения арбитража (см.описание работы анализатора : запросов), на выходе элемента И 45 формируется высокий уровень. На установочном входе R триггера 29 поддерживается высокий уровень, что разрешает его работу. После задержки, отрабатьшаемой первым

4232

элементом 50 задержки, высокий уровень появляется на динамическом вхо С триггера 29, который переходит в состояние логической единицы. В результате на шине 24 формируется высокий уровень, а с выхода Q низкий уровень запрещает обращение устройс через блок 10, т.е. в ответ на запрос прямого доступа блок 10 отвечает сигналом разрешения прямого доступа. Устройство - источник запроса в ответ сбрасывает низкий уровень в шине 25 и устанавливает сигнал ПВБ (низкий уровень 74). Триггер 29 сбрасывается, сигнал на шине 24 становится низким (отсутствие сигнала), и схема переходит в исходное состояние. В РЕЖ2 сигнал разрешения передачи в шине 16 всегда передается блоком 10 на ее продолжение.

Формула изобретения

1. Многоканальная система управления распределением ресурсов в. вычислительном комплексе, центральный канал которой содержит блок памяти, анализатор запросов, группу блоков ввода-вывода, а каждый периферийньй канал содержит периферийньй анализатор запросов, двунаправленньй коммутатор, группу блоков ввода-вывода, устройство прямого доступа, причем выход разрешения прерывания Каждого предьщущего блока ввода-вывода каждой группы соединен с входом разрешения прерывания каждого последующего блока ввода-вывода той же группы, выход разрешения прер ывания анализатора запросов центрального канала соединен с входом первого блока ввода-вывода группы центрального канала, а выход разрешения прерывания последнего блока ввода-вывода группы центрального канала соединен с входом разрешения прерывания анализатора запросов первого периферийного канала, выход разрешения прерывания анализатора запросов каждого предьщущего периферийного канала . соединен с входом разрешения- прерывания анализатора запросов каждого последующего периферийного канала, вход-выход анализатора запросов каждого периферийного канала соединены с входом-выходом двунаправленного коммутатора этого же канала, вход . запросов прерывания которого соединен с выходами запросов прерывания блоков ввода-вывода группы своего канала, выходы запросов прерывания двунаправленных коммутаторов всех периферийных каналов объединены с выходами запросов прерывания блоков ввода-вывода центрального канала и соединены с входом запросов прерывания анализатора запросов центрального канала, информационно-управляющие входы-выходы блоков вводавывода центрального канала, анализатора запросов центрального канала и блока памяти центрального канала объединены центральной информационноуправляющей шиной, информационноуправляющие входы-выходы блоков ввода-вывода каждого периферийного канала объединены соответствующей периферийной информационно-управляющей щиной, отличающаяся тем, что, с целью повьшения коэффициента использования оборудова.ния и надежности системы за счет отключения отказавшего канала от других работоспособных каналов, в каясдый периферийньй канал системы введены блок памяти, блок реконфигурации, первый и второй блоки элементов запрета, причем выход разрешения прямого доступа анализатора запросов центрального канала соединен с входом разрешения прямого доступа блока реконфигурации периферийного канала, вькод разрешения прямого доступа бло ка реконфигурации каждого предыдущего периферийного канала соединен с входом разрешения прямого доступа блока реконфигурации каждого последующего периферийного канала., вход запроса прямого доступа анализатора запросов центрального канала соедине с выходами запроса прямого доступа блоков реконфигурации периферийных каналов, центральные информационноуправляющие входы блоков реконфигурации и центральные информационно-управляюшзие входы-выходы первых блоков элементов запрета периферийных каналов подсоединены к центральной информационно-управляющей шине, периферийный, информационно-управляюшрй вход блока реконфигурации, периферийный информационно-управляющий вход-выход второго блока элементов запрета и информационно-управляющие входы-выходы устройства прямого доступа и блока памяти каждого периферийного канала подсоединены к периферийной информационно-управляющей шине, выход разрешения прерывания двунаправленного коммутатора каждого периферийнЬго канала соединен с входом разрешения прерьгеания устройства прямого доступа этого же канала, выход разрешения прерывания которого соединен с входом разрешения прерьшания первого блока ввода-вывода этого периферийного канала, выход запроса прерывания устройства прямого доступа каждого периферийного канала подсоединен к входу запроса прерывания двунаправленного коммутатора этого же канала, вход разрешения прямого доступа и выход запроса прямого доступа устройства прямого доступа каждого периферийного канала соединены с периферийным выходом разрешения прямого доступа и ВХОДОМ запроса прямого доступа блока реконфигурации этого же канала соответственно, выход запрета которого соединен с входами запрета первого и второго блоков элементов запрета этого же канала, первьй и второй информационно-управляющие входы-выходы которых соединены с первым и вторым информационно-управляющими входами-выходами двунаправленного коммутатора этого периферийного канала.

2,Система поп,1,о т л и ч а я с я тем, что блок реконфигурации каждого периферийного канала содержит две схемы сравнения, пять триггеров, три переключателя, два элемента 2H-IfflH, пять элементов ИЛИ, семь элементов И, пять элементов задержки, десять элементов НЕ, причем центральный информационно-управляющий вход блока соединен с входами первой схемы сравнения первого и второго элементов НЕ, первого элемента И и первым входом первогогэлемента ИЖ, периферийный информационно-управляющий вход блока соединен с входами второй схемы сравнения с третьего по пятый элементов НЕ и второго элемента И, выход первой схемы сравнения соединен непосредственно и через шестой элемент НЕ соответственно с первым и вторым входами первого элемента 2И-ШШ, выход которого соединен с первым входом первого триггера, выход которого соединен с первым входом первого переключател

и через второй элемент И с первыми входами второго элемента ИЛИ и тре- тьего элемента И, выход которого через первый элемент задержки соединен с первым входом второго триггера, выходы которого соединены с первыми входами соответственно третьего элемента ИЛИ и четвертого элемента И, выход второй схемы сравнения соединен непосредственно и через седьмой элемент НЕ соответственно с первым и вторьм входами второго элемента 2И-ИЛИ, выход которого соединен с первым входом третьего триггера, выход которого через соединенные последовательно второй переключатель и четвертый элемент ИЛИ соединен с выходом запрета блока, вход разрешения прямого доступа которого соединен с первьм входом четвертого триггера и через второй элемент задержки с первыми входами пятого и шестого элементов И, вторые входы . которых соединены с выходами четвертого триггера, а выходы соответственно - с выходом разрешения прямого доступа блока и вторым входом третьего элемента ИЛИ, выход которого соединен с периферийным выходом разрешения прямого доступа блока, вход запроса прямого доступа которого через восьмой элемент НЕ соединен с вторым входом третьего элемента И и первым входом седьмого элемента И, прямой и инверсный выходы которого соединены соответственно с вторым входом четвертого триггера и через

девятый элемент НЕ с выходом запроса прямого и четвертым входом третьего элемента И доступа блока, выход

третьего переключателя соединен с J третьими входами первого и второго элементов 2И-ИЛИ, вторым входом седьмого элемента И и через десятый элемент НЕ с четвертыми входами эле.ментов 2И-ИЛИ, выходы первого и чет10 вертого элементов НЕ соединены с

вторыми входами соответственно перIвого и третьего триггеров, выход второго элемента НЕ соединен с входом пятого элемента ШШ и через

15 третий элемент задержки с третьим входом первого триггера, выход третьего элемента НЕ через пятьй элемент ИЛИ и первый элемент И соединен соответственно с первым входом пято20 го триггера и вторым входом второго элемента ИЛИ, выход которого через четвертый элемент задержки соединен с вторым входом четвертого элемента И, выход которого соединен с вто5 рым входом пятого триггера, выход которого соединен с вторым входом ; первого переключателя; выход которого соединен с входом четвертого элемента ИЛИ, периферийный ннформацион0 но-управляющий вход блока соединен с третьим входом третьего элемента И и вторым входом первого элемента ИЛИ, выход которого соединен с вторым входом триггера, выход пятого J элемента НЕ через пятый элемент за:держки соединен с третьим входом третьего триггера.

RG 84

36

&

iS

d &

f6

| название | год | авторы | номер документа |

|---|---|---|---|

| Многоканальная система управления распределением ресурсов в вычислительном комплексе | 1987 |

|

SU1432580A1 |

| Устройство для согласования системных магистралей | 1989 |

|

SU1674143A1 |

| Устройство для сопряжения двух ЭВМ | 1986 |

|

SU1399751A1 |

| Устройство для формирования сигнала идентификации начала команды ЭВМ | 1985 |

|

SU1352493A1 |

| Аналого-цифровая вычислительная система и аналоговая вычислительная машина (ее варианты) | 1983 |

|

SU1259300A1 |

| Устройство для сопряжения ЭВМ с магистралью внешних устройств | 1985 |

|

SU1408440A1 |

| Устройство для сопряжения вычислительного модуля с магистралью | 1985 |

|

SU1325495A1 |

| Устройство для сопряжения двух магистралей | 1984 |

|

SU1241249A1 |

| Устройство для сопряжения двух магистралей | 1986 |

|

SU1348874A1 |

| Устройство для сопряжения двух магистралей | 1988 |

|

SU1509915A2 |

Изобретение относится к области вычислительной техники и может быть использовано в вычислительных системах с большим числом устройств ввода-вывода. Целы изобретения является повьЕпение коэффициента использования оборудования и надежности системы. Система состоит из центрального канала, включающего блок памяти, анализатор запросов, группу блоков ввода-вывода и периферийных каналов, содержащих анализатор запросов, двунаправленный коммутатор, группу блоков ввода-вьшода,устройство прямого доступа, блок памяти, Блок реконфигурации, блок элементов запроса. Система позволяет распределить ресурсы между.отдельными каналами для их одновременной работы, что обеспечивает постоянную загрузку процесi сора. Кроме того, система позволяет отключать каналы, в которых произо(Л шел отказ, обеспечивая освобождение центрального канала и продолжение работы процессора. 1 з.п. ф-лы, 18 ил. ю О5 СО 1 tc

9S

Фиг.З

L «

77 SB B2

a

a

$

Z n

je

i

ZIc

13 /4 f6

11

16

IZS

116

119

к

PC

HI

s,

it

Kt

f3

22

| Авторское свидетельство СССР № 758118, кл | |||

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Система обработки информации | 1978 |

|

SU922712A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1986-11-07—Публикация

1982-12-15—Подача