(54) А,(.1ЛПТИВНОЕ ТЕ/ЙИЗМЕРИТЕЛЬНОЕ УСТРОЙСТВО

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для отображения информации на экране телевизионного приемника | 1988 |

|

SU1583967A1 |

| Устройство для формирования и передачи дискретных сигналов | 1985 |

|

SU1277420A1 |

| Устройство для сбора и передачииНфОРМАции | 1977 |

|

SU678974A1 |

| Устройство для сопряжения вычислительной машины с каналами связи | 1990 |

|

SU1727126A1 |

| Адаптивный коммутатор системыТЕлЕизМЕРЕНий | 1979 |

|

SU809295A1 |

| Адаптивный коммутатор | 1979 |

|

SU824264A1 |

| Коммутатор каналов для телеметрической системы | 1979 |

|

SU855714A1 |

| Адаптивная телеметрическая система | 1979 |

|

SU783825A1 |

| Устройство для отладки программ | 1983 |

|

SU1290334A1 |

| УСТРОЙСТВО ДЛЯ РЕГИСТРАЦИИ ЧИСЛА ПРОСТОЕВ ОБОРУДОВАНИЯ | 1991 |

|

RU2017219C1 |

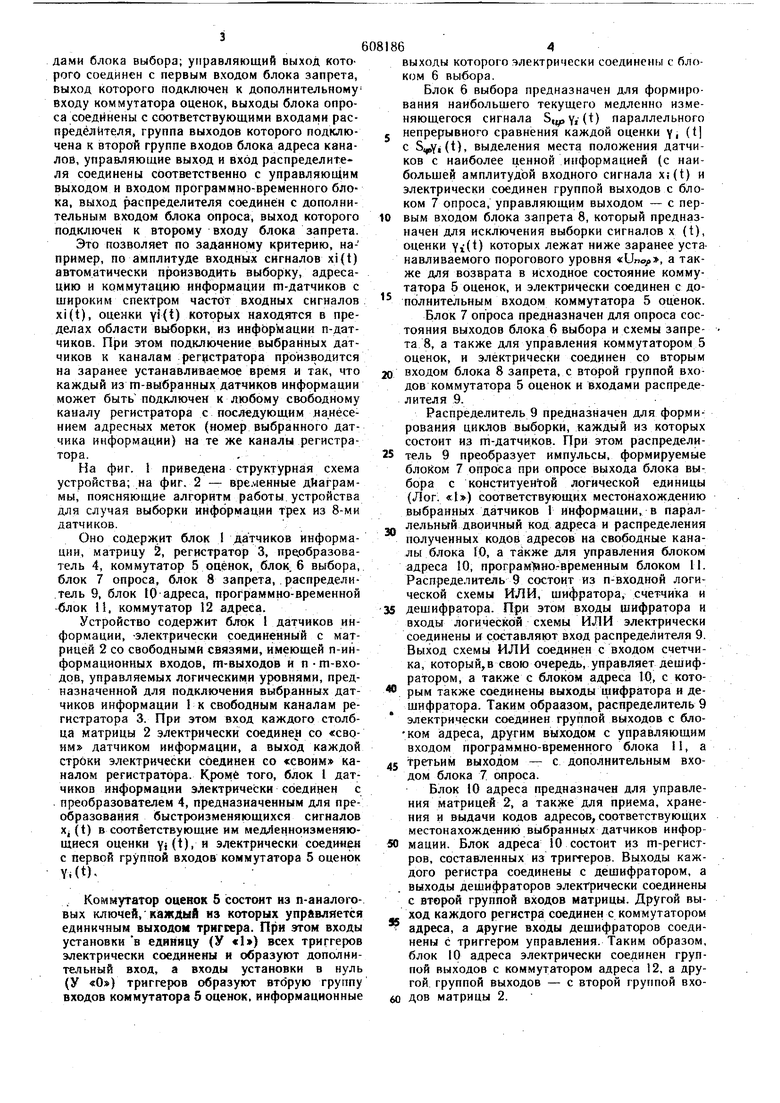

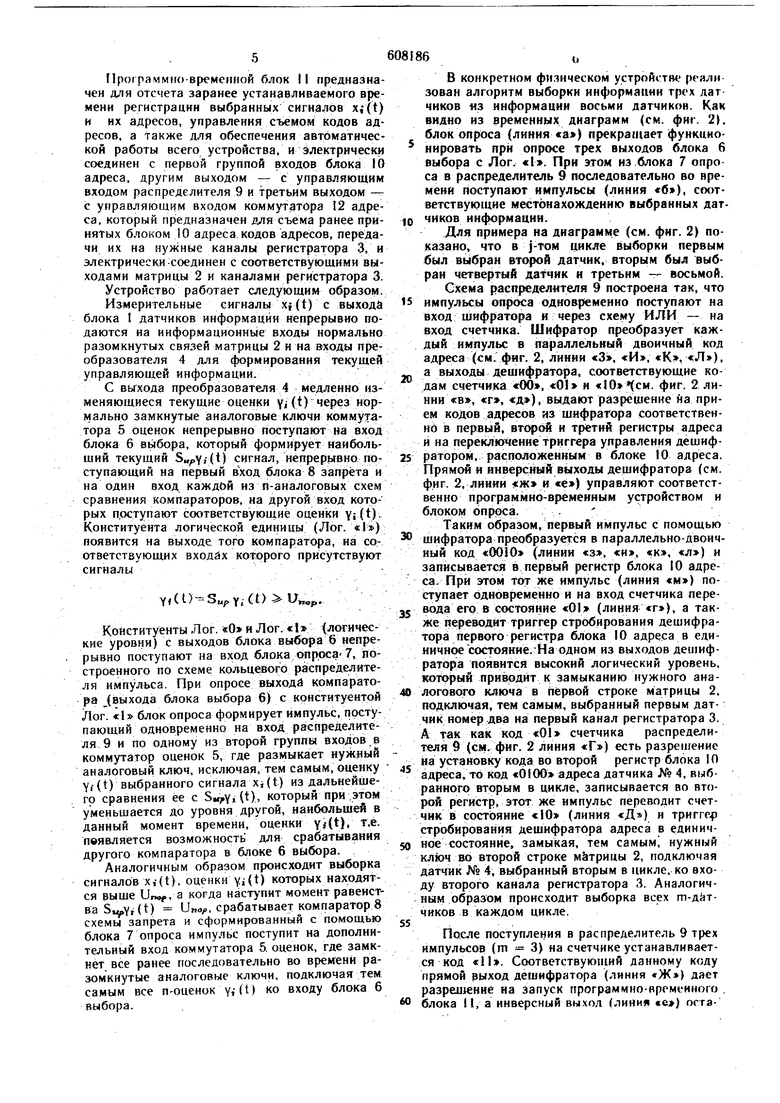

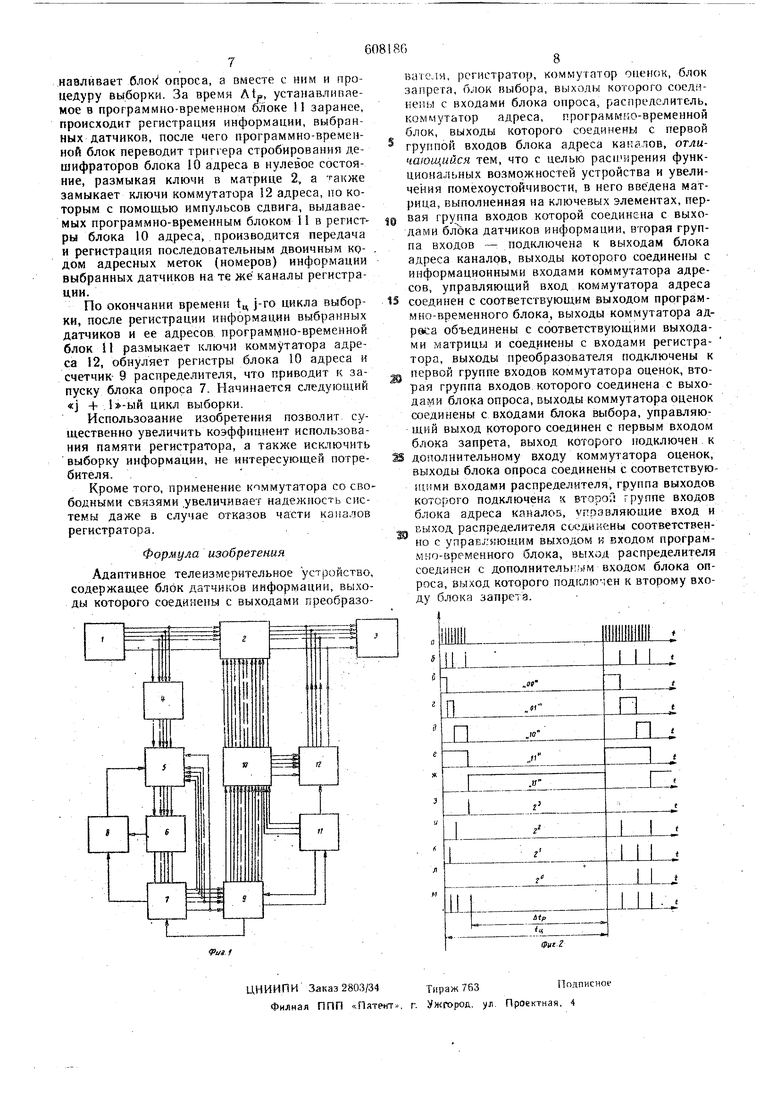

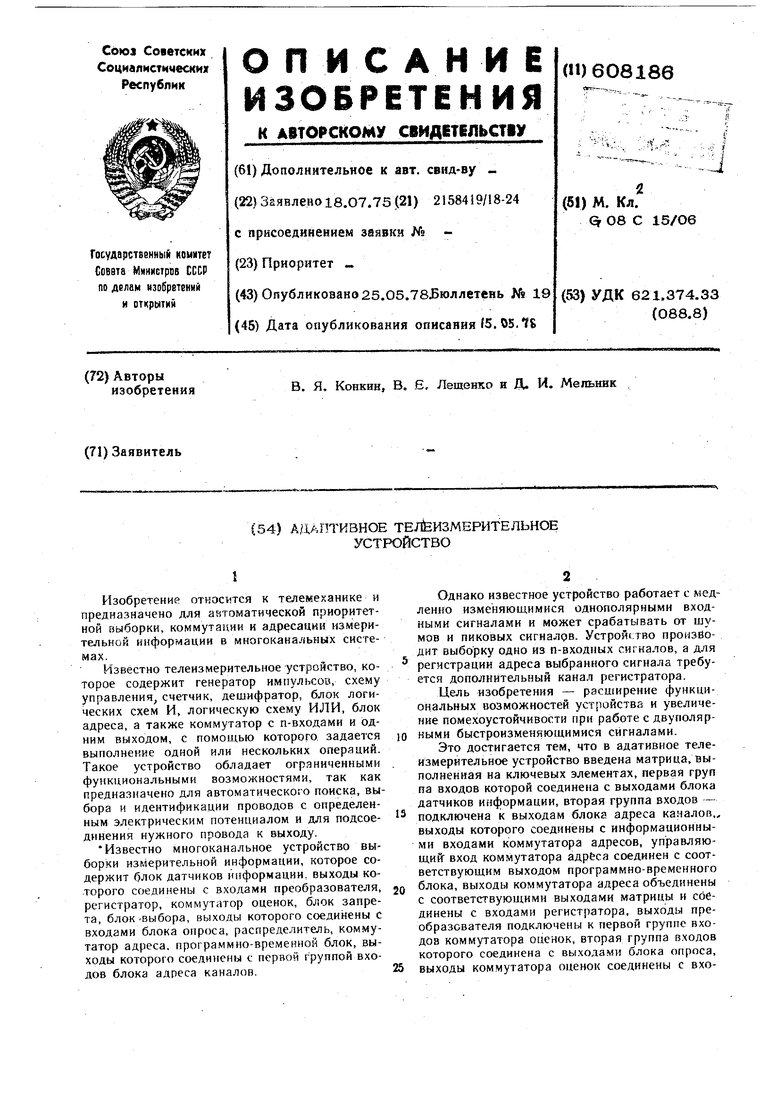

Изобретение относ1 тся к телемеханике я предназначено для автоматической приоритетной выборки, коммутации и адресации измерительной информации в многоканальных системах. Известно телеизмерительное устройство, которое содержит генератор импульсов, схему управления, счетчик, дешифратор, блок логических схем И, логическую схему ИЛИ, блок адреса, а также коммутатор с п-входами и Одним выходом, с помощью которого, задается выполнение одной или нескольких операций. Такое устройство обладает ограниченными функ 1иональиыми возможностями, так как предназначено для автоматического поиска, выбора и идентификации проводов с определенным электрическим потенциалом и для подсоединения нужного провода к выходу. Известно многоканальное устройство вЫ борки измерительной информации, которое содержит блок датчиков информации, выходы которого соединены с входами преобразователя, регистратор, коммутатор оценок, блок запрета, блокВыбора, выходы которого соединены с входами блока опроса, распределитель, коммутатор адреса, программно-временной блок, выходы которого соединены с первой группой входов блока адреса каналов. Однако известное устройство работает с медленно изменяющимися однополярными входными сигналами и может срабатывать от шумов и пиковых сигналов. Устройство производит выборку одно из п-входных сигналов, а для регистрации адреса выбранного сигнала требуется дополнительный канал регистратора. Цель изобретения - расширение функциональных возможностей устройства и увеличение помехоустойчивости при работе с двуполярными быстронзменяющимися сйгиалами. Это достигается тем, что в адативное телеизмерительное устройство введена матрица, выполненная на ключевых элементах, первая груп па входов которой соединена с выходами блока датчиков информации, вторая группа входов - подключена к выходам блока адреса каналов,, выходы которого соединены с информационными входами коммутатора адресов, управляющий вход коммутатора адреса соединен с соответствующим выходом программно-временного блока, выходы коммутатора адреса объединены с соответствующими выходами матрицы и соединены с входами регистратора, выходы преобразователя подключены к первой группе входов коммутатора оценок, вторая группа входов которого соединена с выходами блока опроса, выходы коммутатора оценок соединены с входами блока выбора; управляющий выход которого соединен с первым входом блока запрета, выход которого подключен к дополнительному входу коммутатора оценок, выходы блока опроса соединены с соответствующими входами распределителя, группа выходов которого подключена к второй группе входов блока адреса каналов, управляющие выход и вход распределителя соединены соответственно с управляюииим выходом и входом программно-временного блока, выход распределителя соединен с дополнительным входом блока опроса, выход которого подключен к второму входу блока запрета. Это позволяет по заданному критерию, например, по амплитуде входных сигналов xi{t) автоматически пронзводить выборку, адресацию и коммутацию информации т-датчнков с широким спектром частот входных сигналов xi(t), оценки (i) которых находятся в пределах области выборки, из информации п-датчиков. При этом подключение выбранных датчиков к каналам регистратора производится на заранее устанавливаемое время и так, что каждый из гп-выбранных датчиков информации может быть подключен к любому свободному каналу регистратора с последующим нанесением адресных меток (номер выбранного датчика информации) на те же каналы регистратора.. На фиг. 1 приведена структурная схема устройства; на фиг, 2 - временные диаграммы, поясняющие алгоритм работы устройства для случая выборки информации трех из 8-ми датчиков. Оно содержит блок I датчиков информации, матрицу 2, регистратор 3, пре.образователь 4, коммутатор 5 оценок, блок. 6 выбора, блок 7 опроса, блок 8 запрета, распределитель 9, блок Ю адреса, программно-временной -блок 11, коммутатор 12 адреса. Устройство содержит блок 1 датчиков информации, -электрически соединенный с матрицей 2 со свободными связями, имеющей п-информациоииых входов, гп-выходов и л т-входов, управляемых логическими уровнями, предназначенной для подключения выбранных датчиков информации 1 к свободным каналам регистратора 3. При этом вход каждого столбца матрицы 2 электрически соединен со «своим датчиком ииформации, а выход каждой строки электрически соединен со «своим каналом регистратора. Кроме того, блок I датчиков информации электрически соединен с преобразователем 4, предназначенным для преобразования быстроизменяющихся сигналов Xj (t) в соотбетствующие им медЛеннонзменяющиеся оценки Yt() и электрически соединен с первой группой входов коммутатора 5 оценок Y.(t)/ Коммутатор оценок 5 состоит из п-аиалоговых ключей, каждый из которых управляется единичным выходом трнгсера. При этом входы установки в единицу (У «1) всех триггеров электрически соединены и образуют дополнительный вход, а входы установки в нуль (У «О) триггеров образуют вторую группу входов коммутатора 5 оценок, ииформационные выходы которого электрически соединены с блоком 6 выбора. Блок 6 выбора предназначен для формирования наибольщего текущего медленно изменяющегося сигнала S,YI() параллельного непрерывного сравнения каждой оценки YI (tj с S,Yi(t), выделения места положения датчиков с наиболее ценной информацией (с наибольщей амплитудой входного сигнала x;(t) и электрически соединен группой выходов с блоком 7 опроса, управляющим выходом - с первым входом блока запрета 8, который предназначен для исключения выборки сигналов х (t), оценки Yi(t) которых лежат ниже заранее устанавливаемого порогового уровня «Unop, а также для возврата в исходное состояние коммутатора б оценок, и электрически соединен с дополнительным входом коммутатора 5 оценок. Блок 7 опроса предназначен для опроса состояния выходов блока 6 выбора и схемы запрета 8, а также для управления коммутатором 5 оценок, и электрически соединен со вторым входом блока 8 запрета, с второй группой входов коммутатора 5 оценок и входами распределителя 9. Распределитель 9 предназначен для формирования циклов выборки, каждый из которых состоит из ш-датчиков. При этом распределитель 9 преобразует импульсы, формируемые блоком 7 опроса при опросе выхода блока выбора с конституентой логической единицы (Лог «1) соответствующих местонахождению выбранных датчиков 1 информации, в параллельный двоичный код адреса и распределения полученных кодов адресов на свободные каналы блока О, а также для управления блоком адреса 10, программно-временным блоком И. Распределитель 9 состоит из п-входной логической схемы ИЛИ, шифратора, счетчика и дешифратора. При этом входы шифратора и входы логической схемы ИЛИ электрически соединены и составляют вход распределителя 9. Выход схемы ИЛИ соединен с входом счетчика, который,в свою очередь, управляет дешифратором, а также с блоком адреса 10, с которым также соединены выходы шифратора и дешифратора. Таким обраазом, распределитель 9 электрически соеДииен группой выходов с блоком адреса, другим выходом с управляющим входом программно-временного блока И, а третьим выходом - с дополнительным входом блока 7 опроса. Блок 10 адреса предназначен для управления матрицей 2, а также для приема, хранения и выдачи кодов адресов, соответствующих местонахождению выбранных датчиков информации. Блок адреса 10 состоит из т-регистров, составленных из триггеров. Выходы каждого регистра соединены с дешифратором, а выходы дешифраторов электрически соединены с второй группой входов матрицы. Другой выход каждого регистра соединен с коммутатором адреса, а другие входы дешифраторов соединены с триггером управления. Таким образом, блок 10 адреса электрически соединен группой выходов с коммутатором адреса 12, а другой группой выходов - с второй группой вхоДОН матрицы 2. Ilporраммко-времемной блок il предназначен для отсчета заранее устанавлнваемого времени регистрации выбранных сигналов x,-(t) и их адресов, управления съемом кодов адресов, а также для обеспечения автоматической работы всего устройства, и электрически соединен с первой группой входов блока 10 адреса, другим выходом - с управляющим входом распределителя 9 и третьим выходом - с управляющим входом коммутатора 12 адреса, который предназначен для съема ранее принятых блоком 10 адреса кодов адресов, передачи их на нужные каналы регистратора 3, и электрически соединен с соответствующими выходами матрицы 2 и каналами регистратора 3. Устройство работает следующим образом. Измерительные сигналы xj(t) с выхода блока I датчиков информации непрерывно подаются на информационные входы нормально разомкнутых связей матрицы 2 и на входы преобразователя 4 для формирования текущей управляющей информации. С преобразователя 4 медленно изменяющиеся текущие оценки YJ (t) через нормально замкнутые аналоговые ключи коммутатора 5 оценок непрерывно поступают на вход блока 6 выбора, который формирует наибольший текущий SKpYj(t) сигнал, непрерывно поступающий на первый вход блока 8 запрета и на одни вход каждой из п-аналоговых схем сравнения компараторов, на другой вход которых п.оступают соответствующие оценки Yi (t). Конституента логической единицы (Лог. «) появится на выходе, того компаратора, на соответствующих входах которого присутствуют сигналы уК1 -3„рУ;а)1Л«р. Конституенты Лог. «О и Лог. «I (логические уровни) с выходов блока выбора 6 непрерывно поступают на вход блока йпррсЗ7, построенного по схеме кольцевого распределителя импульса. При опросе выходи компаратора {выхода блока выбора 6) с конституентой Лог. «1 блок опроса формирует импульс, поступающий одновременно на вход распределителя 9 и по одному из второй группы входов в коммутатор оценок 5, где размыкает нужный аналоговый ключ, исключая, тем самым, оценку у,-(t) выбранного сигнала Xi(t) из дальнейшего сравнения ее с S,YI () ™рый при этом уменьшается до уровня другой, наибольшей в данный момент времени, оценки i(i), т,е. появляется возможность для срабатывания другого компаратора в блоке 6 выбора. Аналогичным образом происходит выборка сигналов x,-(t). оценки yi(t) которых находятся выще Unep, а когда наступит момент равенства S,.oYi(tj Uno/., срабатывает компаратор 8 схемы запрета и сформированный с помощью блока 7 опроса импульс поступит на дополнительный вход коммутатора 5. оценок, где замкнет все ранее последовательно во времени разомкнутые аналоговые ключи, подключая тем самым все п-оценок у,-(Ч) ко входу блока б выбора. 6о В конкретном физическом устройспн- реяли зован алгоритм выборки информации трех датчиков из информации восьми датчиков. Как видно из временных диаграмм (см. фиг. 2), блок опроса (линия «а) лрекра(цает функционировать при опросе трех выходов блока 6 выбора с Лог. «I. При этом из .блока 7 опроса в распределитель 9 последовательно во времени поступают импульсы (линия «б), соответствующие местонахождеиию выбранных датчиков информации. Для примера иа диаграмме (см. фиг. 2) показано, что в J-TOM цикле выборки первым был выбран второй датчик, вторым был выбран четвертый датчик и третьим - восьмой. Схема распределителя 9 построена так, что импульсы опроса одновременно поступают на вход и1ифратора и через схему ИЛИ - на вход счетчика. Шифратор преобразует каждый импульс 8 параллельный двоичный код адреса (см. фиг. 2, линии «3, «И, «К, «Л), а выходы дещифратора, соответствующие кодам счетчика «00, «01 и «10(см. фиг. 2 линии «в, «г, «д), выдают разрешенне на прием кодов адресов из щифратора соответственно в первый, второй и третий регистры адреса и на переключение триггера управления дещнфратором, расположеиным в блоке 10 адреса. Прямой и инверсный выходы дешифратора (см. фиг. 2, линии «ж и «е) управляют соответственно программно-временным устройством и блоком опроса. Таким образом, первый импульс с помощью шифратора преобразуется в параллельно-двоичный код «0010 (линии «3, «и, «к, «л) и записывается в первый регистр блока 10 адреса. При этом тот же импульс (линия «м) поступает Одновременио и иа вход счетчика перевода его в состояние «01 (линия «г), а также переводит триггер стробирования дешифратора первого регистра блока 10 адреса в единичное состояние.На одном из выходов дешифратора Появится высокий логический уровень, который приводит к замыканию нужного аналотового ключа в первой строке матрицы 2, подключая, тем самым, выбранный первым датчик номер два на первый канал регистратора 3. А так как код «01 счетчика распределителя 9 (см. фиг. 2 линия «Г) есть разрешение йа установку кода во второй регистр блока 10 адреса, тО код «0100 адреса датчика № 4, выбраииогр вторым в цикле, записывается во второй регистр, этот же импульс переводит счетчик в состояние «10 (линия «Д) и триггер стробирования дешифратора адреса в единичное состояние, замыкая, тем самым нужный ключ во второй строке матрицы 2, подключая датчик № 4, выбранный вторым в цикле, ко входу второго канала регистратора 3. Аналогичным образом происходит выборка всех т-датчиков в каждом цикле. После поступления в распределитель 9 трех импульсов (ш 3) на счетчике устанавливается код «11. Соответствующий данному коду прямой рыход дешифратора (линия «Ж) даст разрешение иа запуск программио-вромеиного . блока 11, а инверсный выход (линия «е) оста

Авторы

Даты

1978-05-25—Публикация

1975-07-18—Подача