127

ты И-НЕ 6 и 17,регистр 7 сдвига, блок 8 управления, дешифратор 9, кодер 10, Ф 11 сигнала выборки канала, бло1 12 опроса состояния канала, блок 13 переключения адреса канала, распределитель 14, блок 15 запрета, генератор 16 управляемых сигналов, блок 18 сравнения, блок 19 передачи, содержащий элементы И-НЕ 22 и 23, инвертор 20, выходной триггер 21. Ф 11 содержит три элемента И-НЕ, два инвертора. Блок 12 содержит три инвертора, шесть элементов И-.НЕ. Блок 5 содержит семь элементов переключения. Блок 18 содержит три элемента

Изобретение относится к технике связи и может быть использовано в многоканальных системах передачи дискретной информации.

Цель изобретения - повьш ение точ- ности формирования и объема передавамой информации.

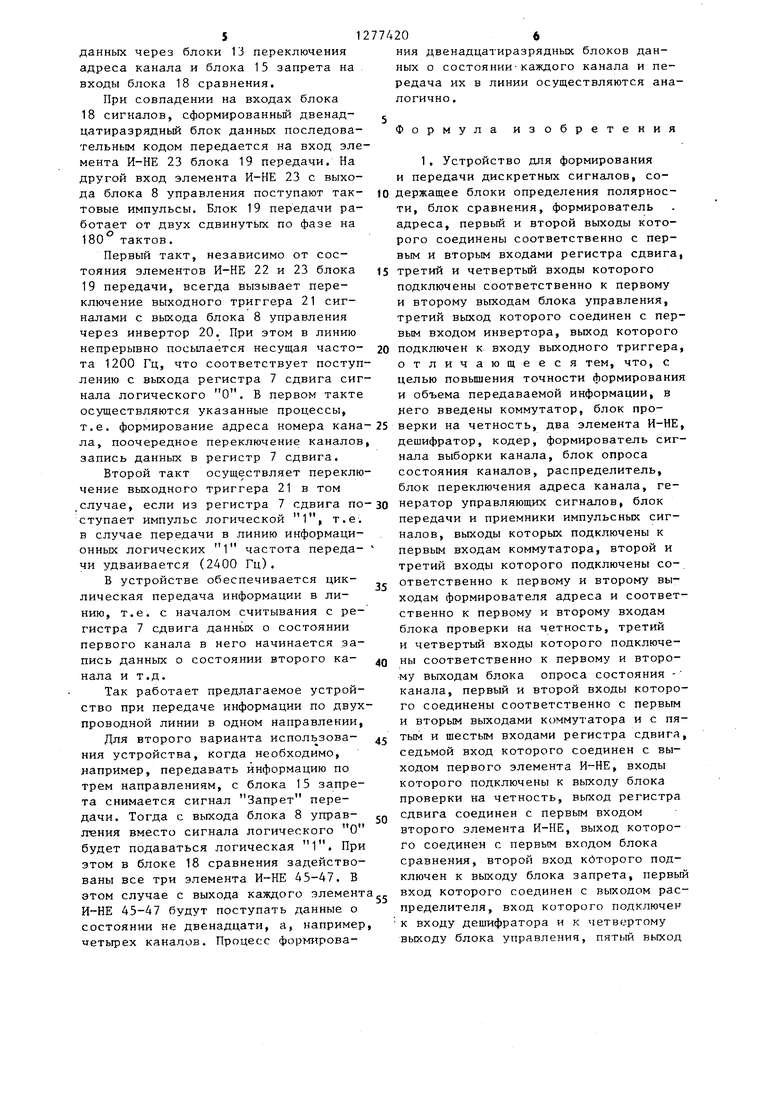

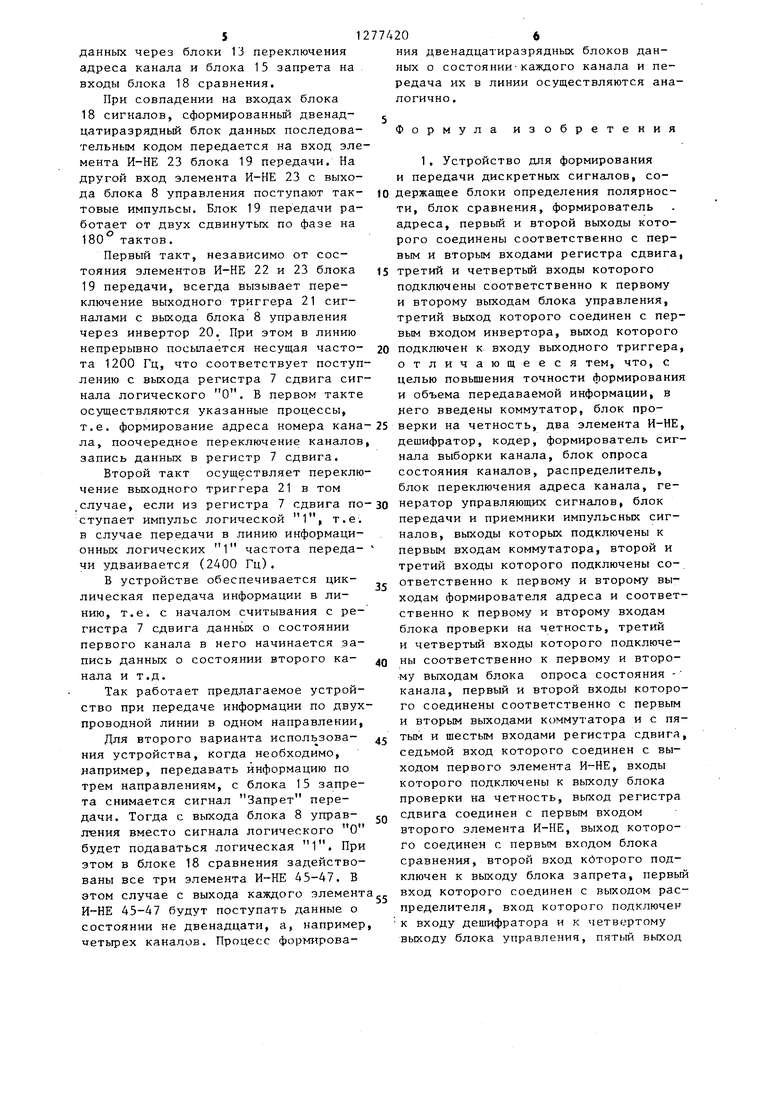

На фиг. 1 изображена структурная электрическая схема устройстваJ на фиг. 2 - структурная электрическая схема формирователя сигнала выборки канала, блока опроса состояния ка-, налов и блока проверки на четность; на фиг. 3 - структурная электрическая схема блока сравнения.

Устройство для формирования и передачи дискретных сигналов содержит блоки 1 определения полярности, приемники 2 импульсных сигналов, комму- . татор 3, формирователь 4 адреса, бло 5 проверки на четность, первый элемент И-НЕ 6, регистр 7 сдвига, блок 8 управления, дешифратор 9, кодер 10, формирователь 11 сигнала выборки канала, блок 12 опроса состояния ка- нала, блок 13 переключения адреса канала, распределитель 14, блок 15 запрета, генератор 16 управляюш;их сигналов, второй элемент И-НЕ 17, блок 18 сравнения, блок 19 передачи, инвертор 20, выходной триггер 21. Блок передачи содержит первый и второй элементы И-НЕ 22 и 23.

Формирователь сигнала выборки канала содержит первый, второй и тре-

И-НЕ. Дешифратор 9 с 10 и распределителем 14 обеспечивает дешифрацию номеров каналов и распределение их по возрастающему порядку. При совпадении на входах блока 18 сигналов, сформированный двенадцати- разрядньй блок данных последовательным кодом передается на вход элемента И-НЕ 23, на другой его вход с блока 8 поступают тактовые импульсы. Блок 19 работает от 2-х сдвинутых по фазе на 180 тактов, Б устройстве обеспечивается циклическая передача информации в линию. 1 з.п. ф-лы, 3 ил.

0

5

0

тий элементы И-НЕ 24-26, первый и второй инверторы 27 и 28.

Блок опроса состояния каналов содержит первый, второй и третий инверторы 29-31 и первый, второй, третий, четвертый, пятьй и шестой элементы И-НЕ 32-37.

Блок проверки на четность содержит первый, второй,третий, четвертьм, пятый, шестой и седьмой элементы 38-44 переключения.

Блок сравнения содержит первьй, второй и третий элементы И-НЕ 45-47.

Устройство работает следующим образом.

На вход блока 1 определения полярности сигналы могут поступать в виде перепада положительного (например, 27В) или отрицательного (-27В) напряжения. Установка необходимого режима осуществляется в блоке 1 оп-. ределения полярности.

С выхода блока 1 определения полярности сигнал поступает на вход приемника 2 импульсных сигналов, в котором обеспечивается прием сигнала с акустической и оптической сигнализацией, формирование потенциалов

логических

О и Г

а также выда 20

35

30

ча сформированных сигналов на входы коммутатора 3, на другие входы которого с выхода формирователя 4 адреса подается сигнал, определяющий адрес номера и состояние канала, которьй в данньй момент находится под конт3

ролем. В кпммутеторс 3 rijioncxojuiT преобразование сигнала из логическ1гх О и 1 в сигналы БИТО - БИТ 3.

С выхода коммутатора 3 сигналы поступают на первые входы элементов И-НЕ 32-37, на другие входы которых через инверторы 29-31 поочередно подаются управляющие сигналы с выхода элементов И-НЕ 24-26, При совпадении сигналов на входах элементов И-НЕ 32-37 производится последовательное считывание через коммутаоор 3 принятой приемниками 2 импульсных сигналов информации.

С выхода блока 12 опроса состояни каналов информация поступает на входы элемента 39 переключения блока 5 проверки на четность. При поступлении на оба входа элементов 38-43 переключения одинаковой информации (1,1 или 0,0), на их выходах формируется логический О, а при поступлении разной информации - логическая 1. Одновременно с выхода формирователя 4 адреса на входы элемента 38 переключения поступает сигнал,включающий адрес номера канала,с которого в даиньй момент считывается информация.

С выхода блока 5 проверки на четность через элемент И-НЕ 6 на седьмой информационный вход регистра 7 сдвига поступают сигналы, определяющие четность передаваемой информации На другие входы регистра 7 сдвига поступают следующие данные: от коммутатора 3 - данные о состоянии (нор ма или авария) каналов в виде БИТО - БИТЗ; от формирователя 4 адреса - адрес номера канала и приемника 2, с которого считывается информация; от блока 8 управления - управляющие сигналы в виде тактовых импульсов с частотой 1200 и 2400 Гц.

На основании указанных сигналов для каждого канала формируется двенадцатиразрядный блок данных, кото- рый, например, может включать: 1 разряд - стартовый бит (всегда логический О); 2-9 разряды - информационный байт, содержащий 2-3 разряды - адрес номера канала, который кодируется следующим образом 2 разр. 3 разр.

-первый канал;

-второй канал

-третий канал,

-четвертый канал.

04

4,5 разряды - код выбора опрашиваемого приемника. При этом номеру приемника 2 соответствует код 4 разр. 5 разр,

-первый приемник ,

-второй приемник;

1 О - третий приемник ,

-четвертьй приемник.

Следовательно, общее число конт- ролируемых каналов может составить 16 (по четыре канала в каждом из четырех приемников),

6-9 разряды - информация о состоянии одного канала, закодированная в

20 виде

6 7 8 9

35

25

1 1 1 1 , - незадействие, 0101 - норма канала; 100 1 - авария канала, 10 разряд - четность передаваемой информации: логическая 1 - информация четная, логический О - нечетная, 11 и 12 разряды - стоповые им- ,Q пульсы (всегда логическая 1), т,е, каждый блок данных о состоянии канала содержит импульсную последовательность двоичных элементов, например, такого вида: 000100101111, которая означае т, что первый канал третьего

приемника находится в норме.

Образованный таким образом двенадцатиразрядный блок данных в параллельном коде записывается в регистр 7 сдвига и под воздействием тактовых импульсов, поступающих от блока 8 управления, передается через элемент И-НЕ 17 на вход блока 18 сравнения, на другие входы которого подаются одновременно с этим сигналы с выхода блока 13 переключения адреса канала и блока 15 запрета. Дешифратор 9 вместе с кодером 10 и рас- пред елителем 14 обеспечивает дешифрацию номеров каналов и распределе - ние их по возрастающему порядку, например, от 1 до 12 или 16, Для-этого с выхода блока 8 управления на входы дещифратора 9 и распределите- ля 14 поступают управляющие сигналы, под действием которых и осуществляется выбор очередного канала для опроса его состояния, а также вьщача

данных через блоки 13 переключения адреса канала и блока 15 запрета на входы блока 18 сравнения.

При совпадении на входах блока

18сигналов, сформированный двенадцатиразрядный блок данных последовательным кодом передается на вход элемента И-НЕ 23 блока 19 передачи. На другой вход элемента И-НЕ 23 с выхода блока 8 управления поступают тактовые импульсы. Блок 19 передачи работает от двух сдвинутьгх по фазе на 180 тактов.

Первый такт, независимо от состояния элементов И-НЕ 22 и 23 блока

19передачи, всегда вызывает переключение выходного триггера 21 сигналами с выхода блока 8 управления через инвертор 20. При этом в линию непрерывно посьтается несущая частота 1200 Гц, что соответствует поступлению с выхода регистра 7 сдвига сигнала логического О. В первом такте осуществляются указанные процессы,

т.е. формирование адреса номера кана-25 верки на четность, два элемента И-НЕ,

дешифратор, кодер, формирователь сигнала выборки канала, блок опроса состояния каналов, распределитель, блок переключения адреса канала, гела, поочередное переключение каналов, запись данных в регистр 7 сдвига.

Второй такт осуществляет переключение выходного триггера 21 в том

35

40

случае, если из регистра 7 сдвига по-зо нератор управляющих сигналов, блок ступает импульс логической 1, т.е. в случае передачи в линию информационных логических 1 частота переда- чи удваивается (2400 Гц).

В устройстве обеспечивается циклическая передача информации в линию, т.е. с началом считывания с регистра 7 сдвига данных о состоянии первого канала в него начинается запись данных о состоянии второго канала и т.д.

Так работает предлагаемое устройство при передаче информации по двухпроводной линии в одном направлении.

Для второго варианта использования устройства, когда необходимо, например, передавать информацию по трем направлениям, с блока 15 запрета снимается сигнал Запрет передачи. Тогда с выхода блока 8 управ- Л1ения вместо сигнала логического О будет подаваться логическая 1. При этом в блоке 18 сравнения задействованы все три элемента И-НЕ А5-47. В этом случае с выхода каждого элемента И-НЕ 45-47 будут поступать данные о состоянии не двенадцати, а, например, четырех каналов. Процесс формирова45

50

55

передачи и приемники импульсных сиг налов, выходы которых подключены к первым входам коммутатора, второй и третий входы которого подключены со ответственно к первому и второму вы ходам формирователя адреса и соотве ственно к первому и второму входам блока проверки на четность, третий и четвертый входы которого подключе ны соответственно к первому и второ му выходам блока опроса состояния канала, первый и второй входы котор го соединены соответственно с первы и вторым выходами коммутатора и с п тым и шестым входами регистра сдвиг седьмой вход которого соединен с вы ходом первого элемента И-НЕ, входы которого подключены к выходу блока проверки на четность, выход регистр сдвига соединен с первым входом второго элемента И-НЕ, выход которо го соединен с первь;м входом блока сравнения, второй вход которого под ключен к выходу блока запрета, перв вход которого соединен с выходом ра пределителя, вход которого подключе к входу дешифратора и к четвертому выходу блока управления, пятый выхо

ния двенадцатиразрядных блоков данных о состоянии-каждого канала и передача их в линии осуществляются аналогично .

5

Формула изобретения

1. Устройство для формирования и передачи дискретных сигналов, со10 держащее блоки определения полярности, блок сравнения, формирователь адреса, первый и второй выходы которого соединены соответственно с первым и вторым входами регистра сдвига,

15 третий и четвертый входы которого подключены соответственно к первому и второму выходам блока управления, третий выход которого соединен с первым входом инвертора, выход которого

20 подключен к входу выходного триггера, отличающееся тем, что, с целью повышения точности формирования и объема передаваемой информации, в него введены коммутатор, блок про

нератор управляющих сигналов, блок

передачи и приемники импульсных сигналов, выходы которых подключены к первым входам коммутатора, второй и третий входы которого подключены соответственно к первому и второму выходам формирователя адреса и соответственно к первому и второму входам блока проверки на четность, третий и четвертый входы которого подключены соответственно к первому и второму выходам блока опроса состояния - канала, первый и второй входы которого соединены соответственно с первым и вторым выходами коммутатора и с пятым и шестым входами регистра сдвига, седьмой вход которого соединен с выходом первого элемента И-НЕ, входы которого подключены к выходу блока проверки на четность, выход регистра сдвига соединен с первым входом второго элемента И-НЕ, выход которого соединен с первь;м входом блока сравнения, второй вход которого подключен к выходу блока запрета, первый вход которого соединен с выходом распределителя, вход которого подключен к входу дешифратора и к четвертому выходу блока управления, пятый выход

которого соединен с первым входом блока передачи, второй вход которого подключен к выходу блока сравнения, третий вход которого соединен с выходом блока переключения адреса ка- нала, вход которого подключен к первому вькоду дешифратора, второй выход которого соединен с входом кодера, первый выход которого соединен с входом формирователя адреса, при это второй вход блока запрета подключен к первому выходу генератора управляющих сигналов, второй выход которого соединен с вторым входом второго элемента И-НЕ, второй выход коде- ра соединен через формирователь сигнала выборки канала с третьим входом

блока опроса состояния канала, выходы блоков определения полярности соединены с входами соответствукяцих приемников импульсных сигналов, а выход блока передачи подключен к второму входу инвертора.

2. Устройство по п. 1, отли- чающееся тем, что блок передачи содержит последовательно соединенные первый и второй элементы И-НЕ, при этом объединенные входы первого элемента И-НЕ являются первым входом блока передачи, вторым входом которого является второй вход второго элемента И-НЕ, выходом блока передачи является выход второго элемента И-НЕ,

| название | год | авторы | номер документа |

|---|---|---|---|

| Система телемеханики | 1982 |

|

SU1152015A1 |

| Система передачи и приема цифровой информации | 1988 |

|

SU1559361A1 |

| УСТРОЙСТВО ИЗБИРАТЕЛЬНОГО ВЫЗОВА | 2005 |

|

RU2299525C1 |

| Устройство для передачи и приема команд телеуправления | 1988 |

|

SU1667135A1 |

| Устройство для контроля неисправностей в цифровой системе связи | 1983 |

|

SU1104574A1 |

| Адаптивная телеметрическая система | 1979 |

|

SU783825A1 |

| Устройство для ввода информации от двухпозиционных датчиков | 1984 |

|

SU1156053A1 |

| УСТРОЙСТВО ДЛЯ КОНТРОЛЯ ДВИЖЕНИЯ ТРАНСПОРТНЫХ СРЕДСТВ | 1995 |

|

RU2096833C1 |

| Адаптивный коммутатор системы телеизмерений | 1985 |

|

SU1309071A1 |

| Устройство для контроля движения транспортных средств | 1987 |

|

SU1538178A1 |

Изобретение относится к технике связи. Цель изобретения - повышение точности формирования и объема информации. Устройство содержит бло- ки 1 определения полярности, приемники 2 импульсных сигналов, коммутатор 3, формирователь (Ф) 4 адреса, блок 5 проверки на четность, элемен(Л Фиг.1

Ф яГ 4 4f Ф

LfJ ф Ф

Фиг.2

Составитель О.Геллер Редактор И.Касарда Техред л.Сердюкова Корректор В.Бутяга

Заказ 6762/58 Тираж 624 Подписное ВНИИПИ Государственного комитета СССР

по делам изобретений и открытий 113035, Москва, Ж-35, Раушская наб., д. 4/5

Производственно-полиграфическое предприятие, г. Ужгород, ул. Проектная, 4

ipuz.

| Стартстопный приемопередатчик | 1977 |

|

SU684764A1 |

| Очаг для массовой варки пищи, выпечки хлеба и кипячения воды | 1921 |

|

SU4A1 |

| Очаг для массовой варки пищи, выпечки хлеба и кипячения воды | 1921 |

|

SU4A1 |

Авторы

Даты

1986-12-15—Публикация

1985-06-17—Подача