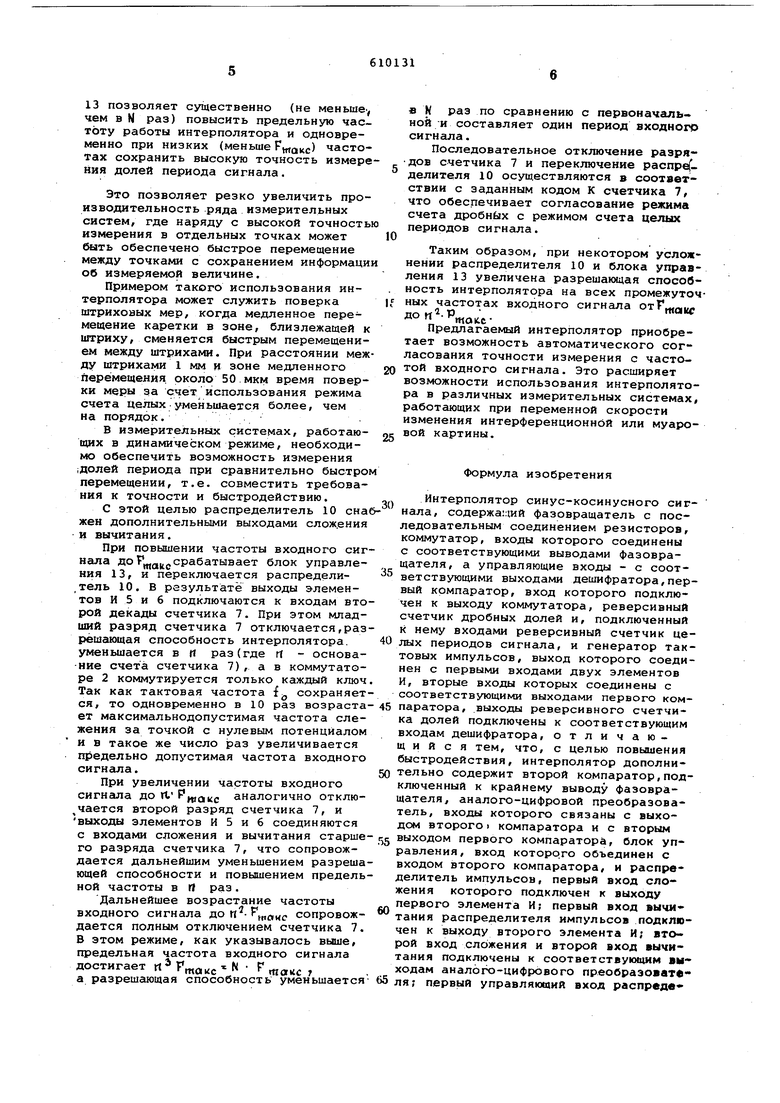

(54) ИНТЕРПОЛЯТОР СИНУС-КОСИНУСНОГО СИГНАЛА пределителя импульсов подключен к выходу второго элемента И, второй вход сложения и второй вход вычитания подключены к соответствующим выходам АЦП Первый управляющий вход распределителя импульсов подключен к первому выхо ду первого компаратора, второй управляющий Вход - к выходу блока управления , остсшьные управляющие входы связаны с соответётвующими выходами всех разрядов реверсивного счетчика дробны долей. Выходы сложения и вычитания распределителя импульсов соединены с соответствующими входами реверсивного счетчика дробных долей и реверсивного счетчика целых периодов сигнала. Распределитель испульсов снабжен дополнительной группой выходов сложения и вычитания, подключенных к соответствующим входам всех разрядов, кроме младшего, реверсивного счетчика дробных долей. На чертеже дана функциональная схе| ма интерполятора. Он содержит фазовращатель с последовательным соединением резисторов Ц- коммутатор 2, компараторы 3 и 4, элементы И 5 и 6, реверсивный счетчик 7дробных долей, дешифратор 8, реверсивный счетчик 9 целых периодов сигнала, распределитель импульсов 10, генератор тактовых импульсов 11, АЦП 12 и блок управления 13. Устройство работает следующим образом. При подаче на крайние выводы фазовращателя напряжений вида 11 gin ф И TJain 1-ф) 7 а на средний вывод напряжения - вида и СОЙ ср , угол ф может быть определен по положению точки нулевого потенциала на фазовращателе. 8исходном состоянии распределитель 10 находится в таком состоянии, при котором выходы элементов И 5 и б подключены к входам сложения и вычитания счетчика 7, преобразователь 12 отключен от входов счетчика 9, -а счётчики 7 и 9 установлены в нулевое положение,вследствие чего дешифратор 8 замыкает первый ключ коммутатора 2. Под действием напряжений U sirt ф., поступающего на вход первого компаратора 3, срабатывает элемент И 5 или 6, и импульсы с выхода генератора 11 через распределитель 10 поступают Соответственно на вход сложения или вычита ния, счетчика 7, Последний через дешифратор 8 осуществляет последовательное переключение ключей коммутато ра 2 до тех пор, пока знак входного напряжения компаратора 3 не измениться на противоположный. При этом интерполятор переходит в режим слежения за точкой с нулевым потенциалом. В этом режиме jno6oe изменение фазы сигнала ф приводит к соответствующему последовательному переключению ключей коммутатора 2, между которыми находится точка с нулевым потенциалом. Перенос целых в счетчик 9 по прежнему осуществляется в момент изменения кода счетчика 7 с 999 на 000. Таким образом, режим слежения за точкой с нулевым потенциалом при малой частоте входного сигнала аналогичен режиму слежения в известном интерполяторе. Если частота входного сигнала начинает увеличиваться и превышает ntaiec то срабатывает блок управлания 13.Под действием его выходного сигнала распределитель 10 отключает выходы элементов И 5 и 6 от входов счетчика 7 и подключает к счетчику 9 выходы АЦП 12. Эти переключения проходят не сразу, а по достижении определенного кода К счетчика 7 в соответствии с управляющими сигналами, поданными на входы распределителя ю. В результате интерполятор переходит в режим счета целых периодов, в счетчике 7 записан код К, а компаратор 3 покдлючеи к выводу делителя, соответствующего этому коду. Принципиально код К может бЫть любым, однако с точки зрения надежности работы интерполятора., он должен отличаться .от кодов 000 и 500, при которых происходит перенос импульса в счетчик 9 и изменение направления счета счетчика 7. Для надежной работы АЩ1 12 на входы компараторов 3 и 4 должны быть поданы напряжений, сдвинутые на 90. В связи с этим код К удобно выбрать равным К 1 J что соответствует подключению компаратора к среднему выводу фазовращателя. В режиме счета целых периодов импульсы счета поступают с выхода АЦП 12 через распределитель 10 непосредственно На входы счетчика 9, а показайия счетчика 7 неизменны . В этом режиме работа интерполятора возможна вплоть до частоты t Р д и ограничивается только частотным диапазоном работы АЦП 12 и счетчика 9 (к компараторам в этом режиме требования по точности не предъявляются). ПРИ уменьшении частоты сигнала до значения, меньшего, чем T tnouc восстанавливается исходное состояние блока управления 13 в распределителе 10. ПРИ этом АЦП 12 отключается, и осуиествляется переход к режиму определения дробных долей периоду, как указано pcrtree. Обратный переход происходит не сразу, а только при поступлении на вход распределителя 10 сигнала с компаратора 3, т.е. в момент достижения нуле.вой точкой узла, к которому подключен этот компаратор. При этом оба режима полностью согласованы при прямом и обратном переключении распредв лителя 10. Таким образом, совместное применение второго компаратора 4, АЦП 12, распределителя 10 и блока управления 13 позволяет существенно (не меньше чем в N раз) повысить предельную частоту работы интерполятора и одновременно при низких (меньше ) частотах сохранить высокую точность измере ния долей периода сигнала. Это позволяет резко увеличить производительность ряда измерительных систем, где наряду с высокой точность измерения в отдельных точках может быть обеспечено быстрое перемещение между точками с сохранением информаци об измеряемой величине. Примером такого использования интерполятора может служить поверка штриховых мер, когда медленное перемещение каретки в зоне, близлежащей к штриху, сменяется быстрым перемещением между штрихами. При расстоянии меж ду штрихами 1 мм и зоне медленного перемещения около 50 мкм время поверки меры за счет использования режима счета целых уменьшается более, чем на порядок. В измерительных системах, работающих в динамическом режиме, необходимо обеспечить возможность измерения ;долей периода при сравнительно быстро перемещении, т.е. совместить требования к точности и быстродействию. С этой целью распределитель 10 сна жен дополнительными выходами слож.ения и вычитания. При повышении частоты входного сиг нала до Р д дсрабатывает блок управления 13, и переключается распредели,тель 10. В результате выходы элементов И 5 и 6 подключаются к входам вто рой декады счетчика 7. При этом младший разряд счетчика 7 отключается,раз решающая способность интерполятора. уменьшается в tt раз(где rt - основаине счета счетчика 7) , а в коммутаторе 2 коммутируется только каждый ключ Так как тактовая частота i сохраняет ся, то одновременно в 10 раз возраста ет максимальнодопустимая частота слежения за точкой с нулевым потенциалом и в такое же число раз увеличивается предельно допустимая частота входного сигнала. При увеличении частоты входного сигнала до Л PHIQKC аналогично отклю чается второй разряд счетчика 7, и выходы элементов И 5 и 6 соединяются с входами сложения и вычитания старше го разряда счетчика 7, что сопровождается дальнейшим уменьшением разреша ющей способности и повышением предель ной частоты в П раз. Дальнейшее возрастание частоты входного сигнала до сопровождается полным отключением счетчика 7. В этом режиме, как указывалось выше, предельная частота входного сигнала достигает « Pma« f такс т а разрешающая способность уменьшается N раз по сравнению с первоначальной /и составляет один период входного сигнала. Последовательное отключение разрядов счетчика 7 и переключение pacnpefделителя 10 осуществляются в соответствии с заданным кодом К счетчика 7, что обеспечивает согласование режима счета дpoбнkx с режимом счета целых периодов сигнала. Таким образом, при некотором усложнении распределителя 10 и блока управления 13 увеличена разрешающая способность интерполятора на всех промежуточных частотах входного сигнала , Д° - и10 сПредлагаемый интерполятор приобретает возможность автоматического согласования точности измерения с частотой входного сигнала. Это расширяет возможности использования интерполятора в различных измерительных системах, работающих при переменной скорости изменения интерференционной или муаровой картины. Формула изобретения Интерполятор синус-косинусного сигнала, содержавший фазовращатель с последовательным соединением резисторов, коммутатор, входы которого соединены с соответствующими выводами фазовращателя, а управляющие входы - с соответствующими выходами дешифратора,первый компаратор, вход которого подключен к выходу коммутатора, реверсивный счетчик дробных долей и, подключенный к нему входами реверсивный счетчик цеJBJx периодов сигнала, и генератор тактовых импульсов, выход которого соединен с первыми входами двух элементов И, вторые входы которых соединены с соответствующими выходами первого компаратора, выходы реверсивного счетчика долей подключены к соответствующим входам дешифратора, отличающийся тем, что, с целью повышения быстродействия, интерполятор дополнительно содержит второй компаратор,подключенный к крайнему выводу фазовращателя, аналого-цифровой преобразователь, входы которого связаны с выходом второго I компаратора и с вторым выходом первого компаратора, блок управления, вход которо.го объединен с входом второго компаратора, и распределитель импульсов, первый вход сложения которого подключен к выходу первого элемента И; первый вход вычитания распределителя импульсов подключен к выходу второго элемента И; второй вход сложения и второй вход вычитания подключены к соответствующим выходам аналого-цифрового преобразователя; первый управляющий вход распредв

лителя импульсов подключен к первому выходу первого коммутатора, второй управляющий вход - к выходу блока управления; остальные управляющие входы связаны с соответствующими выходами всех разрядов реверсивного счетчика дробных долей; выходам сложения и вычитания распределителя импульсов соединены с соответствующими входами реверсивного счетчика дробных долей и реверсивного счетчика целых периодов сигнала.

2. Интерполятор поп.1, отлич а jo Щ и йен тем, что распредели4.-/,ijl

тель импульсов снабжен дополнительной) группой выходов сложения и вычитания, подключенных к соответствующим входам всех разрядов, кроме младшего, ревер5 сивног-о счетчика дробных долей.

Источники информации, принятые во внимание при экспертизе:

1. Драпкин М.Я. и др. Автоматичес1 кая измерительная система к оптическим интерферометрам. Уникальные приборы СЭВ, 1971, В 9, с. 13-18.

2.Shepher«d A.T.Jour«a of МааИЫеТооЕ Beajg f and тгейеагс г аЭбЗ, V. 3, p, 47-59. L,

| название | год | авторы | номер документа |

|---|---|---|---|

| Шаговый электропривод | 1986 |

|

SU1372585A1 |

| ЛИНЕЙНО-КРУГОВОЙ ИНТЕРПОЛЯТОР | 1991 |

|

RU2010293C1 |

| АНАЛОГО-ЦИФРОВОЙ ПРЕОБРАЗОВАТЕЛЬ УГЛА | 1996 |

|

RU2115229C1 |

| Устройство двухступенчатого аналого-цифрового преобразования | 1985 |

|

SU1266003A1 |

| Измеритель амплитудно- и фазочастотной характеристики СВЧ-тракта | 1990 |

|

SU1721546A1 |

| Преобразователь угла поворота вала в код | 1985 |

|

SU1261116A1 |

| Преобразователь угла поворота вала в код | 1980 |

|

SU928387A1 |

| Преобразователь перемещений в код | 1983 |

|

SU1111188A1 |

| Аналого-цифровой преобразователь | 1990 |

|

SU1829117A1 |

| Преобразователь угла поворота вала в код | 1986 |

|

SU1410277A1 |

Авторы

Даты

1978-06-05—Публикация

1976-02-02—Подача