Изобретение относится к области автоматики и вычислительной технике.

Цель изобретения - расширение области применения за счет преобразования сигналов нескольких каналов и повышение достоверности преобразуемой информации.

Известно, что в РЭА основными источг никами помех являются импульсные устройства такие, как статические преобразователи вторичных источников питания, формирователи адресных токов, электромагнитные реле и др. (работающие, как правило, от единого генератора опорной частоты). Наводимые ими в момент переключения помехи имеют импульсный

характер, а уровни зачастую превышают уровни срабатывания логических и аналоговых пороговых устройств, временные характеристики ограничены обычно длительностями не более десятых долей микросекунд.

Кроме того часто необходимо производить преобразование аналоговых сигналов, поступающих по нескольким каналам. Причем информация о конкретном канале должна поступать на выход АЦП не зависимо от того,какой канал в данный момент обрабатывается в АЦП.

Введение дополнительных элементов с вышеуказанными связями позволило при наличии импульсных помех исключить ложоэ ю ю

VJ

ную фиксацию состояния компаратора регистром последовательных приближений, проводить преобразование аналоговых сигналов по нескольким каналам, считывать информацию данного канала независимо от того, какой канал обрабатывается в ДЦП в данный момент, и исключить запись информации в ячейку в момент чтения информации из нее, т.е. позволило расширить функциональные возможности АЦП и повысить достоверность преобразования информации.

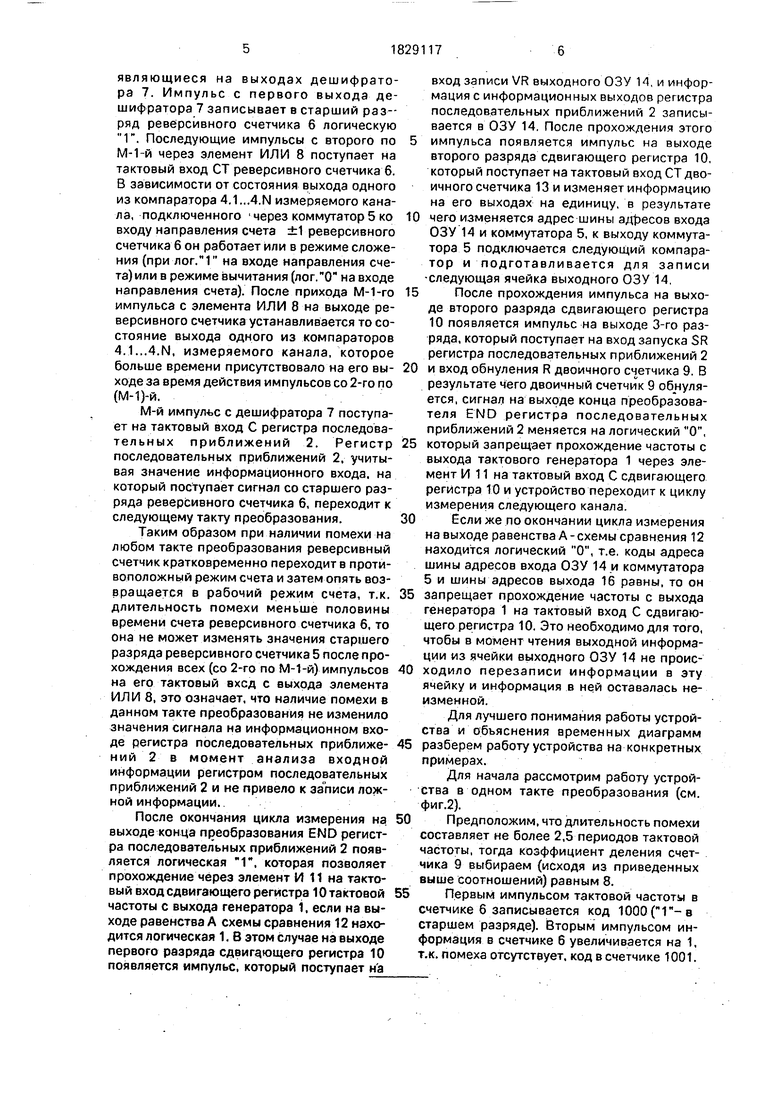

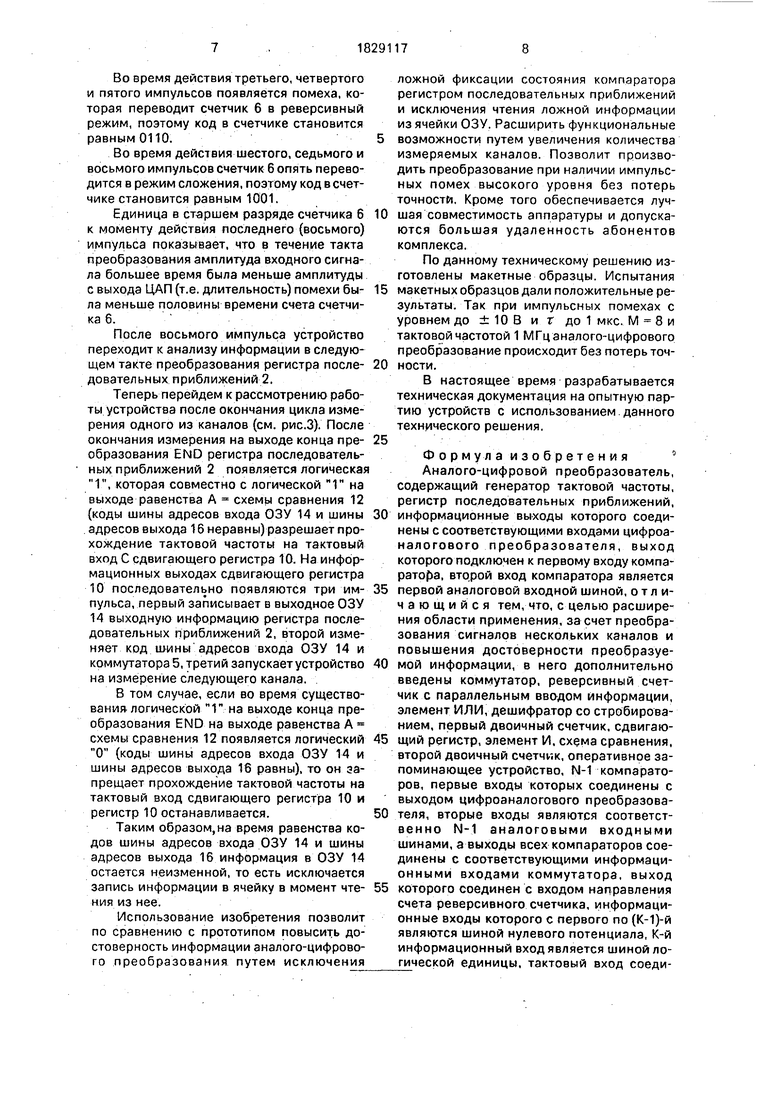

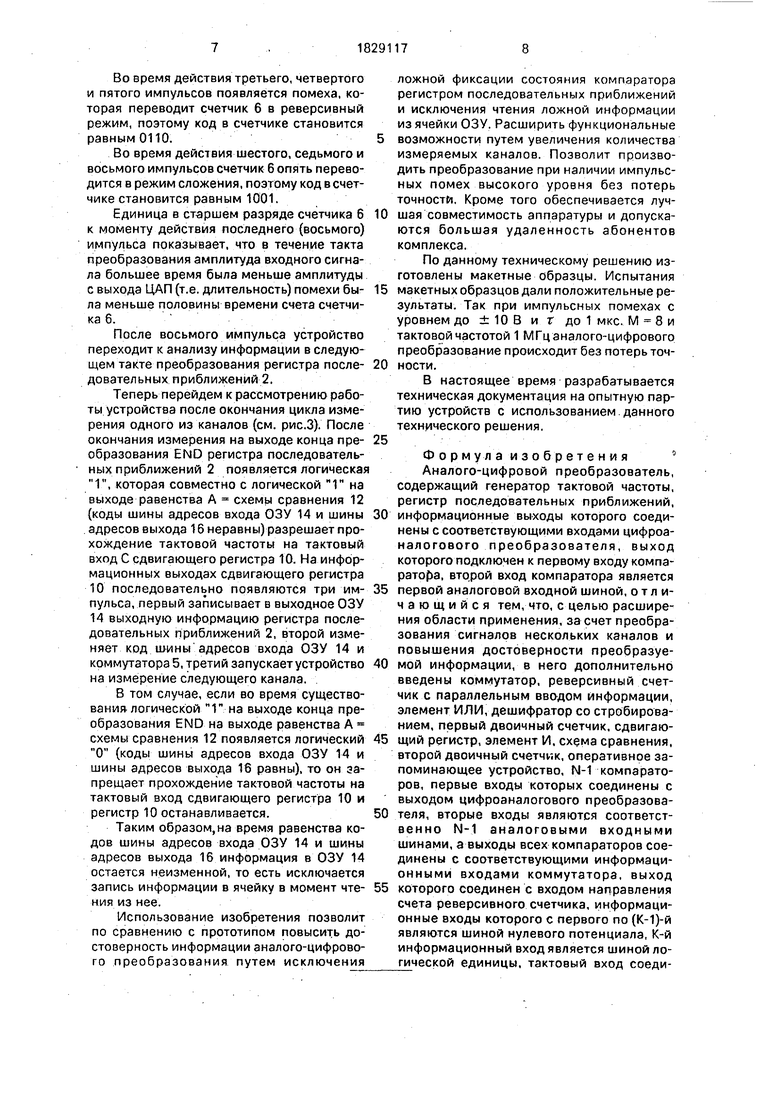

На фиг.1 изображена блок-схема заявляемого устройства; на фиг.2 - временные диаграммы работы устройства в одном такте преобразования; на фиг.З - временная диаграмма работы устройства в конце цикла измерения.

На фиг. 1-3 приняты следующие обозначения; 1 - генератор тактовой частоты; 2 - регистр последовательных приближений; 3 - цифроэналоговый преобразователь; 4.1...4.N - компаратора; 5- коммутатор; 6- реверсивный счетчик с параллельным вводом информации; 7 - дешифратор; 8 - элемент ИЛИ; 9 - двоичный счетчик с обнулением; 10- сдвигающий регистр; 11 - элемент И; 12 - схема сравнения; 13 - двоичный счетчик; 14 - выходное ОЗУ; 15.1...15.N - входы каналов аналого-цифрового преобразователя; 16 - шина адресов выхода; 17- выходная шина.

Предлагаемое устройство включает генератор тактовой частоты 1, регистр последовательных приближений 2, цифроаналоговый преобразователь 3, компараторы 4.1..,4.N, коммутатор 5, реверсивный счетчик с параллельной записью информации 6, дешифратор 7, элемент ИЛИ 8, двоичный счетчик с обнулением 9, сдвигающий регистр 10, элемент И 11 .схема срав нения 12, двоичный счетчик 13, выходное ОЗУ 14. Выход генератора тактовой частоты 1 соединен с вторым входом элемента И11, тактовым входом СТ двоичного счетчика с обнулением 9, и входом стробирования С дешифратора 7.

Информационные выходы регистра последовательных приближений 2 соединены с информационными входами ОЗУ 14, и с информационными входами цифроаналого- вого преобразователя 3. Выход цифроана- логового преобразователя 3 соединен с первыми входами компараторов 4.1...4.N, вторые входы компараторов 4.1..AN являются аналоговыми входами каналов устройства 15.1...15.N. Выходы компараторов 4.1...4.N соединены с соответствующими входами коммутатора 5. Выход коммутатора 5 соединен с входом направления счета 1

реверсивного счетчика с параллельной записью информации 6.

Вход записи параллельной информации V реверсивного счетчика 6 соединен с выходом первого разряда дешифратора 7. Тактовый вход СТ реверсивного счетчика 6 соединен с выходом элемента ИЛИ 8. Входы параллельной информации с 1-го по К-1 реверсивного счетчика 6 соединены с шиной

общего провода, на к-й вход подана логическая 1. Выходы дешифратора 7 со 2-го по (М-1)-й соединены с входами элемента ИЛИ 8, М-й выход соединен с тактовым входом С регистра последовательных приближений

2. Информационные входы дешифратора 7 соединены с соответствующими выходами двоичного счетчика с обнулением 9. Вход обнуления R двоичного счетчика 9 соединен с выходом третьего разряда сдвигающего

регистра 10 и входом запуска SR регистра последовательных приближений.

Тактовый вход С сдвигающего регистра 10 соединен с выходом элемента И 11, выход второго разряда регистра 10 соединен с

тактовым входом СТ двоичного счетчика 13. Первый вход элемента И 11 соединен с выходом конца преобразования END регистра последовательных приближений 2, а третий вход соединен с выходом равенства А схемы сравнения 12. Входы второго числа схемы сравнения 12 соединены с шиной адресов выхода ОЗУ 14 и шиной адресов выхода 16, Входы второго числа схемы сравнения 12 соединены с информационными

выходами счетчика 13, шиной адресов входа ОЗУ 14 и коммутатора 5.

Информационные выходы ОЗУ 14 являются выходной шиной 17 устройства.

Коэффициент деления двоичного счетчика 9 выбирается следующим образом. 2-С

М

5

0

5

где Т-период тактовой частоты генератора 1;

т - максимальная длительность помехи.

Причем М равно числу разрядов дешифратора 7 и связано с числом разрядов К реверсивного счетчика с параллельной записью информации 6 следующим соотношением М 2 +2.

Устройство работает следующим образом.

Импульсы тактовой частоты от генератора тактовой частоты 1 приложенные к двоичному счетчику 9 образуют на его выходе линейные нарастающий код. Этот код дешифратором 7 преобразуется в импульсы, етробированные импульсами тактовой частоты от генератора тактовой частоты 1, появляющиеся на выходах дешифратора 7. Импульс с первого выхода дешифратора 7 записывает в старший раз-ряд реверсивного счетчика 6 логическую 1. Последующие импульсы с второго по М-1-й через элемент ИЛИ 8 поступает на тактовый вход СТ реверсивного счетчика 6. В зависимости от состояния выхода одного из компаратора 4.1...4.N измеряемого канала, подключенного через коммутатор 5 ко входу направления счета ±1 реверсивного счетчика 6 он работает или в режиме сложения (при лог. 1 на входе направления счета) или в режиме вычитания (лог.О на входе направления счета). После прихода М-1-го импульса с элемента ИЛИ 8 на выходе реверсивного счетчика устанавливается то состояние выхода одного из компараторов 4.1...4.N, измеряемого канала, которое больше времени присутствовало на его выходе за время действия импульсов со 2-го по (М-1)-й.

М-й импул-ьс с дешифратора 7 поступает на тактовый вход С регистра последова- тельных приближений 2. Регистр последовательных приближений 2, учитывая значение информационного входа, на который поступает сигнал со старшего разряда реверсивного счетчика б, переходит к следующему такту преобразования.

Таким образом при наличии помехи на любом такте преобразования реверсивный счетчик кратковременно переходит в противоположный режим счета и затем опять возвращается в рабочий режим счета, т.к. длительность помехи меньше половины времени счета реверсивного счетчика 6, то она не может изменять значения старшего разряда реверсивного счетчика 5 после прохождения всех (со 2-го по М-1-й) импульсов на его тактовый вход с выхода элемента ИЛИ 8, это означает, что наличие помехи в данном такте преобразования не изменило значения сигнала на информационном входе регистра последовательных приближений 2 в момент анализа входной информации регистром последовательных приближений 2 и не привело к ззЪиси ложной информации.

После окончания цикла измерения на выходе конца преобразования END регистра последовательных приближений 2 появляется логическая 1. которая позволяет прохождение через элемент И 11 на тактовый вход сдвигающего регистра 10 тактовой частоты с выхода генератора 1, если на выходе равенства А схемы сравнения 12 находится логическая 1, В этом случае на выходе первого разряда сдвигающего регистра 10 появляется импульс, который поступает на

вход записи VR выходного ОЗУ 14, и информация с информационных выходов регистра последовательных приближений 2 записывается в ОЗУ 14, После прохождения этого 5 импульса появляется импульс на выходе второго разряда сдвигающего регистра 10, который поступает на тактовый вход СТ двоичного счетчика 13 и изменяет информацию на его выходах на единицу, в результате

0 чего изменяется адрес шины адресов входа ОЗУ 14 и коммутатора 5, к выходу коммутатора 5 подключается следующий компаратор и подготавливается для записи следующая ячейка выходного ОЗУ 14.

5 После прохождения импульса на выходе второго разряда сдвигающего регистра 10 появляется импульс на выходе 3-го разряда, который поступает на вход запуска SR регистра последовательных приближений 2

0 и вход обнуления R двоичного счетчика 9. В результате чего двоичный счетчик 9 обнуляется, сигнал на выходе конца преобразователя END регистра последовательных приближений 2 меняется на логический О,

5 который запрещает прохождение частоты с выхода тактового генератора 1 через элемент И 11 на тактовый вход С сдвигающего регистра 10 и устройство переходит к циклу измерения следующего канала.

0 ЕСЛИ же по окончании цикла измерения на выходе равенства А-схемы сравнения 12 находится логический О, т.е. коды адреса шины адресов входа ОЗУ 14 и коммутатора 5 и шины адресов выхода 16 равны, то он

5 запрещает прохождение частоты с выхода генератора 1 на тактовый вход С сдвигающего регистра 10. Это необходимо для того, чтобы в момент чтения выходной информации из ячейки выходного ОЗУ 14 не проис0 ходило перезаписи информации в эту ячейку и информация в ней оставалась неизменной.

Для лучшего понимания работы устройства и объяснения временных диаграмм

5 разберем работу устройства на конкретных примерах.

Для начала рассмотрим работу устройства в одном такте преобразования (см. фиг.2).

0 Предположим, что длительность помехи составляет не более 2,5 периодов тактовой частоты, тогда коэффициент деления счетчика 9 выбираем (исходя из приведенных выше соотношений) равным 8.

5 Первым импульсом тактовой частоты в счетчике б записывается код 1000(Г-в старшем разряде). Вторым импульсом информация в счетчике б увеличивается на 1, т.к. помеха отсутствует, код в счетчике 1001.

Во время действия третьего, четвертого и пятого импульсов появляется помеха, которая переводит счетчик 6 в реверсивный режим, поэтому код в счетчике становится равным 0110.

Во время действия шестого, седьмого и восьмого импульсов счетчик 6 опять переводится в режим сложения, поэтому код в счетчике становится равным 1001.

Единица в старшем разряде счетчика 6 к моменту действия последнего (восьмого) импульса показывает, что в течение такта преобразования амплитуда входного сигнала большее время была меньше амплитуды с выхода ЦАП (т.е. длительность) помехи бы- ла меньше половины времени счета счетчика 6.

После восьмого импульса устройство переходит к анализу информации в следующем такте преобразования регистра после- довательных приближений 2.

Теперь перейдем к рассмотрению работы устройства после окончания цикла измерения одного из каналов (см. рис.3). После окончания измерения на выходе конца пре- образования END регистра последовательныхприближений 2 появляется логическая 1, которая совместно с логической Г на выходе равенства А схемы сравнения 12 (коды шины адресов входа ОЗУ 14 и шины адресов выхода 16 неравны) разрешает прохождение тактовой частоты на тактовый вход С сдвигающего регистра 10. На информационных выходах сдвигающего регистра 10 последовательно появляются три им- пульса, первый записывает в выходное ОЗУ 14 выходную информацию регистра последовательных приближений 2, второй изменяет код шины адресов входа ОЗУ 14 и коммутатора 5, третий запускает устройство на измерение следующего канала. .

В том случае, если во время существования логической 1 на выходе конца преобразования END на выходе равенства А схемы сравнения 12 появляется логический О (коды шины адресов входа ОЗУ 14 и шины адресов выхода 16 равны), то он запрещает прохождение тактовой частоты на тактовый вход сдвигающего регистра 10 и регистр 10 останавливается.

Таким образом,на время равенства кодов шины адресов входа ОЗУ 14 и шины адресов выхода 16 информация в ОЗУ 14 остается неизменной, то есть исключается запись информации в ячейку в момент чте- ния из нее.

Использование изобретения позволит по сравнению с прототипом повысить достоверность информации аналого-цифрового преобразования путем исключения

ложной фиксации состояния компаратора регистром последовательных приближений и исключения чтения ложной информации из ячейки ОЗУ. Расширить функциональные возможности путем увеличения количества измеряемых каналов. Позволит производить преобразование при наличии импульсных помех высокого уровня без потерь точности. Кроме того обеспечивается лучшая совместимость аппаратуры и допускаются большая удаленность абонентов комплекса.

По данному техническому решению изготовлены макетные образцы. Испытания макетных образцов дали положительные результаты. Так при импульсных помехах с уровнем до ± 10 В и т до 1 мкс. М 8 и тактовой частотой 1 МГц аналого-цифрового преобразование происходит без потерь точности.

В настоящее время разрабатывается техническая документация на опытную партию устройств с использованием данного технического решения.

Ф о р м у л а и з о б р е т е н и я°

Аналого-цифровой преобразователь, содержащий генератор тактовой частоты, регистр последовательных приближений, информационные выходы которого соединены с соответствующими входами цифроа- налогового преобразователя, выход которого подключен к первому входу компаратора, второй вход компаратора является первой аналоговой входной шиной, отличающийся тем, что, с целью расшире- ния области применения, за счет преобразования сигналов нескольких каналов и повышения достоверности преобразуемой информации, в него дополнительно введены коммутатор, реверсивный счетчик с параллельным вводом информации, элемент ИЛИ, дешифратор со стробирова- нием, первый двоичный счетчик, сдвигающий регистр, элемент И, схема сравнения, второй двоичный счетчик, оперативное запоминающее устройство, N-1 компараторов, первые входы которых соединены с выходом цифроаналогового преобразователя, вторые входы являются соответственно N-1 аналоговыми входными шинами, а выходы всех компараторов соединены с соответствующими информационными входами коммутатора, выход которого соединен с входом направления счета реверсивного счетчика, информационные входы которого с первого по (К-1)-й являются шиной нулевого потенциала, К-й информационный вход является шиной логической единицы, тактовый вход соединен с выходом элемента ИЛИ, выход - с информационным входом регистра последовательных приближений, вход записи - с выходом первого разряда дешифратора, выходы которого с второго по (М-1.)-й разряд соединены с входами элемента ИЛИ, выход М-го разряда соединен с тактовым входом регистра последовательных приближений, информационные входы соединены с соответствующими выходами первого двоично го счетчика, вход стробирования соединен с выходом тактового генератора и объединен с первым входом элемента И и с тактовым входом первого двоичного счетчика, вход обнуления которого соединен с входом запуска регистра последовательных приближений и выходом третьего разряда сдвигающего регистра, выход, второго разряда которого соединен с тактовым входом второго двоичного счетчика, а выход первого разряда соединен с входом записи оперативного запоминающего устройства, тактовый вход сдвигающего регистра соединен с выходом элемента И, второй вход которого соединен с выходом конца преобразования

регистра последовательных приближений, третий вход соединен с выходом равенства схемы сравнения, первые входы информации которой объединены с первыми адресными входами оперативного

запоминающего устройства и коммутатора и соединены с информационными выходами второго двоичного счетчика, вторые входы схемы сравнения объединены с вторыми адресными входами оперативного запоминающего устройства и являются цифровой входной шиной, информационные входы оперативного запоминающего устройства соединены с информационными выходами регистра последовательных приближений, а

информационные выходы являются выходной шиной.

J 3 45 б 7 8

| название | год | авторы | номер документа |

|---|---|---|---|

| Аналого-цифровой преобразователь | 1990 |

|

SU1795548A1 |

| Программируемый источник питания | 1988 |

|

SU1597875A1 |

| Цифроаналоговый преобразователь с автокалибровкой | 1989 |

|

SU1683176A1 |

| Цифроаналоговый генератор телевизионного сигнала | 1989 |

|

SU1654978A1 |

| Способ локальной радиотелефонной связи и система для его осуществления | 1991 |

|

SU1831767A3 |

| ПРЕОБРАЗОВАТЕЛЬ ПАРАЛЛЕЛЬНОГО КОДА В ПОСЛЕДОВАТЕЛЬНЫЙ | 2000 |

|

RU2187887C2 |

| Цифроаналоговая система сбора и обработки информации | 1986 |

|

SU1363271A1 |

| Устройство для измерения отношения размаха сигнала к эффективному значению флюктуационной помехи | 1988 |

|

SU1601781A1 |

| УСТРОЙСТВО СИНХРОНИЗАЦИИ М-ПОСЛЕДОВАТЕЛЬНОСТИ | 1983 |

|

SU1840196A1 |

| СЕЛЕКТОР ИМПУЛЬСОВ ЗАДАННОЙ КОДОВОЙ КОМБИНАЦИИ | 1994 |

|

RU2076455C1 |

Изобретение относится к автоматике и вычислительной технике. Целью изобретения является расширение области применения за счет преобразования сигналов нескольких каналов и повышение достоверности преобразуемой информации. Аналого-цифровой преобразователь содержит генератор тактовой частоты, регистр последовательныхприближений, информационные выходы которого соединены с входами цифроаналогового преобразователя, выход которого подключен к первому входу компаратора, второй вход компаратора является первой аналоговой входной шиной, N-1 компаратор, коммутатор, реверсивный счетчик с параллельным вводом информации, элемент ИЛИ, дешифратор со стробированием, первый двоичный счетчик, сдвигающий регистр, элемент И, схему сравнения, второй двоичный счетчик, оперативное запоминающее устройство. Зил. Ё

| Кондалев А.И | |||

| и др | |||

| Преобразователи формы информации для малых ЭВМ, 1982.- Киев: Наукрва думка, 1982, с.209-212, рис.71 | |||

| Гитис Э.И | |||

| и др | |||

| Аналого-цифровые преобразователи, - М.: Энергия, 1981, с.235, рис.6-7а. |

Авторы

Даты

1993-07-23—Публикация

1990-08-20—Подача