1 :

Изобретение относится к импульсной технике.

Известен двоичный счетчик с контролем ошибок, содержащий N счетных разрядов, состоящих из триггерных ячеек и логических элементов И, ИЛИ, несколько компараторов, осуществляющих сравнение сигналов счетных разрядов , блок селекции, каждый из которых соединяется сГ выходами компараторов, и управляющее устройство Г Данный счетчик обладает сложной схемой и не обеспечивает надлежащего .быстродействия.

Наиболее близким по технической сущности к предлагаемому является двоичный счетчик, содержащий 2N входовых логических элемента ИЛИ и N разрядов, каждый из которых содержит основной и исполнительный триггеры и четыре двухвходовых логических элеменta И, причем прямой и инверсный выходы основного триггера разряда через первые два двухвходовых логических элемента И, вторые входы которых соединены с прямым выходом основного триггера предыдущего разряда, прдклю чены соответственно к нулевому и единичному входам дополнительного триггера, прямой и инверсный выходы которого через два других двухвходовых логических элемента И, вторые входы кот торык соединены с инверсным выходом основного триггера предыдущего разря- да, подключены соответственно к единичному и нулевому входам основного триггера данного разряда 2.

Недостатком данного.счетчика является недостаточная точность и быс родействие.

Целью изобретения является улучше-т ние точности контроля и повышение быстродействия.

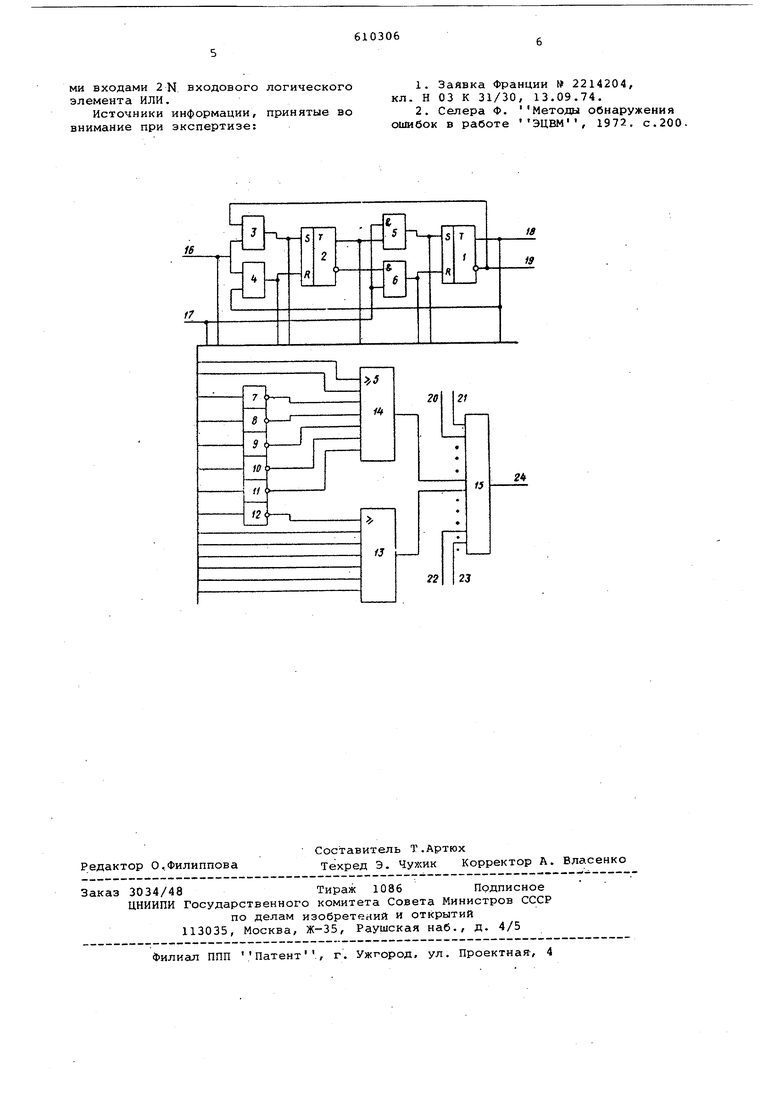

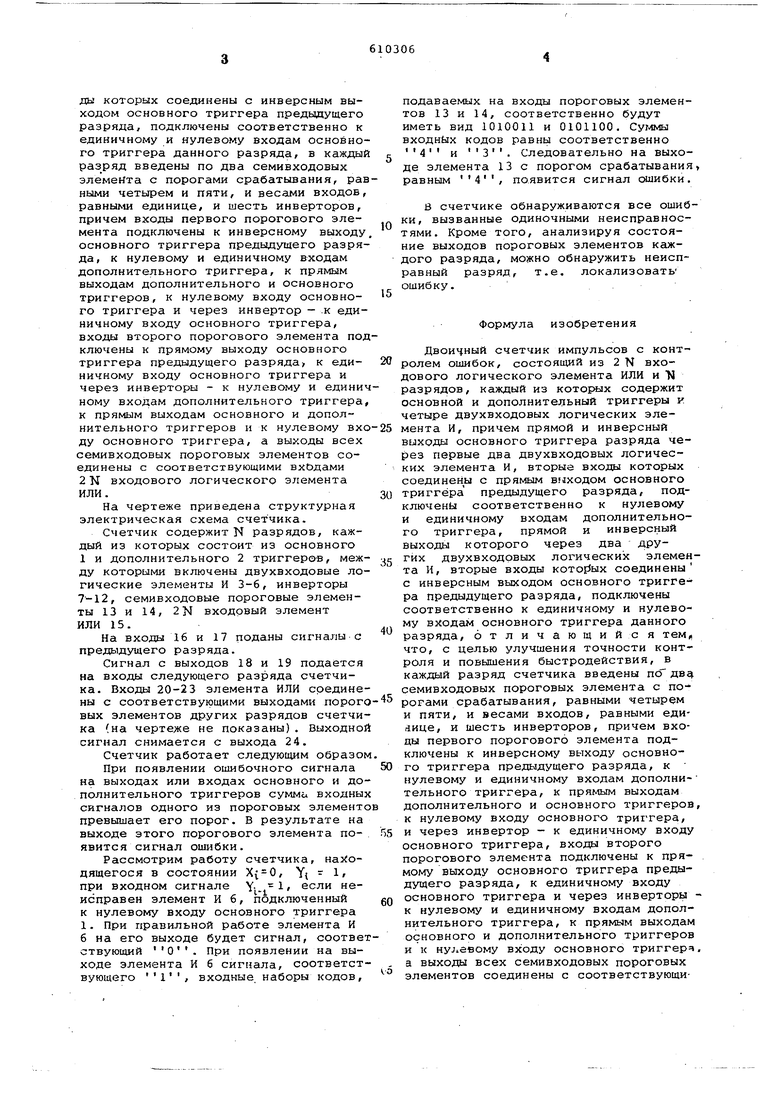

Поставленная цель достигается тем, что в двоичный счетчик, состоящий из 2N входового логического элементаИЛИ и N разрядов, каждый из которых содержит основной и дополнительный триггеры и четыре двухвходовых логических элемента И, причем прямой и инверсный выходы основного триггера разряда через первые два двухвходовых логических элемента И, вторые входы которых соединены с прямым выходом основного триггера предыдущего разряд подключены соответственно к нулевому и единичному входам дополнительного триггера, примой и инверсный выходы которого через два других двухвходовых логических элемента И, вторые входы которых соединены с инверсным выходом основного триггера предыдущего разряда, подключены соответственно к единичному и нулевому входам основно го триггера данного разряда, в кажды разряд введены по два семивходовых элемента с порогами срабатывания, ра ными четырем и пяти, и весами входов равными единице, и шесть инверторов, причем входы первого порогового элемента подключены к инверсному выходу основного триггера предыдущего разря да, к нулевому и единичному входам дополнительного триггера, к прямым выходам дополнительного и основного триггеров, к нулевому входу основного триггера и через инвертор - к единичному входу основного триггера, входы второго порогового элемента под ключены к прямому выходу ОСНОВЕ1ОГО триггера предыдущего разряда, к единичному входу основного триггера и через инверторы - к нулевому и едини ному входам дополнительного триггера к прямым выходам основного и дополнительного триггеров и к нулевому вхо ду основного триггера, а выходы всех семивходовых пороговых элементов соединены с соответствующими вхЬдами 2 N входового логического элемента ИЛИ. На чертеже приведена структурная электрическая схема счетчика. Счетчик содержит N разрядов, каждый из которых состоит из основного 1 и дополнительного 2 триггеров, меж ду кoтopыtvш включены двухвходовые ло гические элементы И 3-6, инверторы 7-12, семивходовые пороговые элементы 13 и 14, 2N входовый элемент ИЛИ 15. На входы 16 и 17 поданы сигналы с предыдущего разряда. Сигнал с выходов 18 и 19 подается на входы следующего разряда счетчика. Входы 20-23 элемента ИЛИ соединены с соответствующими выходами порого вых элементов других разрядов счетчика (на чертеже не показаны). Выходной сигнал снимается с выхода 24. Счетчик работает следуюнщм образом При появлении ошибочного сигнала на выходах или входах основного и дополнительного триггеров сумме входных сигналов одного из пороговых элементо превышает его порог. В результате на выходе этого порогового элемента появится сигнал ошибки. Рассмотрим работу счетчика, находящегося в состоянии Х(0, У( - If при входном сигнале Y-,.,- 1 если неисправен элемент И 6, подключенный к нулевому входу основного триггера 1. При правильной работе элемента И 6 на его выходе будет сигнал, соответ ствующий О . При появлении на выходе элемента И 6 сигнала, соответствующего , входные, наборы кодов. подаваемых на входы пороговых элементов 13 и 14, соответственно будут иметь вид lOlOOil и 0101100. Суглмы входнЬ1х кодов равны соответственно Следовательно на выходе элемента 13 с порогом срабатывания появится сигнал сяиибки. равным в счетчике обнаруживаются все ошибки, вызванные одиночными неисправностями. Кроме того, анализируя состояние выходов пороговых элементов каждого разряда, можно обнаружить неисправный разряд, т.е. локализовать ошибку. . . Формула изобретения Двоичный счетчик импульсов с контролем ошибок, состоящий из 2 N входового логического элемента ИЛИ и J разрядов, каждый из которых содержит основной и дополнительный триггеры и четыре двухвходовых логических элемента И, причем прямой и инверсный выходы основного триггера разряда через первые два двухвходовых логических элемента И, вторые входы которых соединены с прямым выходом основного триггера предыдущего разряда, подключенй соответственно к нулевому и единичному входам дополнительного триггера, прямой и инверсный выходаа которого через два других двухвходовых логических элемента И, вторые входы котоЕ1ых соединены с инверсным выходом основного триггера предыдущего разряда, подключены соответственно к единичному и нулевому входам основного триггера данного разряда, отличающийся тем что, с целью улучшения точности контроля и повышения быстродействия, в каждый разряд счетчика введены псГ дв семивходовых пороговых элемента с порогами срабатывания, равными четырем и пяти, и весами входов, равными еди11ице, и шесть инверторов, причем входы первого порогового элемента подключены к инверсному выходу основного триггера предыдущего разряда, к нулевому и единичному входам дополнительного триггера, к прямым выходам дополнительного и основного триггеров, к нулевому входу основного триггера, и через инвертор - к единичному входу основного триггера, входы второго порогового элемента подключены к прямому выходу основного триггера предыдущего разряда, к единичному входу основного триггера и через инверторы к нулевому и единичному входам дополнительного триггера, к прямым выходам основного и дополнительного триггеров и к HyjieeoMy входу основного триггерч. а выходы всех семивходовых пороговых элементов соединены с соответствующими входами 2N входового логического элемента ИЛИ.

Источники информации, принятые во внимание при экспертизе:

1.Заявка Франции № 2214204, кл. Н 03 К 31/30, 13.09.74.

2.Селера Ф. Методы обнаружения ошибок в работе ЭЦВМ, 1972. с.200.

| название | год | авторы | номер документа |

|---|---|---|---|

| Двойчный счетчик со встроеннымКОНТРОлЕМ | 1979 |

|

SU815921A1 |

| Двоично-десятичный счетчик в коде 8-4-2-1 | 1986 |

|

SU1415439A1 |

| Вычитающее у тройство с контролем | 1977 |

|

SU690481A1 |

| Устройство для защиты трехфазного частотно-регулируемого привода от неполнофазного режима питания | 1985 |

|

SU1377950A1 |

| Многопороговый логический элемент | 1977 |

|

SU705684A1 |

| СПОСОБ КОРРЕКЦИИ ПОГРЕШНОСТЕЙ АНАЛОГО-ЦИФРОВОГО ПРЕОБРАЗОВАНИЯ И УСТРОЙСТВО ДЛЯ ЕГО ОСУЩЕСТВЛЕНИЯ | 2007 |

|

RU2326494C1 |

| УСТРОЙСТВО ПОИСКА ИНФОРМАЦИИ | 2006 |

|

RU2313128C1 |

| МНОГОРАЗРЯДНЫЙ УПРАВЛЯЕМЫЙ ДЕЛИТЕЛЬ ЧАСТОТЫ | 1996 |

|

RU2119248C1 |

| Двоично-десятичный счетчик в коде 8-4-2-1 | 1987 |

|

SU1462474A1 |

| АРИФМЕТИКО-ЛОГИЧЕСКОЕ УСТРОЙСТВО ДЛЯ СЛОЖЕНИЯ, ВЫЧИТАНИЯ И УМНОЖЕНИЯ ЧИСЕЛ ПО МОДУЛЮ | 2019 |

|

RU2711051C1 |

Авторы

Даты

1978-06-05—Публикация

1976-03-29—Подача