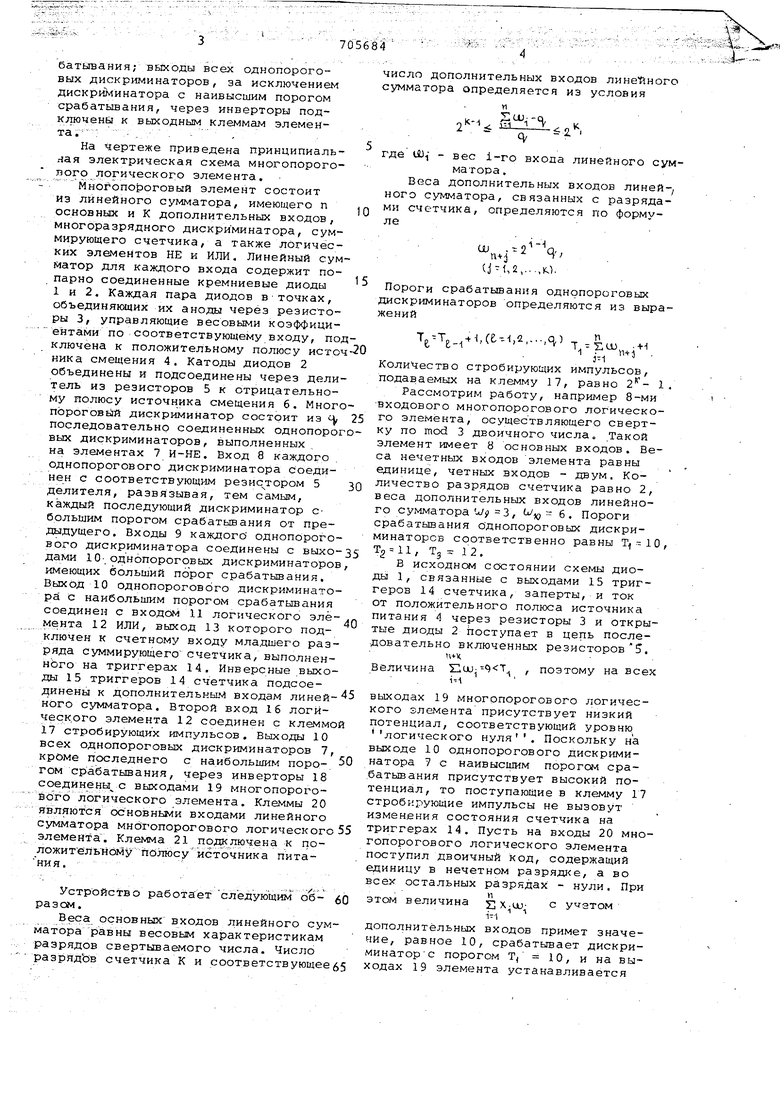

Изобретение относится к рбларти автоматики ивычислительной техники в частности к пороговым логическим элементам. Известен пороговый логический элемент, содержащий линейный суммат дискриминатор 1. Недостатком известного устройства является сложность устройства. Известен многопороговый логический элемент, легко реализуемый в интегральном исполнении, содержащий линейный сумматор, выполненный на резисторах, управляемый входными диодами, многопороговый дискриминатор, презназначенные для реализации функции свертки по mod 2 2, Недостатком известного мнргопоро гового логического элемента являются его низкие функциональные возмотк ности, не позволяющие использовать логический элемент для организации свертки- по более высоксму модулю, чем mod 2. Кроме того, наличие только одного выхода у известных элементов не позволяет принципиально сформировать результат свертки двоичного числа по модулю с 2, ч Целью изобретения является возможность реализации функции свертки двоичного числа по любому модулю. Для этогомногопороговый логический элемент, .содержащий линейный сумматор, состоя щий из входных диодов, аноды которых через соотвётствуюгцие резисторы подключены к источнику питания и к анодам соответствующих разделительных диодов, катоды которых соединены с входом резисторного делителя, выходы которого подключены к .входам соответствующих однопо- poroBbDi дискриминаторов на элементах И-НЕ, дополнительно содержит суммирующий счетчик, инверторы и двухвходовой логический .элемент ИЛИ один вход которого соединен с выходом однопорогового дискриминатора с наинысшим порогом срабатывания, второй - с клеммой стробирующих импульррв, а выкод подключен к счетному входу младшего разряда суммирующего счетчика, инверсные выходы раз-. рядов счетчика| соединены с дополнительными входами линейного сумматора, причем выход каждого однопорогового дискриминатора соединен с входами всех однопороговых дискркми наторов, имеющих меньший порог ерабатьлвания; выходы всех однопороговых дискриминаторов, за исключением дискриминатора с наивысшим порогом срабатьшания, через инверторы подключена к выходным клеммам элемента. ; . - На чертеже приведена принципиальная электрическая схема многопороголого логического элемента. Многопороговый элемент состоит из линейного сумматора, имеющего п основных и К дополнительных входов, многоразрядного дискриминатора, суммирующего счетчика, а также логических элементов НЕ и ИЛИ. Линейный сум матор для каждого входа содержит попарно соединенные кремниевые диоды 1 и 2. Каждая пара диодов в точках, объединяющих их аноды через резисторы 3, управляющие весовыми коэффициентами по соответствующему входу, по ключена к положительному полюсу исто ника смещения 4. Катоды диодов 2 объединены и подсоединены через дели тель из резисторов 5 к отрицательному полюсу источника смещения 6. Мног пороговйй дискриминатор состоит из последовательно соединенных однопоро вых дискриминаторов, выполненных., на элементах 7 И-НЕ. Вход 8 каждого однопорогового дискриминатора соединен с соответствующим резис тором 5 делителя, развязывая, тем самым, каждый последующий дискриминатор сбольшим порогом срабатывания от предыдущего. Входы 9 каждого однопорого вого дискриминатора соединены с выхо дами 10-, однопороговых дискриминаторов имеющих больший порог срабатывания. Выход 10 однопорогового дискриминато рА С наибольшим порогом срабатьтания соединен с входом 11 логического эле мента 12 ИЛИ, выход 13 которого подключен к счетному входу младшего раз ряда суммирующего счетчика, выполненнЬго на триггерах 14. Инверсные выхо ды 15 триггеров 14 счетчика подсоединены к дополнительным входам линейного сумматора. Второй вход 16 логического элемента 12 соединен с клеммо 17 стробирующих импульсов. Выходы 10 всех однопороговых дискриминаторов 7 кроме последнего с наибольшим порогом срабатывания, через инверторы 18 соединеннее выходами 19 многопорогового логического элемента. Клеммы 20 являются основными входами линейного сумматора мнбгопорогового логического элемента . Клемма 21 подключена к положитеЛЬнбмупоЗтюсу источника питания. Устройство работает следующим образом. Веса ОСНОВНЫХ входов линейного сум матора равны весовым характеристикам разрядов свертываемого числа. Число разрядЪв счетчика К и соответствующее число дополнительных входов линейного умматора определяется из условия м ...K где iD{ - вес i-ro входа линейного сумматора. Веса дополнительных входов линейного сумматора, связанных с разрядами счетчика, определяются по формуле, n.. (j-1,2,...,K.l. Пороги срабатьшания однопороговых дискриминаторов определяются из выраженийт.,.-се-,2,..,я5 т,4%.Г . Количество стробирующих импульсов, подаваемых на клемму 17, равно 1, Рассмотрим работу, например 8-ми входового многопорогового логического элемента, осуществляющего свертку по mod 3 двоичного числа. Такой элемент имеет 8 основных входов. Веса нечетных входов элемента равны единице, четных входов - двум. Количество разрядов счетчика равно 2, веса дополнительных входов линейного сумматора и/J 3, б. Пороги срабатьтания однопороговых дискриминаторов соответственно равны , То -11, Тч 12. В исходном состоянии схемы диоды 1, связанные с выходами 15 триггеров 14 счетчика, заперты, и ток от положительного полюса источника питания 4 через резисторы 3 и открытые диоды 2 поступает в цепь последовательно включенных резисторов . величина 11ии- «)Т , поэтому на всех Ь-( выходах 19 многопорогового логического элемента присутствует низкий потенциал, соответствующий уровню логического нуля . Поскольку на выходе 10 однопорогового дискриминатора 7 с наивысшим порогом срабатывания присутствует высокий потенциал, то поступающие в клемму 17 стробирующие импульсы не вызовут изменения состояния счетчика на триггерах 14. Пусть на входы 20 многопорогового логического элемента поступил двоичный код, содержащий единицу в нечетном разрядке, а во всех остальных разрядах - нули. При 11 этом величина sx-uu- с учетом дополнительных входов примет значение, равное 10, срабатывает дискриминатор с порогом Т( 10, и на выходах 19 элемента устанавливается

код 01, соответствующий результату свертки по mod 3, поступившего даоичного кода. Поскольку на выходе 10 однопорогового дискриминатора 7 с чаивысшим порогом срабатывания присутствует высокий потенциал, то поступающие на клемму 17 стробирующие импульсы не вызовут изменения состояния счетчика на триггерах 14.

Пусть теперь на входы 20 многопорогового логического элемента поступил код, содержащий единицу в нечетном разряде и две единицы в чётных. При этом величина :& с учетом дополнительных входов примет . значение, равное 14, на выходе 10 однопорогового дискриминатора 7 с наивысшим () порогом срабатывания установится низкий уровень . напряжения, и первый же стробирующий.импульс, поступающий на клемму 17, переключит младший разряд счетчика в единичное состояние. Это приведет к тому, что величина с

учетом дополнительных ёходов прим-ет значение, равное 11. При этом на выходе 10 дискриминатора 7 с порогом устанавливается высокий потенциал, и стробирующиё импульсы, поступающие на клемму 17, не будут изменять состояния счетчика на триггерах 14. На выходах дискриминаторов с порогами и Tt«lO установятся (соответственно) низкий и высокий уровень напряжения, что приведет к формированию на выходах 19 элемента кода 10, соответствующего результату свертки по mod 3, поступившего двоичного кода.

Аналогичным образом происходит работа многЪпорогового логического элемента и при других комбинациях

входных сигналов. Состояния элементов схемы для всевозможных значений

|х,и.,

сведены в таблицу.

величины

| название | год | авторы | номер документа |

|---|---|---|---|

| Многопороговый логический элемент | 1985 |

|

SU1272499A2 |

| Многопороговый логический элемент четности | 1977 |

|

SU660261A2 |

| Многопороговый логический элемент | 1988 |

|

SU1575307A1 |

| МНОГОПОРОГОВЫЙ ЛОГИЧЕСКИЙ ЭЛЕМЕНТ | 2000 |

|

RU2189110C2 |

| Многопороговый логический элемент четности | 1980 |

|

SU928653A1 |

| Многопороговый логический элемент четности | 1976 |

|

SU608266A1 |

| Многопороговый логический элемент четности | 1980 |

|

SU900455A2 |

| Многопороговый логический элемент | 1990 |

|

SU1728966A2 |

| Многопороговый логический элемент | 1980 |

|

SU936427A1 |

| Многопороговый логический элемент | 1983 |

|

SU1112564A2 |

Формула изобретения

Многопороговый логический элемент, содержащий линейный сумматор, состоящий из входных дисдов, аноды которых через соответствующие резисторы подключены к источнику питания и к анодам соответствующих разделительных диодов, катоды которых соединены с входом резисторного делителя, выходы которого подключены к входам соответствующих однопороговых дискриминаторов на элементах И-НЕ, о т л ичающийс я тем, что, с целью

реализации функциисвертки двоичного числа по любому модулю, он дополнительно содержит суммирующий счетчик, инверторы и двухвходовой логический элемент ИЛИ, один вход которого соединен с выходом однопорогового дискриминатора с наивысшим порогом срабатывания, второй - с клеммой стробирующих импульсов, а выход подклю.чен К счетному входу младшего разряд суммирующего счетчика, инверсные выходы разрядов которого соединены с дополнительными входами линейного сумматора, причем выход каждого однопорогоБОГо дискриминатора соединён с входами всех одйопороговых дискриминаторов, имеющих меньший порог срабатьюания; выходы всех Ьднопороговых дискриминаторов, за исключением дискриминатора с наивысшим порогом срабатывания, через инBeptopu подключены к выходным клеммам элемента.

и

г

ff

Источники информации, принятые во внимание при экспертизе

f-s-19

«

13

18

Авторы

Даты

1979-12-25—Публикация

1977-12-05—Подача