Изобретение относится к вьяислительной технике и может быть использовано для хранения, считывания, а также электрической :перезаписи информации (микропрограмм, таблиц функций, значений констант и т.д.) в цифровых вычислительньгх машинах и устройствах дискретной автоматики.

Известны полупостоянные запоминающие устройства (ПОЗУ), содержаише накопитель матричного типа, допускающий электрическую перезапись (репрограммирование) хранящейся в нем информации Сх} . В состав таких ППЗУ обычно входят также входной регистр, дешифраторы, элементы И (схемы совпадения) и ИЛИ, входные и выходные

ключи. Наиболее близким к изобретению по схеме организации является запоминающее устройство, содержащее накопитель матричного типа, входы которого подключены к выходам первых элементов И, одни из входов которых соединены с выходами первого дешифратора, вход которого подключен к одному из выходов входного регистра, другой выход которого соединен со входом второго дешифратора, выходы второго дешифрат

ра подключены к первым входам вторых элементов И, выходы которых подключены к вервым входам элементов ИЛИ, а выходы элементов ИЛИ соединены с первыми входами выходных ключей, вторые входы которых подключены к выходам накопителя 2j , Однако для осуществления стирания старой и записи новой информации в нем требуется большое число дополнительных выводов, что снижает надежность функционирования устройства.

Целью изобретения является повышение надежности. В предлагаемом устройстве эгб достигается тем, что оно содержит ключ записи и ключ стирания и считывания, выход которого подключен к выходу клюна записи и ко вторым входам первых элементов И, ход ключа записи подключен ко вторым входам вторых элементов И, а вход ключа стирания и считывания соединен со вторымк входами элементов ИЛИ.

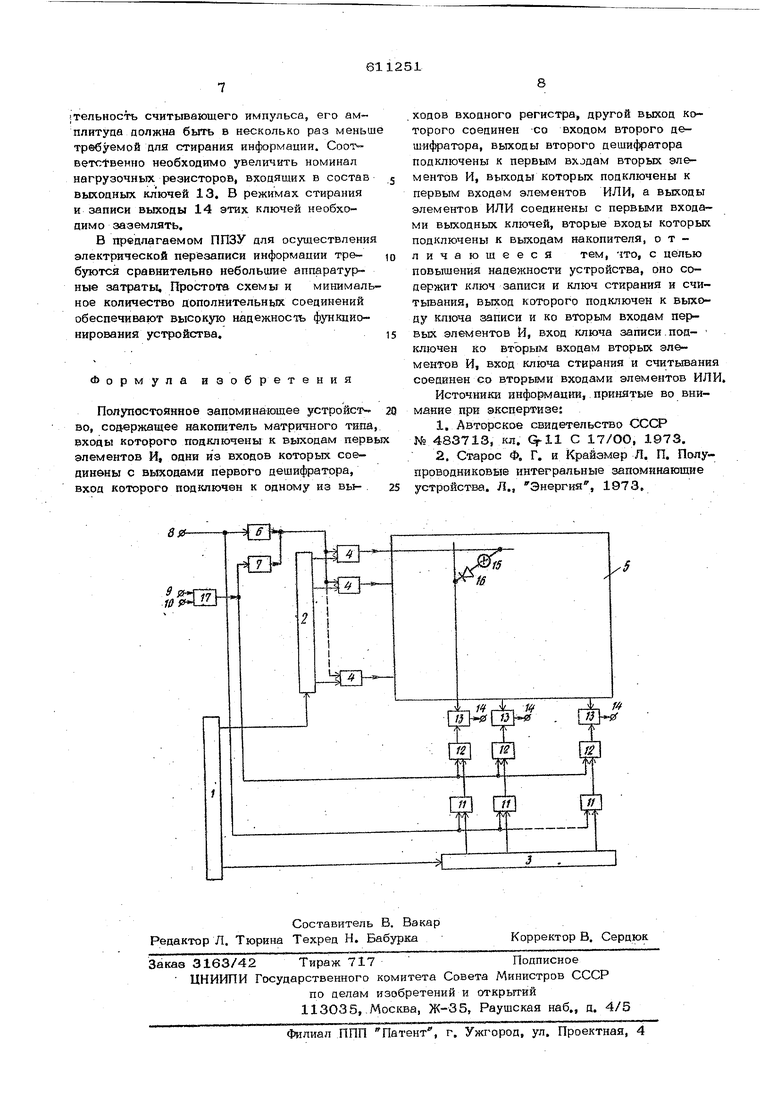

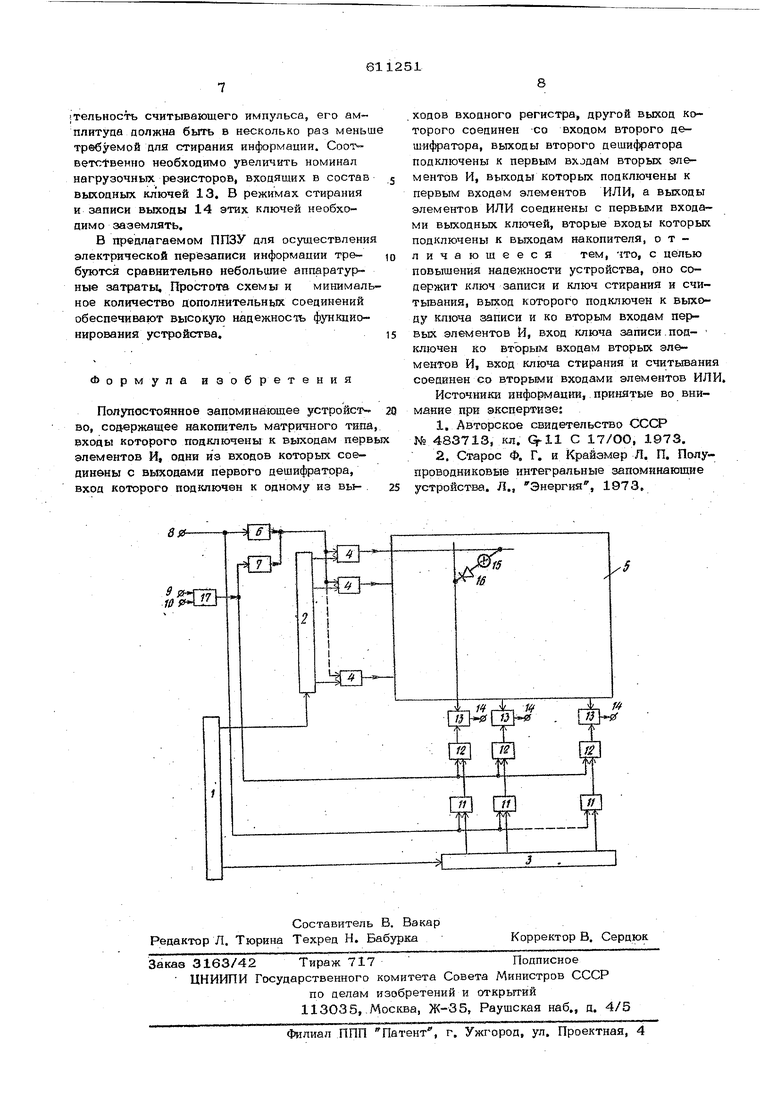

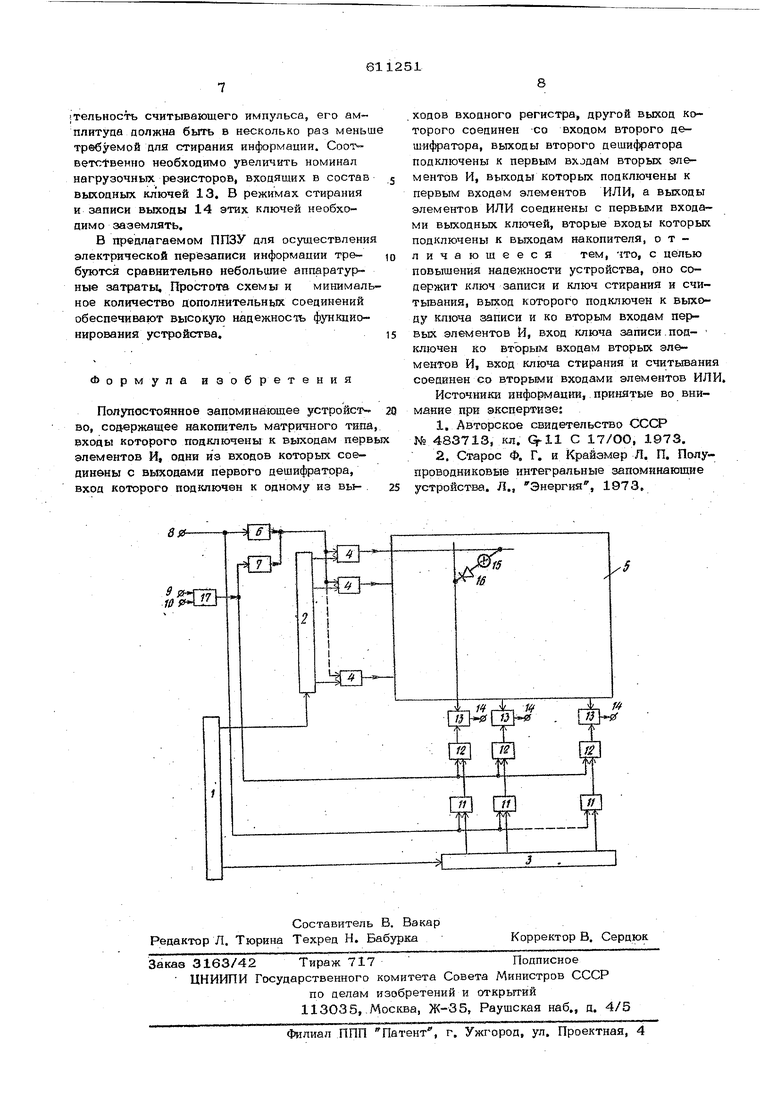

На чертеже показана схема предлагаемого устройства.

Оно содержит входной регистр 1, один из выходов которого, представляюишй собой

совокупность шин от первой группы разрядов кода адреса, подключен ко входу первого дешифратора 2, а другой выход (совокупность шин от второй группы разрядов кода адреса) - ко входу второго дешифратора 3. Выходы дешифратора 2 подключены к первым (управляющим)входам первых элементов И 4, выходы которых соединены со входами накопителя 5, Вторие входы элементов И 4 подключв цы к соединенным между собой выходам ключе записи 6 и ключа стирания и считывания 7, Вх 8 ключа записи 6 предназначен для подачи служебного сигнала Запись } входы 9 и 10, соответственно, служат для подачи служебных сигналов Стирание и Считывание, Выходы второго дешифратора 3 подключены к первым входам вторых элементов И 11, вторые входы которых соединены со входом 8, Выходы элементов И 11 подключены к первьгм входам элементов ИЛИ 12, вторые входы которых подключены ко- входу ключа стирания и считывания 7, Выходы элеMeHToiB ИЛ.И,12 соединены с первыми входами выходных ключей 13, вторые входы которых подключены к выходам накопителя 5. Вых1эды 14 ключей 13 служат для выдачи сигналов считывания, В накопителе 5 условно показан запоминающий элемент, состоящий из последовательно соенииенного бистабильного переключателя IS и полупррводникового диода 16, Элемент ИЛИ 17 подключён ко входу ключа стирания и считывания 7и ко входам элементов ИЛИ 12. ; Предлагаема ПШУ работает в трех режимах: записи, стирания и считывания, В режиме записи во входной регистр 1 поочередно заносятся коды адреса тех ячеек накопителя 5, в которые требуется запйсать информацию. Первая группа разрядов кода ощэеделает номер . строки, а вторая - номер столбца аакопителя 5. При постуил - НИИ иа вход дешифратора 2 первой группы разрядов на управляющий в,ход элемента И 4, вьясоа которого подключен к требуемой строке накопителя 5, подается разрешающий сигнал. Вторая rpjrnm разрядов кода адреса посгуаа&е на второго дешифратора 3, разре шающий сигнал при этом подается на вход элемента И 11, соответствующего требуемому столбцу накопителя 5, После занесе ния во входной регистр 1 очереэного кода адреса на вход 8 подается Сигнал Запись, который поступает на вход ключа записи в и на вторые входы всех элементов И 1.1, При. этом на выходе ключа записи 6 формируется импульс напряжения для записи информации. Импульс записи поступает на вторые входы всех элементов И 4, но на соответствующую строку накопителя 5 через элемент И 4 импульс записи

поступает только в том случае, если на первом входе элемента И 4 имеется разрешающий сигнал от дешифратора 2, Совпадение служебного сигнала .Запись с разрэгшающим сигналомот дешифратора 3 на входе одного из элементов И 11 приводит к передаче с его выхода через соответствующий элемент ИЛИ 12 разрешающего сигнала на вход соответствующего вьгходного ключа 13, Этот ключ открьгеается, и для запоминающего элемента, включенного между соот ветствуюшим столбцом и выбранной строкой, электричесгсая цепь записи оказывается замкнутой. Все другие вьгходные ключи 13 остются закрытыми, из-за чего для остальных за минающих элементов выбранной строки накопителя 5 электрическая цепь записи оказьтвается разомкнутой.

Таким образом, в теч:ение импульса записи в заданное состояние первйлючается только один запоминающий элемент, адрес которого занесен во входной регистр 1.

После окончания импульса записи бывшие открьггыми элементы 4, 11, 12 и ключ 13 закрьшаются, и устройство оказывается готовым к приему очередного кода адреса и записи следующего бита информации либо к переходу в другой режим работы. В отличие от режима запяси в остальных двух режимах стирание и считывание производятся не отдельиь1ми бйтамй, а целыми словами разрядность которых определяется количеством столбцов накопителя, вьшолнаюших в данном случае огнкции разрядных шин (а строки-функаии числовых шин). Для этого во входной регистр 1 заносится код адреса стираемого (или считьюаемого) слова, определяющий номер строки (числовой шины) накопителя S, в которую $то слово записано Код адреса заносится В первую группу разрядов регистра 1 и, поступая с них на дешифратор 2, приводит к появлению разрешающего сигнала иа первом (управляющем) входе соотве1х:твуюшего элемента И 4, Вторая группа разрядов регистра 1 в режиме стирания и считывания остается незадействованной, а дешифратор 3 заблокирован элементами И 11, открываемыми только в режиме записи. После подали кода адреса в регистр 1 на вхоя 9 подается служебный сигнал Стирание (а при считьтании - на вход 10 служебньгй сигнал

Считывание), Этот сигнал, поступая на вторые входы элементов ИЛИ 12, приводит к появлению разрешающих сигналов на первых (управляющих) входах всех выходных ключей . 13, благодаря чему все они открываются. Одновременно служебный сигнал Страние (Считывание) поступает на вход ключа стирания и считывания 7, в результате чего на вьгходе этого ключа формируется импульс напряжения (или тока), требуемого для стирания (сгштывания) информации. Этот импульс поступает на вторые входы всех элементов И 4, но пропускается на соответс вующую строку накопителя 5 только тем иэ них, на первый вход которого подан разрешающий сигнал от де11ги4 атора 2. Поскольку все выходные ключи 13 открьгты, цепь стирания (считывания) оказывается замкнутой одновременно для всех запоминающих элементов накопителя 5, подключенных к выбранной строке. Благодаря этому в режиме стирания все они переключаются в исходное состояние, В режиме считывания длительност (или амплитуда, или то и другое вместе) сл жебного сигнала Считывание выбирается гораздо меньше, чем у служебного сигнала Стирание. Соответственно меньше (по длительности и/или амплитуде) .также и импульс формируем ьШ на выходе ключа стирания и считывания 7 и поступающий на выбранную строку накопителя 5. Энергии этого импульс недостаточно для переключения запоминак ишх элементов накопителя в исходное состоя ние. Поэтому при считывании стирания за- писанной информации не происходит. Но величина тока, протекающего через каждый запоминающий элемент на второй вход соот:ветствующего выходного ключа 13, зависит от того, в каком состоянии этот запоминающий элемент находится, И в зависимости от этого на выходах 14 ключей 13 формируются сигналы считьюания нуля или единицы, ПосЛе окончания служебного сигнала Счить ние (Стирание) открытый элемент И 4, элементы ИЛИ 12 и вькодные ключи 13 за1фываются, и устройство оказывается гоTOBbiM к считыванию (стиранию) следующего слова либо к переходу в режим записи. Допустим, что- накопитель 5 представляет собой матрицу, образуемую двумя изолированными, но пересекающимися между собой системами проводящих шин (строк и столбпов), в каждое перекрестие которой включе;ны последовательно соединенные бистабильный переключатель 15 и диод 16, Бистабиль |ный переключатель представляет собой полуп водниковый элемент, способный под воздейст вием соответствующих электрических импульс изменять свое сопротивление на несколько порядков и надежно сохранять любое из двух состояний в течение длительного времени, в том числе и при отключенном питании. Такие бистабильные переключатели изготавливаются, например, из полупроводниковых материалов, в которых возможны многократные фазовые превращения иэ аморф ного состояния в кристаллическое и обратно, В исходном непроводящем состоянии такой бистабильный переключатель имеет большое сопротивление (порядка 1-10 МОм), При воздействии импульса напряжения с ампли-г тудой больше определенной кристаллической величины (обычно 15-25 В) в нем происхоант электрический пробой с формированием кристаллического проводящего канала, в результате чего бистабильный переключатель переходит в проводящее состояние с сопротивлением порядка 1 кОм, в котором может стабильно оставаться неопределенное время, Этот процесс и называется в данном елу чае Запись информации. Для перевода бистабильного переключателя обратно в непровоящее состояние (Стирание информашш), через него необходимо пропустпнть импульс тока большой величины (обычно 1О-1ОО мА), достаточной для расплавления кристаллического проводящего канала, материал которого в результате бьгстрого остывания опять Возвращается в непроводящее аморфное состояние. При использовании такого накопителя ключ записи 6 может быть вьтолнен, например, на орнове одного м -р- ,п -транзистора (на чертеже не . показан), , база которого подключена ко входу 8, а коллектор - к источнику напряжения записи (20-ЗО В), и подсоединенного к его эмиттеру резистора, необходимого для ограничения тока, после переключения бистабильного переключателя в проводящее состояние. Второй конец этого резистора и будет выходсэм ключа записи 6. Для реализации ключа стирания и считывания 7 необходим, . например, более мощный W -р- и транзистор, коллектор которого подключается к источнику напряжения стирания и считывания, эмнт тер - к выходу ключа записи 6, а база - к выходу элемента ИЛИ 17, выполненного на диодной сборке. Элементы 4 могут, например, представлять собой аналогичные И -рYl -транзисторы, базы которых подключены к соответствующим выходам дешифратора 2, эмиттеры - к соответствующим строкам накопителя 5, а все коллекторы - к общему выходу ключей 6 и 7. Выходные ключи 13 могут быть выполнены также на основе j-f р fj -транзисторов по схеме эмиттерного повторителя, в котором коллектор поцкгиочен к соответствующему столбцу накопителя ;5, база - к выходу соответствующего элемента ИЛИ 12, а общая точка эмиттера и нагрузочного резистора - к выходу 14, Считывание в этом случае должно произвоциться короткими импульсами (порядка О,1-1,О мк/с) с длительность, намного меньшей, чем требуется для стирания информации (обычно 1-10 м/с). При построении ППЗУ потвнп(ального типа, где возможна большая или-

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для преобразования телеграфного кода в видеокод | 1985 |

|

SU1314461A1 |

| Полупостоянное запоминающее устройство | 1976 |

|

SU690562A1 |

| Устройство для централизованного контроля и оперативного управления | 1977 |

|

SU633029A1 |

| Счетное устройство, сохраняющее информацию при отключении питания | 1987 |

|

SU1492476A1 |

| Устройство для графического отображения синтезируемой устной речи | 1986 |

|

SU1411802A1 |

| Запоминающее устройство | 1981 |

|

SU1010654A1 |

| Запоминающее устройство | 1977 |

|

SU720509A1 |

| Ассоциативное запоминающее устройство | 1990 |

|

SU1793475A1 |

| Ассоциативное запоминающее устройство с самоконтролем | 1980 |

|

SU858105A1 |

| МОЛЕКУЛЯРНО-ЭЛЕКТРОННОЕ ЗАПОМИНАЮЩЕЕ УСТРОЙСТВО | 1992 |

|

RU2068586C1 |

Авторы

Даты

1978-06-15—Публикация

1975-05-22—Подача