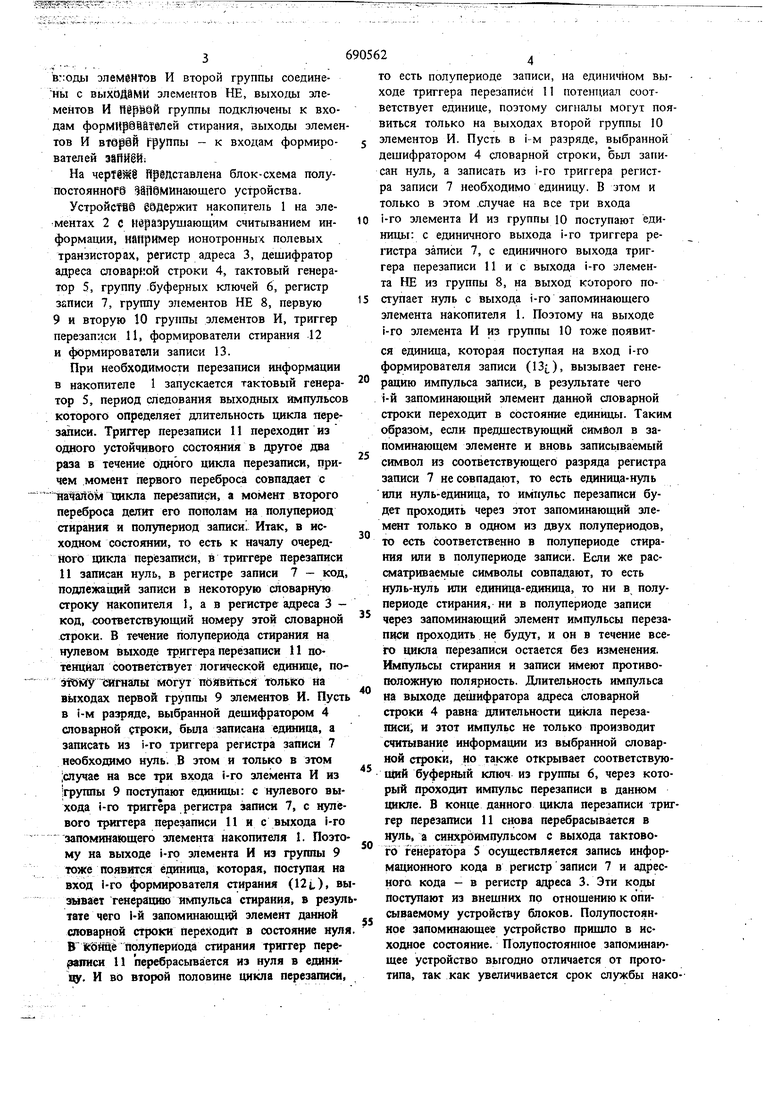

(54) ПОЛУПОСТОЯННОЕ ЗАПОМИНАЮЩЕЕ УСТГОЙСТВО в::оды элементов И второй группы соедине ны с выхОД§МИ элементов НЕ, выходы элементов И nipseft группы подключены к входам форМИрЙНТелей стирания, выходы элемен тов И втар§й рруппы - к входам формирователей 31ПйёЙ; На черТвй ё Приставлена блок-схема полупостоянноре заПбМИнающего устройства. Устройстеб ёЭДержит накопитель 1 на элементах 2 с иераэрушающим считыванием информации, например ионотронных полевых транзисторах, регистр адреса 3, дешифратор адреса словарной строки 4, тактовый генератор 5, группу .буферных ключей 6, регистр записи 7, группу элементов НЕ 8, первую 9 и вторую 10 группы элементов И, триггер перезаписи И, формирователи стирания 12 и формирователи записи 13. При необходимости перезаписи информации в накопителе 1 запускается тактовый генера тор 5, период следования выходных импульсо которого определяет длительность цикла перезаписи. Триггер перезаписи 11 переходит из одного устойчивого состояния в другое два раза в течение одного цикла перезаписи, причем момент первого переброса совпадает с 1йачаЯо никла перезаписи, а момент второго переброса деяит его пополам на полуяериод стирания и полупериод записи. Итак, в исходном состоянии, то есть к началу очередного цикла перезаписи, в триггере перезаписи И записан нуль, в регистре записи 7 - код, подлежащий записи в Некоторую словарную строку накопителя 1, а в регистре адреса 3 код, соответствующий номеру этой словарной строки. В течение полупериода стирания на нулевом выходе триггера перезаписи 11 потенциал соответствует логической единице, поэтб йу ййгналы могут появиться только иа вь1ходах первой группы 9 элементов И. Пусть в i-M разряде, выбранной дешифратором 4 словарной строки, была записана единица, а записать из i-ro триггера регистра записи 7 иеобходамо нуль. В этом и только в этом |случае на все три входа i-ro элемента И из 1группы 9 поступают единицы: с нулевого выхода (-ГО триггера регистра записи 7, с иул гвого триггера перезаписи 11 и с выхода i-ro запоминающего элемента накопителя 1. Поэтому иа выходе i-ro элемента И из группы 9 тоже появится единица, которая, поступая иа вход I-го формирователя стирания (12t) вы 31ывает генерацию импульса стирания, в резуль тате чего i-й запоминающий элемент дашюй словарной строки переходит в состояние иуля В Шнцё полупериода стирания триггер пере алиси 11 пере6расыва ется из нуля в едини1ф. И во второй половине цикла перезаписи, то есть полупериоде записи, на единичном выходе триггера перезаписи 11 потенциал соответствует единице, поэтому сигналы могут появиться только на выходах второй группы 10 элементов И. Пусть в i-м разряде, выбранной дешифратором 4 словарной строки, был записан нуль, а записать из i-ro триггера регистра записи 7 необходимо единицу. В этом и только в этом .случае на все три входа i-ro элемента И из группы Ю поступают единицы: с единичного выхода i-ro триггера регистра записи 7, с единичного выхода триггера перезаписи 11 и с выхода I-го :5лемента НЕ из группы 8, на выход которого поступает нуль с выхода i-ro запоминающего элемента накопителя 1. Поэтому на выходе 1-го элемента И из группы 10 тоже появится единица, которая поступая на вход i-ro формирователя записи (13;,), вызывает генерацию импульса записи, в результате чего t-й запоминающий элемент данной словарной строки переходит в состояние единицы. Таким образом, если предшествующий символ в запоминающем элементе и вновь записываемый символ из соответствующего разряда регистра записи 7 не совпадают, то есть единица-нуль или нуль-единица, то импульс перезаписи будет проходить через этот запоминающий злемент только в одном из двух полупериодов, то есть соответственно в полупериоде стирания или в полупериоде записи. Если же рассматриваемые символы совпадают, то есть нуль-нуль или единица-единица, то ни в полупериоде стирания, ни в полупериоде записи через запоминающий элемент импульсы перезаписи проходить не будзгг, и он в течение всего цикла перезаписи остается без изменения. Импупьсы стирания и записи имеют противоположную полярность. Длительность импульса иа выходе дешифратора адреса словарной строки 4 равна длительности цикла перезаписи, и этот импульс не только производит считывание информации из выбранной словарной , но также открывает соответствуюuwfi буферный ключ из группы 6, через который проходит импульс перезаписи в данном цикле. В конце данного цикла перезаписи триггер перезаписи 11 снова перебрасывается в иуль, а синхроимпульсом с выхода тактового генератора 5 осуществляется запись инф|0рмациоиного кода в регистр записи 7 и адресного кода - в регистр адреса 3. Эти коды поступают из внешних по отношению к описываемому устройству блоков. Полупостоянное запоминающее устройство пришло в исходное состояние. Полупостоянное запоминающее устройство выгодно отличается от прототипа, так как увеличивается срок службы нако|Пителя и исключается выход из строя его запоминающих злементов, что повышает надежность устройства. За счет построчной перезаписи и считывания информации повышается быстродействие устройства. Формула изобретения Полупостоянное запоминаюшее устройство, содержащее накопитель, выходные щины которого подключены ко входам элементов НЕ, регистр записи и регистр адреса, синхронизирующие входы которого подключены к выходу тактового генератора, триггер перезаписи и формирователи стирания и записи, выходы которых связаны с входными шинами накопителя, отличающееся тем, что, с целью повышения надежности и быстро действия устройства, в него введены две груп ьц пы элементов И, причем первые входы элементов И первой группы связаны с выходными шинами накопителя, вторые вхоЩ) элементов И первой группы связаны с нулевым выходом триггера перезаписи, третьи входы элементов И первой группы связаны с нулевыми выходами регистра записи, единичные выходы которого соединены с первыми входами элементов И второй группы, вторые входы которых соединены с единичным выходом триггера перезаписи, третьи входы элементов И второй группы соединень с выходами элементов НЕ, выходы злемеитов И первой группы подключены к входам формирователей стирания, выходы элементов И второй группы - к входам формирователей записи. Источники информйшо, принятые во внимание при экспертизе 1. Электроника, 1975, т. 48, N 17, с. 80. 2.Патент США N 3886532, кл. 340-173R. ЕТП

| название | год | авторы | номер документа |

|---|---|---|---|

| Полупостоянное запоминающее устройство | 1975 |

|

SU611251A1 |

| Запоминающее устройство | 1987 |

|

SU1495849A1 |

| Пульт учащегося для устройства обучения языкам | 1985 |

|

SU1354235A1 |

| Полупостоянное запоминающее устройство | 1978 |

|

SU752467A1 |

| Постоянное запоминающее устройство | 1980 |

|

SU1080214A1 |

| Запоминающее устройство с коррекцией программы | 1986 |

|

SU1347097A1 |

| Формирователь записи-считывания для запоминающих устройств | 1978 |

|

SU765873A1 |

| МНОГОКАНАЛЬНАЯ СИСТЕМА ДЛЯ РЕГИСТРАЦИИ ФИЗИЧЕСКИХ ВЕЛИЧИН | 1991 |

|

RU2037190C1 |

| Формирователь записи-считывания для запоминающих устройств | 1982 |

|

SU1035639A1 |

| Полупостоянное запоминающее устройство с электрической перезаписью информации | 1976 |

|

SU634373A1 |

GZ1

{Ь

Авторы

Даты

1979-10-05—Публикация

1976-01-26—Подача