1

Изобретение относится к области вычислительной техники и может быть использовано в качестве постоянного запоминающего устройства с электрической перезаписью.

Известно запоминающее устройство, выполненное на основе МДП-транзисторов с изменяемым порогом включения 1.

Наиболее близким по своей технической сущности к предлагаемому является запоминающее устройство, содержащее матричный накопитель, числовые щины которого подключены к выходам формирователей сигналов, первые входы формирователей сигналов соединены с выходами дешифратора строк, а вторые входы - с одним из выходов дешифратора столбцов, другие входы которого соединены с первыми входами первых ключей, вторые входы первых ключей соединены с первыми разрядными щинами матричного накопителя, выходы первых ключей соединены с выходом устройства, щину записи-считывания, соединенную через вторые ключи со вторыми разрядными шинами, и информационные шины, соединенные с дешифраторами строк и столбцов 2.

Недостатком указанных запоминающих устройств является низкая надежность работы из-за ложной записи сигнала в матрице накопителя запоминающего устройства под влиянием паразитных транзисторов, образующихся между соседними разрядными шинами. В режиме записи при недостаточно большой величине порогового напряжения включения паразитных транзисторов их сопротивление становится равно или даже меньше сопротивления нагрузочных МДПтранзисторов, что ведет к значительному уменьщению напряжения смещения на разрядных шинах и, как следствие, к ложной записи сигнала.

Влияние паразитных транзисторов может быть устранено за счет увеличения их порогового напряжения включения с помощью технологических методов, но это требует проведения дополнительных технологических операций, что усложняет технологический процесс изготовления микросхем.

Целью настоящего изобретения является повышение надежности запоминающего устройства за счет устранения ложной записи сигнала.

Поставленная цель достигается тем, что в устройство введены сумматор, инвертор и элементы И-НЕ, выходы которых подключены ко вторым разрядным шинам матричного накопителя, одни из входов элементов И-НЕ соединены с шиной зaпиcи-cчитывaния другие входы четных элементов И-НЕ с(эединены с выходом инвертора, а другие входы нечетных-элементов И-НЕ - со входом инвертора и с выходом сумматора, входы которого соединены с информационными шинами,

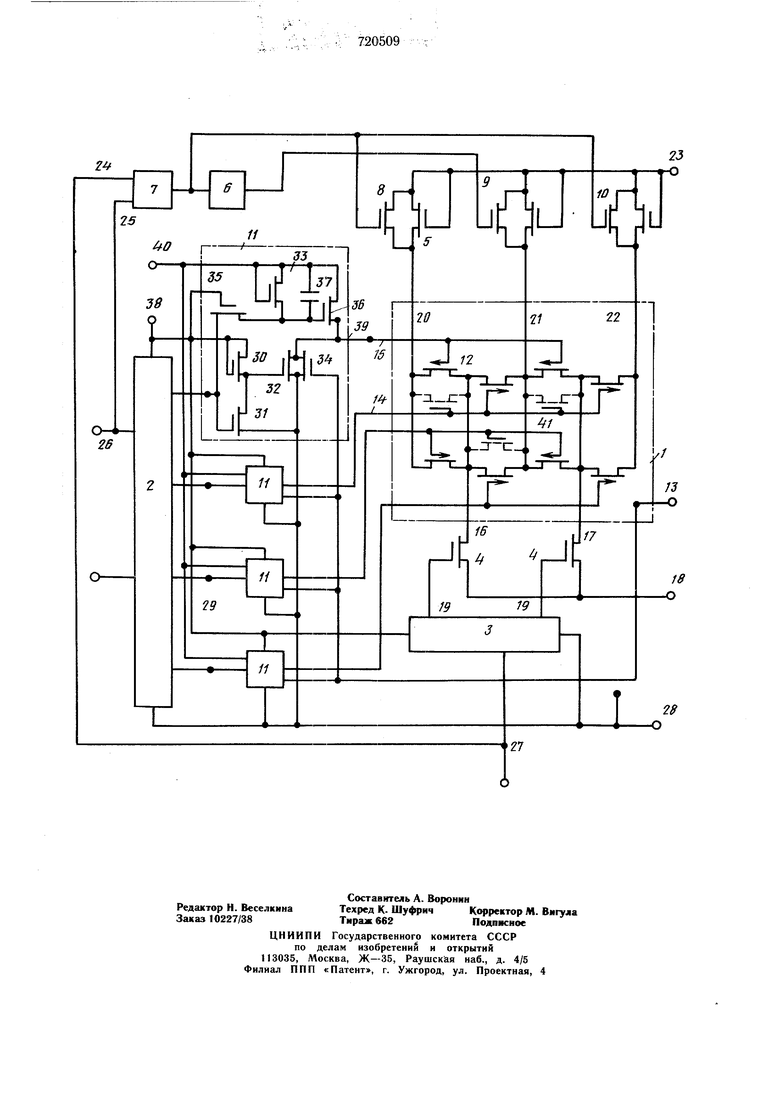

На чертеже представлена функциональная схема запоминающего устройства.

Запоминающее устройство содержит матричный накопитель 1, дешифратор строк 2, дешифратор столбцов 3, первые ключи 4, вторые ключи 5, инвертор 6, сумматор 7, элементы И-НЕ 8, 9, 10 на транзисторахключах, формирователи сигналов 11. Накопитель 1 содержит МДП-транзисторы 12 с изменяемым порогом включения и выполнен на изолированной от остальной части кристалла подложке, имеющей шину 13. Транзисторы 12 в каждой строке матричного накопителя 1 включены последовательно, при этом затворы четных транзисторов объединены числовыми шинами 14, нечетных - числовыми шинами 15, которые подключены к выходам формирователей 11.

В каждом столбце матричного накопителя 1 истоки транзисторов 12 объединены разрядными шинами 16 и 17, которые через ключи 4, выполненные на транзисторах, подключены к выходной шине 18. Затворы первых ключей 4 подключены к соответствующим выходам 19 дешифратора столбцов 3. Стоки транзисторов 12 в столбцах матричного накопителя 1 объединены разрядными шинами 20, 21 и 22, подключенными к шине 23 запись-считывание через вторые ключи 5, выполненные на транзисторах, затворы которых соединены со стоками. Параллельно ключам 5 включены элементы И-НЕ 8, 9, 10, выполненные на транзисторах. Затворы транзисторов-ключей элементов И-НЕ 8 и 10 подключены непосредственно к выходу сумматора 7, а затвор транзистора-ключа элемента И-НЕ 9 - через инвертор 6.

Входы 24 и 25 су.мматора 7 через информационные шины соединены со входом 26 младшего разряда дешифратора строк 2 и входом 27 младшего разряда дешифратора столбцов 3 соответственно. Дешифраторы 2, 3 и формирователи 11 подключены к шине 28 нулевого потенциала. Вход каждого формирователя 11 подключен к одному из выходов 29 дешифратора строк 2. Формирователь И содержит транзисторы 30, 31, 32, 33, 34, 35, 36 и конденсатор 37, шину питания 38 и выход 39.

Запоминающее устройство работает следующим образом.

Запись информации производится за два цикла. В первом цикле все транзисторы 12 с изменяемым порогом включения переводятся в одно состояние (стирание), во втором производится избирательный перевод в другое состояние (запись). Стирание осуществляется подачей управляющего импульса Uy на шину 13 матричного накопителя 1. При этом все числовые щины 14, 15 и все остальные выводы подключены к шине нулевого потенциала 28.

В режиме записи шина запись-считывание 23 подключена к источнику напряжения ЕП,., причем fUyrr-Е и.( 1ипрр1,..где - пороговое напряжение управления (при |и у lUtiqf.i,,транзистор с изменяемым порогом включения состояния не изменяет). Выходная шина 18 и шина 13 подключены к шине нулевого потенциала 28. Шина 38 подключена к источнику напряжения питания. На шину 40 подается управляющий импульс напряжения Uy. Заданный код на входе дешифратора строк 2 обеспечивает прохождение на одну из числовых щин, например, шину 14, управляющего импульса Uy и подключение остальных числовых щин к шине нулевого потенциала 28. Конденсатор 37 способствует полной передаче напряжения Uy через транзистор 36 формирователя 11. Заданный код на входе дещифратора столбцов 3 обеспечивает подключение одной из разрядных шин 16 и 17, например, шины 16, через ключи 4 к выходной шине 18.

Кроме того., при заданном коде на входах дешифраторов 2 и 3 сумматор 7 и инвертор 6 обеспечивают открывание транзисторовключей только четных или только нечетных элементов И-НЕ 8, 9 и 10, например, транзисторы-ключи элементов И-НЕ 8 и 10 открыты, а транзистор-ключ элемента И-НЕ 9 закрыт. Тогда на сток выбранного транзистора 12 накопителя 1 с изменяемым порогом включения, подключенный например, к щине 21, напряжение Е подается через транзистор ключа 5 и канал транзистора 12 находится под нулевым потенциалом. На шину 22 напряжение литания ЕП подается через открытый транзистор-ключ элемента И-НЕ 10. Так как сопротивление транзнстора-ключа элемента И-НЕ 10 существенно меньше, чем сопротивление паразитного транзистора 41 накопителя 1, то утечка через паразитный транзистор 41 не приводит к уменьшению напряжения на шине 22.

Поэтому напряжение на подзатворном диэлектрике только у выбранного транзистора 12 накопителя 1 с изменяемым порогом включения равно напряжению Uy,,.4TO приводит к изменению состояния этого транзистора.

При считывании шина 23 запись-считывание подключена к источнику напряжения ЕСШина 13 подложки матричного накопителя 1 подключена к шине нулевого потенциала 28. На шину 40 подается напряжение UCHRT, тахое, чтобы .4Hr.oi, где Uoo О, Uo 1 О - пороговые напряжения включения транзисторов с изменяемым порогом в состояинях логического нуля и логической единицы соответственно. Дешифратор строк 2 обеспечивает подключение не выбранных числовых шин к шине нулевого потенциала 28, а выбранных - к шине 40. Дешифратор столбцов 3 обеспечивает подключение выбранной разрядной шины к выходной шине 18, в которой контролируется ток, проходяший через выбранный транзистор 12 накопителя 1. Наличие тока свидетельствует о том, что транзистор с изменяемым порогом включения находится в состоянии логической единицы, отсутствие - логического нуля,

Введение новых элементов - сумматора 7, инвертора 6 и элементов И-НЕ 8, 9, 10 выгодно отличает предлагаемое запоминающее устройство от известных, так как устраняется ложная запись, обусловленная влиянием паразитных транзисторов, что повышает надежность работы устройства. В отличие от известных технологических способов устранения паразитных транзисторов предложенное решение увеличивает процент выхода годных микросхем и уменьшает их стоимость, так как уменьшается необходимое число технологических операций.

Формула изобретения Запоминающее устройство, содержащее матричный накопитель, числовые шины которого подключены к выходам формирователей сигналов, первые входы формирователей сигналов соединены с выходами дешифратора строк, а вторые входы - с одним из выходов дешифратора столбцов, другие выходы которого соединены с первыми входами первых ключей, вторые входы первых ключей соединены с первыми разрядными шинами

матричного накопителя, выходы первых ключей соединены с выходом устройства, шину записи-считывания, соединенную через вторые ключи со вторыми разрядными шинами, и информационные шины, соединенные с

дешифраторами строк и столбцов, отличающееся тем, что, с целью повышения надежности устройства за счет устранения ложной записи сигнала, в устройство введены сумматор, инвертор и элементы И-НЕ, выходы которых подключены ко вторым разрядным шинам матричного накопителя, одни из входов элементов И-НЕ соединены с шиной записи-считывания, другие входы четных элементов И-НЕ соединены с выходом инвертора, а другие входы нечетных элементов

И-НЕ - со входом инвертора и с выходом сумматора, входы которого соединены с информационными шинами.

Источники информации, принятые во внимание при экспертизе

1.Авторское свидетельство СССР № 479155, кл. G И С 11/40, 1975.

2.Патент США № 3618051, кл. 340-173, опублик. 1972 (прототип).

| название | год | авторы | номер документа |

|---|---|---|---|

| Постоянное запоминающее устройство | 1979 |

|

SU841047A1 |

| Запоминающее устройство | 1975 |

|

SU598118A1 |

| Постоянное запоминающее устройство | 1986 |

|

SU1388950A1 |

| Запоминающее устройство | 1985 |

|

SU1269209A1 |

| Запоминающее устройство с произвольной выборкой | 1977 |

|

SU769626A1 |

| Программируемое постоянное за-пОМиНАющЕЕ уСТРОйСТВО | 1978 |

|

SU809378A1 |

| Оперативное запоминающее устройство | 1986 |

|

SU1483493A1 |

| Запоминающее устройство | 1975 |

|

SU602995A1 |

| Запоминающее устройство (его варианты) | 1983 |

|

SU1098035A1 |

| Полупроводниковое запоминающее устройство | 1988 |

|

SU1674261A1 |

Авторы

Даты

1980-03-05—Публикация

1977-07-04—Подача