Целью изобретения является повышение быстродействия при изменениях в широком диапазоне уровня измеряемой величины.

Поставленная цель достигается тем, что в предложенное устройство введены регистр признака предела, выход которого подсоединен ко второму входу регистра результатов измерений, элементы задержки и связи, триггер блокировки сравнения, триггер переключения формирования, формирователь образцового постоянного сигнала, два коммутатора и дополнительные каналы измерения, включаюш,ие триггеры разблокировки, блоки сравнения, элементы И-НЕ, кроме канала измерения с младшим пределом, триггеры блокировки, кроме канала измерения со старшим пределом,элементы ИЛИ, кроме каналов измерения с младшим и старшим пределами, и ключи. Выход элемента ИЛИ подключен к первому входу ключа соответствуюпдего канала измерения, а входы - к выходу триггера блокировки и выходу элемента И-НЕ. Первый вход каждого блока сравнения соединен с соответствуюшим выходом делителя измеряемой величины, вторые входы объединены и через первый коммутатор подключены ко второму выходу фор.мирователя образцового сигнала уравновешивания, а через второй коммутатор к выходу формирователя образцового постоянного сигнала. Управляюшие входы коммутаторов соединены соответственно с первым и вторым выходами триггера переключения формирователей, первый вход которого соединен с первым выходом блока управления, а второй вход через элемент задержки - со вторым выходом блока управления, подключенным к управляюшим входам упомянутых триггеров каналов измерения и к управляющим входам регистра признака предела и триггера блокировки сравнения. Входы регистра признака предела и элемента связи подключены соответственно к выходам ключей. Выход элемента связи подключен ко входу блока управления, первый выход которого соединен со входом триггера блокировки сравнения, выход которого подключен к первым входам элементов И-НЕ, вторые входы которых подключены к выходам триггеров разблокировки соответствующих каналов измерения, а вход каждого триггера разблокировки соединен с выходом ключа соответствующего канала измерения и входо.м триггера блокировки предыдущего канала измерения с младшим пределом. Выход триггера блокировки канала измерения с младшим пределом подключен к первому входу ключа. Выход элемента И-НЕ канала измерения со старшим пределом соединен с первым входом ключа, а второй вход каждого ключа - с выходом соответствующего блока сравнения.

Это позволяет повысить скорость измерений в широком диапазоне изменения измеряемой величины и автоматически выбрать предел измерения; исключить потери

измерительной информации, обусловленные временем п.ереключения-предела, так как выбор предела измерений в данном случае совмещен во времени с циклом самого измерения.

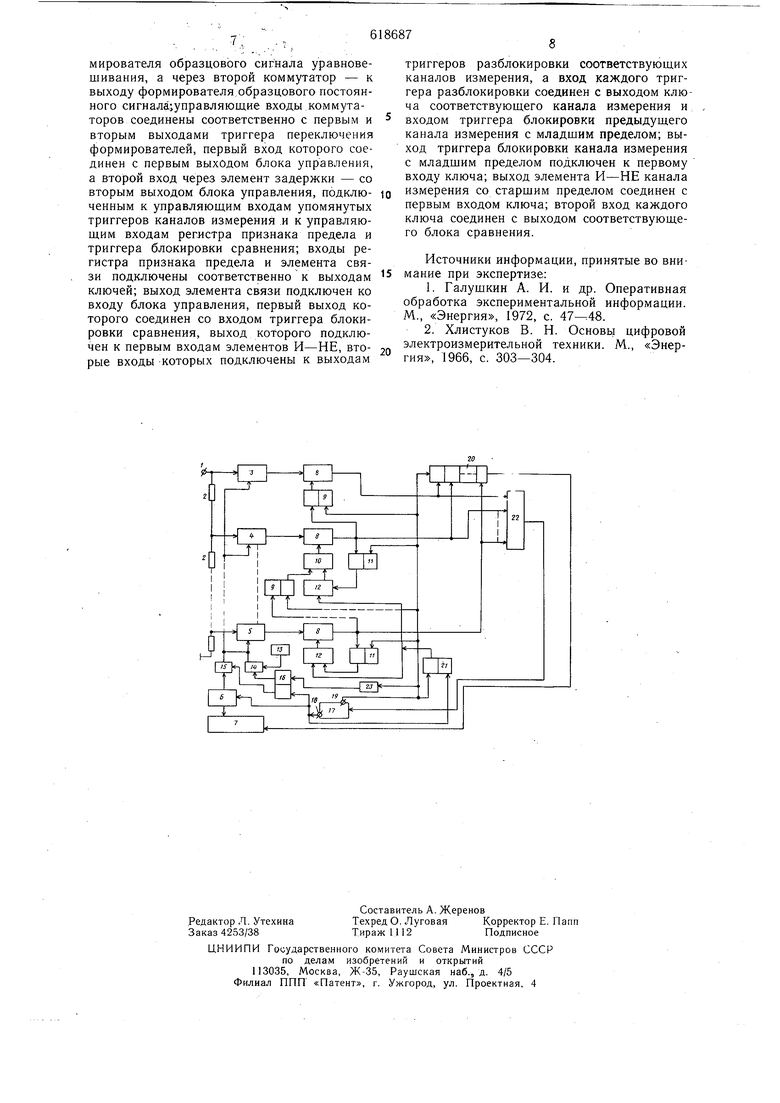

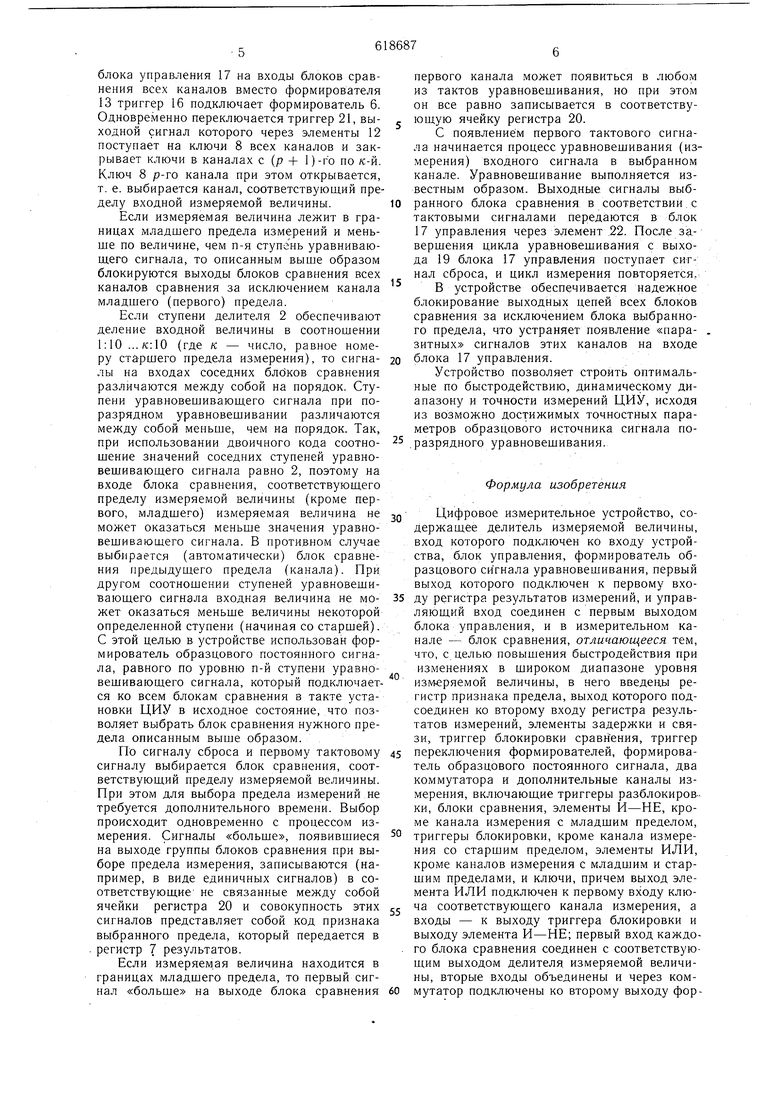

Функциональная схема устройства приведена на чертеже, где обозначены вход 1 измеряемой величины, делитель 2 измеряемой величины, блоки 3-5 сравнения первого (младшего), второго ... последнего (старшего) пределов измерения, формирователь 6 образцового сигнала уравновешивания, регистр 7 результатов измерений, клю.чи 8, триггер 9 блокировки, элемент ИЛИ 10, триггер 11 разблокировки; элементи-НЕ 12. формирователь 13 образцового постоянного сигнала, коммутаторы 14, 15, триггер 16 переключения формирователей, блок 17 управления с выходом 18 тактовых сигналов и выходом 19 сигналов сброса, регистр 20 признака предела, триггер 21 блокировки сравнения, элемент 22 связи и элемент 23 задержки.

Устройство работает следующим образом Измеряемая величина, поступающая на вход 1 через ступени делителя 2, передается одновременно на все блоки сравнения 3-5. Число ступеней делителя выбрано, исходя из требуемого количества пределов измерения, а величина ступени делителя - в соответствии с максимальным значением уравновешивающего сигнала, равного верхней границе младщего предела. Таким образом, измеряемый сигнал распределяется по блокам сравнения в соответствии со ступенями делителя, уменьшаясь в направлении блока сравнения наибольшего предела. По сигналу сброса блока 17 управления триггеры 9, 11 и 21 принимают исходное состояние, обеспечивающее открытое положение ключей 8 в выходных цепях всех блоков сравнения. Одновременно сбрасываются в нуль ячейки регистра 20. Затем с задержкой в элементе 23, достаточной для переключения указанных триггеров, сигнал сброса переводит триггер 16 в положение, при котором открывается коммутатор 14 и на входы всех блоков сравнения подается образцовый постоянный сигнал формирователя 13, равный по величине определенной ступени уравновещивающего сигнала. При этом на выходе каждого блока сравнения группы в случае, если измеряемый сигнал лежит в границах р-го предела и превышает по величине на входе блока сравнения р-го канала п-ю ступень уравновешивающего сигнала появляются единичные сигналы (сигналы «больше) сравнения. С одной стороны сигнал «больше переключает триггер I1 в цепи блока сравнения данного канала а с другой стороны этот сигнал переключает триггер 9 в цепи блока сравнения предыдущего канала. При этом выходы блоков сравнения этих каналов блокируются сигналами триггеров 9 и 11 через элементы 12, 10 и 8. С появлением первого тактового сигнала

блока управления 17 на входы блоков сравнения всех каналов вместо формирователя 13 триггер 16 подключает формирователь 6. Одновременно переключается триггер 21, выходной сигнал которого через элементы 12 поступает на ключи 8 всех каналов и закрывает ключи в каналах с (р + )-го по /с-й. Ключ 8 р-го канала при этом открывается, т. е. выбирается канал, соответствующий пределу входной измеряемой величины.

Если измеряемая величина лежит в границах младшего предела измерений и меньше по величине, чем п-я ступень уравниваюш,его сигнала, то описанным выше образом блокируются выходы блоков сравнения всех каналов сравнения за исключением канала младшего (первого) предела.

Если ступени делителя 2 обеспечивают деление входной величины в соотношении 1:10 ...к:10 (где к - число, равное номеру старшего предела измерения), то сигналы на входах соседних блбков сравнения различаются между собой на порядок. Ступени уравновешивающего сигнала при поразрядном уравновешивании различаются между собой меньше, чем на порядок. Так, при использовании двоичного кода соотношение значений соседних ступеней уравновешивающего сигнала равно 2, поэтому на входе блока сравнения, соответствующего пределу измеряемой величины (кроме первого, младщего) измеряемая величина не может оказаться меньще значения уравновешивающего сигнала. В противном случае выбирается (автоматически) блок сравнения предыдущего предела (канала). При другом соотношении ступеней уравновешивающего сигнала входная величина не может оказаться меньще величины некоторой определенной ступени (начиная со старшей). С этой целью в устройстве использован формирователь образцового постоянного сигнала, равного по уровню п-й ступени уравновешивающего сигнала, который подключается ко всем блокам сравнения в такте установки ЦИУ в исходное состояние, что позволяет выбрать блок сравнения нужного предела описанным выше образом.

По сигналу сброса и первому тактовому сигналу выбирается блок сравнения, соответствующий пределу измеряемой величины. При этом для выбора предела измерений не требуется дополнительного времени. Выбор происходит одновременно с процессом измерения. Сигналы «больще, появившиеся на выходе группы блоков сравнения при выборе предела измерения, записываются (например, в виде единичных сигналов) в соответствующие не связанные между собой ячейки регистра 20 и совокупность этих сигналов представляет собой код признака выбранного предела, который передается в регистр 7 результатов.

Если измеряем.ая величина находится в границах младщего предела, то первый сигнал «больше на выходе блока сравнения

первого канала может появиться в любом из тактов уравновешивания, но при этом он все равно записывается в соответствуюшую ячейку регистра 20.

С появлением первого тактового сигнала начинается процесс уравновешивания (измерения) входного сигнала в выбранном канале. Уравновешивание выполняется известным образом. Выходные сигналы выбранного блока сравнения в соответствии с тактовыми сигналами передаются в блок 17 управления через элемент .22. После за,вершения цикла уравновешивания с выхода 19 блока 17 управления поступает сигнал сброса, и цикл измерения повторяется;

В устройстве обеспечивается надежное блокирование выходных цепей всех блоков сравнения за исключением блока выбранного предела, что устраняет появление «паразитных сигналов этих каналов на входе блока 17 управления.

Устройство позволяет строить оптимальные по быстродействию, динамическому диапазону и точности измерений ЦИУ, исходя из возможно достижимых точностных параметров образцового источника сигнала по.разрядного уравновешивания.

Формула изобретения

Q Цифровое измерительное устройство, содержащее делитель измеряемой величины, вход которого подключен ко входу устрой. ства, блок управления, формирователь образцового сигнала уравновешивания, первый выход которого подключен к первому входу регистра результатов измерений, и управляющий вход соединен с первым выходом блока управления, и в измерительном канале - блок сравнения, отличающееся тем, что, с целью повышения быстродействия при изменениях в щироком диапазоне уровня измеряемой величины, в него введены регистр признака предела, выход которого подсоединен ко второму входу регистра результатов измерений, элементы задержки и связи, триггер блокировки сравнения, триггер

5 переключения формирователей, формирователь образцового постоянного сигнала, два коммутатора и дополнительные каналы измерения, включающие триггеры разблокировки, блоки сравнения, элементы И-НЕ, кроме канала измерения с младщим пределом,

0 триггеры блокировки, кроме канала измерения со старщим пределом, элементы ИЛИ, кроме каналов измерения с младшим и старшим пределами, и ключи, причем выход элемента ИЛИ подключен к первому входу ключа соответствующего канала измерения, а входы - к выходу триггера блокировки и выходу элемента И-НЕ; первый вход каждо. го блока сравнения соединен с соответствующим выходом делителя, измеряемой величины, вторые входы объединены и через коммутатор подключены ко второму выходу формирователя образцового сигнала уравновешивания, а через второй коммутатор - к выходу формирователя образцового постоянного сигнала;управляющие входы коммутаторов соединены соответственно с первым и вторым выходами триггера переключения формирователей, первый вход которого соединен с первым выходом блока управления, а второй вход через элемент задержки - со вторым выходом блока управления, подключенным к управляющим входам упомянутых триггеров каналов измерения и к управляющим входам регистра признака предела и триггера блокировки сравнения; входы регистра признака предела и элемента связи подключены соответственно к выходам ключей; выход элемента связи подключен ко входу блока управления, первый выход которого соединен со входом триггера блокировки сравнения, выход которого подключен к первым входам элементов И-НЕ, вторые входы -которых подключены к выходам

триггеров разблокировки соответствующих каналов измерения, а вход каждого триггера разблокировки соединен с выходом ключа соответствующего канала измерения и входом триггера блокировки предыдущего канала измерения с младшим пределом; выход триггера блокировки канала измерения с младщим пределом подключен к первому входу ключа; выход элемента И-НЕ канала измерения со старшим пределом соединен с первым входом ключа; второй вход каждого ключа соединен с выходом соответствующего блока сравнения.

Источники информации, принятые во внимание при экспертизе:

1.Галущкин А. И. и др. Оперативная обработка экспериментальной информации. М., «Энергия, 1972, с. .

2.Хлистуков В. Н. Основы цифровой электроизмерительной техники. М., «Энергия, 1966, с. 303-304.

Авторы

Даты

1978-08-05—Публикация

1976-07-07—Подача