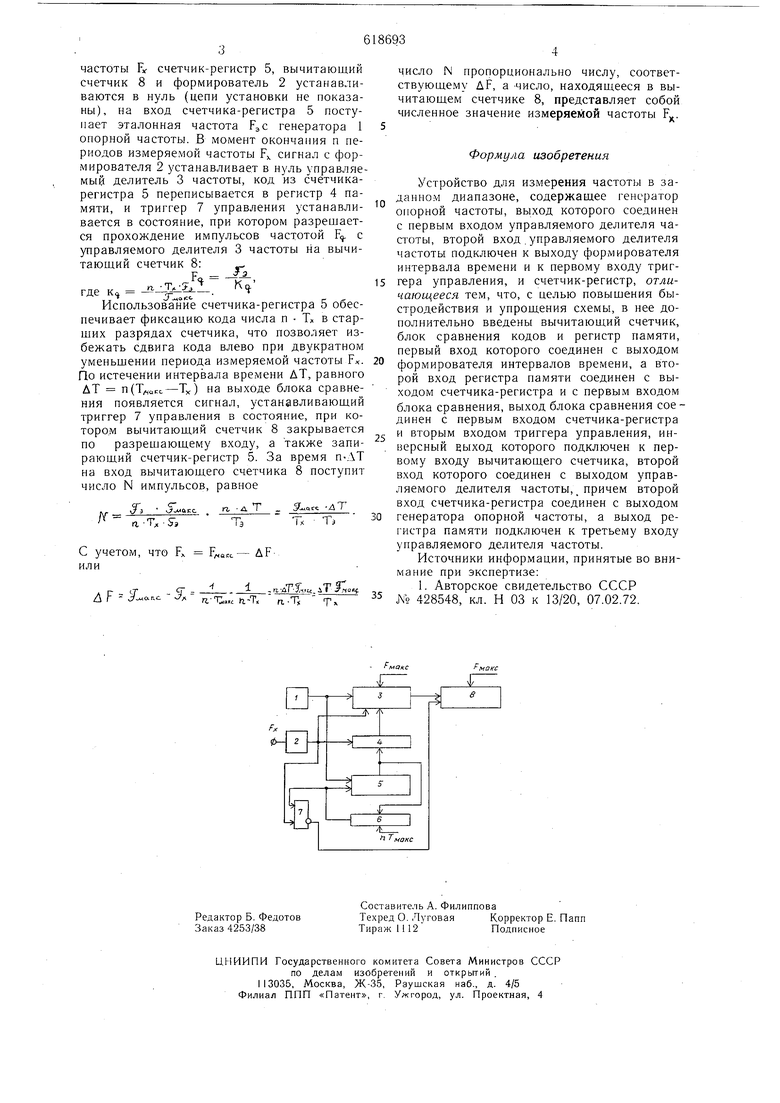

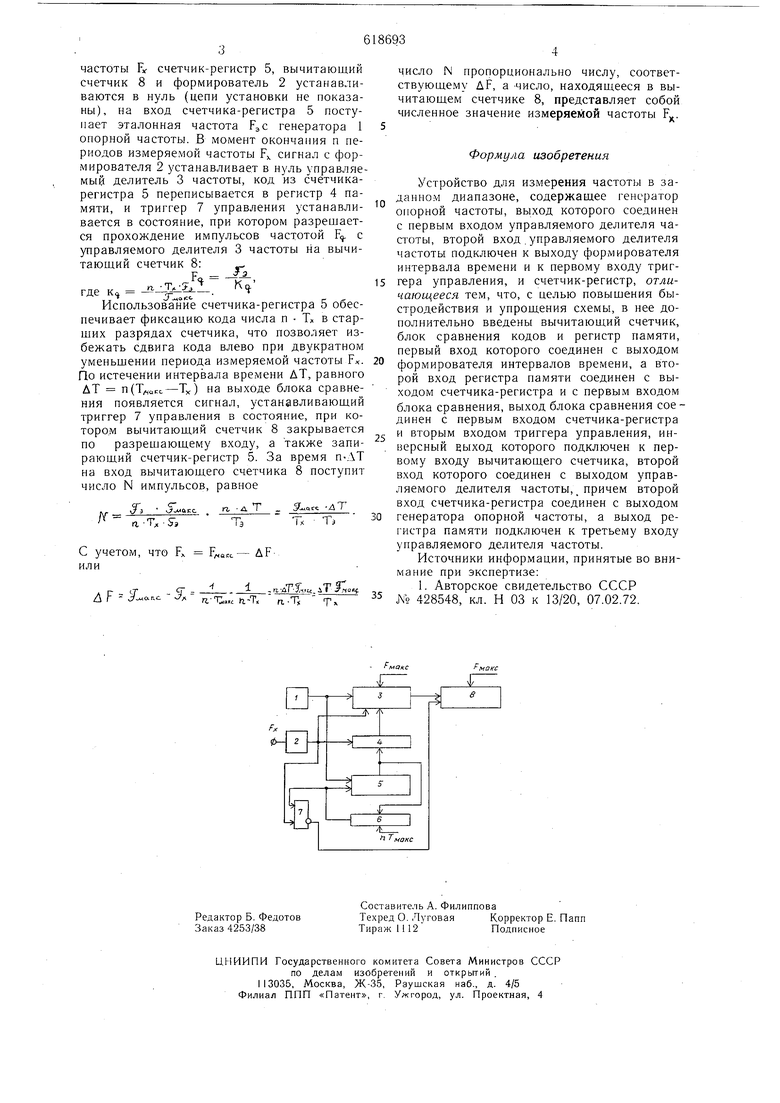

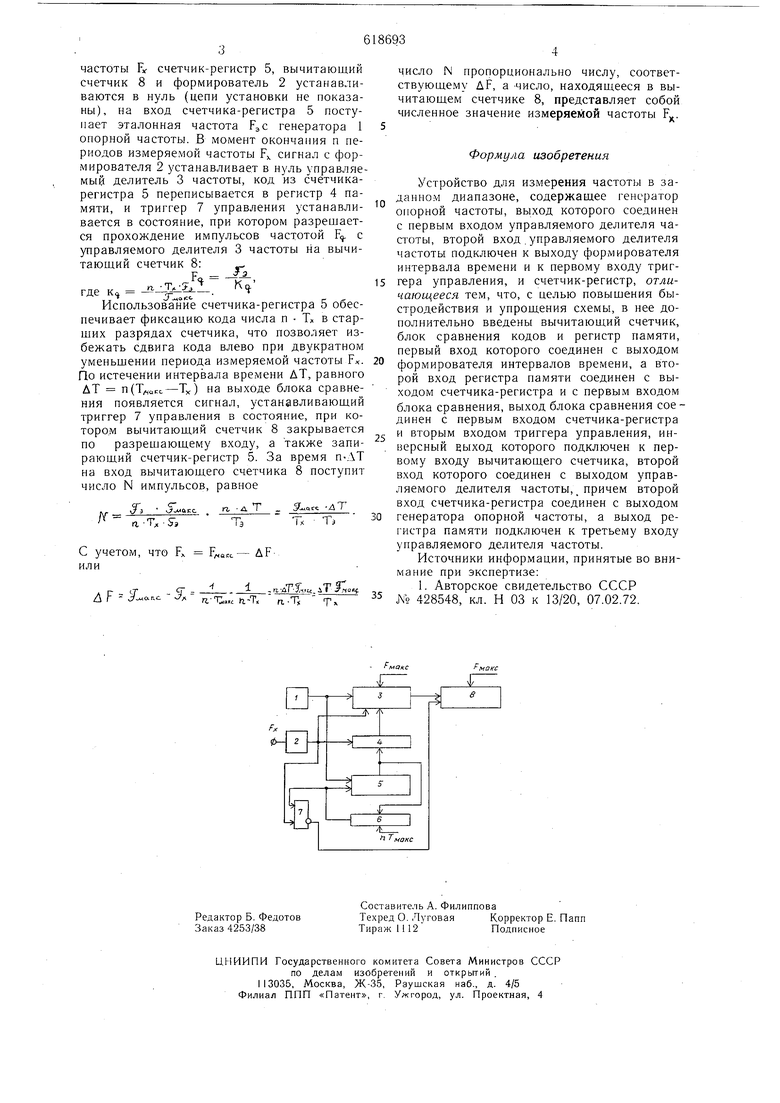

частоты FV счетчик-регистр 5, вычитающий счетчик 8 и формирователь 2 устанавливаются в нуль (цепи установки не показаны), на вход счетчика-регистра 5 поступает эталонная частота генератора 1 опорной частоты. В момент окончания п периодов измеряемой частоты F. сигнал с формирователя 2 устанавливает в нуль управляемый делитель 3 частоты, код из счетчикарегистра 5 переписывается в регистр 4 памяти, и триггер 7 управления устанавливается в состояние, при котором разрешается прохождение импульсов частотой F.,. с управляемого делителя 3 частоты на вычитающий счетчик 8: 3 1. К(} где к, Использование счетчика-регистра 5 обеспечивает фиксацию кода числа п Т), в старщих разрядах счетчика, что позволяет избежать сдвига кода влево при двукратном уменьшении периода измеряемой частоты F. По истечении интервала времени ДТ, равного ДТ п( TX ) на выходе блока сравнения появляется сигнал, устанавливающий триггер 7 управления в состояние, при котором вычитающий счетчик 8 закрывается по разрешающему входу, а также запирающий счетчик-регистр 5. За время п-АТ на вход вычитающего счетчика 8 поступит число N импульсов, равное т -Л Т лг - ri-V -S, С учетом, что Fx F acc-- ДF или т, n.-T,K ц-Т, а.Т, число N пропорционально числу, соответствующему AF, а -число, находящееся в вычитающем счетчике 8, представляет собой численное значение измеряемой частоты F. Формула изобретения Устройство для измерения частоты в заданном диапазоне, содержащее генератор опорной частоты, выход которого соединен с первым входом управляемого делителя частоты, второй вход.управляемого делителя частоты подключен к выходу формирователя интервала времени и к первому входу триггера управления, и счетчик-регистр, отличающееся тем, что, с целью повыщения быстродействия и упрощения схемы, в нее дополнительно введены вычитающий счетчик, блок сравнения кодов и регистр памяти, первый вход которого соединен с выходом формирователя интервалов времени, а втоp g од регистра памяти соединен с выходом счетчика-регистра и с первым входом блока сравнения, выход блока сравнения соед; первым входом счетчика-регистра , вторым входом триггера управления, инверсныи Еыход которого подключен к первому входу вычитающего счетчика, второй вход которого соединен с выходом управляемого делителя частоты, причем второй вход счетчика-регистра соединен с выходом генератора опорной частоты, а выход регистра памяти подключен к третьему входу управляемого делителя частоты. Источники информации, принятые во внимание при экспертизе: Авторское свидетельство СССР 428548, кл. Н 03 к 13/20, 07.02.72.

| название | год | авторы | номер документа |

|---|---|---|---|

| Цифровой кодирующий преобразователь частоты следования импульсов | 1980 |

|

SU919080A1 |

| Устройство для преобразования разности частотно-импульсных сигналов в код | 1976 |

|

SU750728A1 |

| Устройство для измерения частоты повторения импульсов | 1976 |

|

SU573766A1 |

| Цифровой умножитель частоты следования импульсов | 1982 |

|

SU1034146A1 |

| Преобразователь угловой скорости вала в код | 1983 |

|

SU1136312A1 |

| Цифровой кодирующий преобразователь частоты | 1980 |

|

SU938402A1 |

| Умножитель частоты следования импульсов | 1981 |

|

SU991614A2 |

| Устройство для измерения нелинейности пилообразного напряжения | 1990 |

|

SU1777101A1 |

| Датчик углового положения, скорости и ускорения вращения вала | 1982 |

|

SU1107055A2 |

| Устройство для измерения скорости вращения асинхронного электродвигателя | 1976 |

|

SU648909A1 |

Авторы

Даты

1978-08-05—Публикация

1975-11-10—Подача