(54) УМНОЖИТЕЛЬ ЧАСТОТЫ СЛЕДОВАНИЯ ИМПУЛЬСОВ

| название | год | авторы | номер документа |

|---|---|---|---|

| Умножитель частоты | 1979 |

|

SU907781A1 |

| Умножитель частоты | 1983 |

|

SU1135004A1 |

| Умножитель частоты | 1988 |

|

SU1608779A1 |

| Дискретный умножитель частоты | 1977 |

|

SU736099A1 |

| Дискретный умножитель частоты повторения импульсов | 1977 |

|

SU692065A1 |

| Умножитель частоты | 1979 |

|

SU807322A1 |

| Цифровой умножитель частоты | 1978 |

|

SU803100A1 |

| Корреляционный измеритель времени запаздывания | 1983 |

|

SU1160433A1 |

| Умножитель частоты следования периодических импульсов | 1980 |

|

SU980094A1 |

| Умножитель частоты следования импульсов | 1981 |

|

SU961150A1 |

1

Изобретение относится к автоматике и вычислительной технике, в частности к устройствами обработки информации, представленной в частотно-импульсной форме,

По основному авт. св. № 687602. известен умножитель частоты следования импульсов, содержащий блок управления, подютюченный входом к шине ввода умножаемой частоты и к первому входу триггера, первым выходом - к входу обнуления делителя частоты, соединенного счетным входом с выходом генератора опорной частоты, а выходом - со счетным входом первого счетчика, подключенного входом обнуления к второму выходу блока управления, выходом переполнения - к второму входу триггера, а выходами разрядов - к информационным входам первого регистра памяти, соединенного управляющим входом с третьим выходом блока управления, выходами - с установочными входами второго счетчика, подключенного счетным входом к выходу генератора опорной частоты, входом управления установкой кода - к выходу формирователя импульсов, а выходом - к входу

формирователя импульсов и к первок-гу входу первого элемента И, выход которого является зыходом у гложптеля частоты, второй вход соедш1ен с выходом триггера 1.

НедостаичОМ известного y ffloжитeля является поннжештя точность умножения из-за возмоетюй нскратности числа импульсов опорной частоты (определяемого периодом y ffioжaeмoй частоты) коэффициенту умноже.- . НИН, пр1теодящей к неучету возникающего

10 остатка деления и превь щению значения выходной частоты велшштл, определяемой коэффициентом умножения.

Целыо изобретения является повышение точности y ffloжeния.

15

Цель достигается тем, что в умножитель частоты следования импульсов дополнительно введены преобразователь код - напряжение, реверсивный счетчик, ключи, инвертор, второй элемент И. элемент И-НЕ, блок сравнения

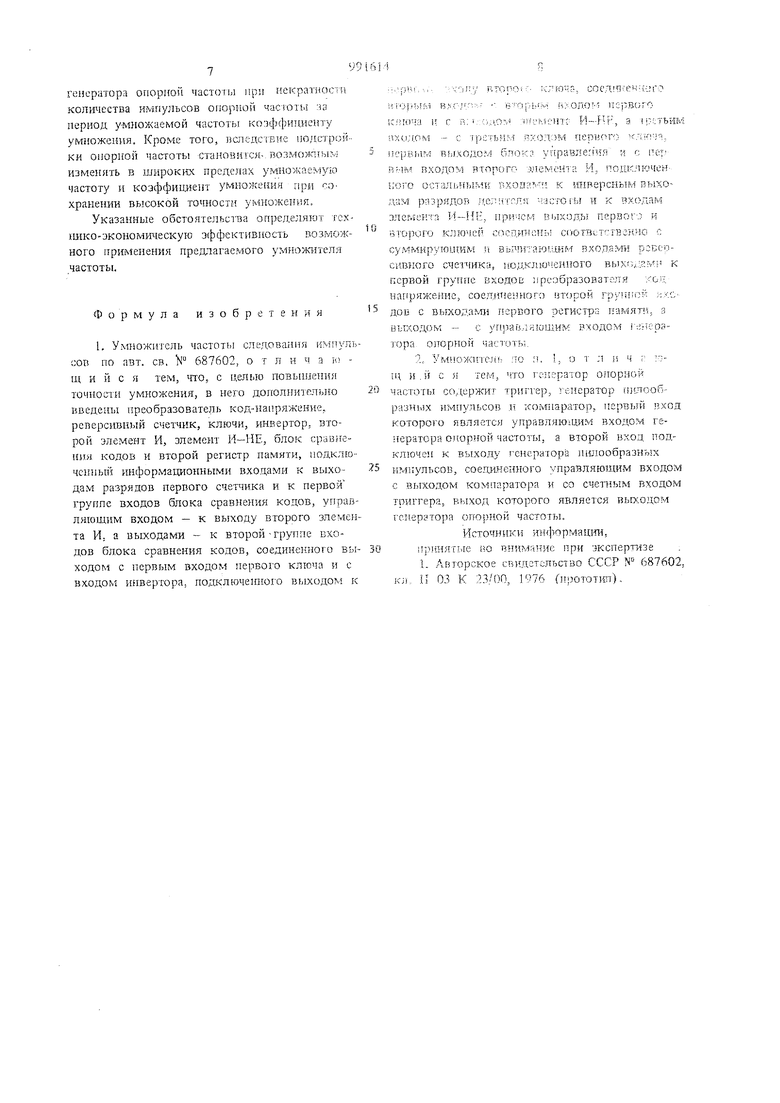

20 кодов и второй регистр памяти, подключенный 1шформадионными входами к выходам разрядов первого счетчика и к первой группе входов блока сравнения кодов, управляющим входом - к выходу второго элемента И, а выходами - к второй группе входов блока сравнения кодов, соединенного выходом с первым входом первого ключа и с входом инвертора, подключенного выходом к первому входу второго ключа, соединенного вторым входом с вторым входом первого ключа и с выходом элемента И-НЕ, а третьим входом - с третьим входом первого ключа, первым вы- ходом блока управления и с первым входом второго элемента И, подключенного остальными входами к инверсным выходам разрядов делителя частоты и к входам элемента И-НЕ, причем выходы первого и второго ключей соединены соответственно с суммирующим и вычитающим входами реверсивного счегшка подключенного выходами к первой группе входов преобразователя код -напряжение, соединенного второй группой входов с выходами первого регистра памяти, а выходом с управляющим входом генератора опорной частоты. При этом генератор опорной частоты содер жит триггер, генератор пилообразных импульсов и компаратор, первый вход которого яв,ляется управляю11р1М входом генератора опорной частоты, а второй вход подключен к выходу генератора пилообразных импульсов, соединенного управляющим входом с выходом компаратора и со счетным входом триггера, выход которого является выходом генератора опорной частоты. На чертеже изображена блок-схема умножителя частоты следования импульсов, содержит умножитель блок I управления, подключенный входом к шине ввода умножаемой частоты и к первому входу триггера 2, а пер вым выходом - к входу обнуления делителя 3 частоты. Делитель 3 соединен счетным входом с выходом генератора 4 опорной частоты, а выходом - со счетным входом первого счетчика 5. Счетчик 5 подключен входом обнуления к второму выходу блока 1 управления, выходом переполнения - к второму входу триггера 2, а выходами разрядов - к информационным входам первого регистра 6 памяти. Регистр 6 Соединен управляющим входом с третьим выходом блока 1 управления, а выходами - с установочными входами второго счетчика 7. Счетчик 7 подключен счетным входом к выходу генератора 4, входом управления установкой кода - к вьсюду формирователя 8 импульсов, а выходом - к входу формирователя 8 и к первому входу первого элемента И 9, выход которого является выходом умножителя частоты, а второй вход соединен с вьгходом триггера 2. Вт рой регистр 10 памяти подключен информационными входами к вьЕходам разрядов счет94 чика 5 к к первой группе входов блока II срави;.кия кодов, управляющим входом к вьосоду второго элемента И 12, а выходами - к второй группе входов блока П. Блок 11 соединен выходом с первым входом первого ключа 13 и с входом инвертора 14, подключенного выходом к первому входу второго ключа 15. Ключ 15 соединен вторым входом с вторым входом ключа 13 и с выходом элемента И-НЕ 16, а третьим входом с третьим входом ключа 13, первым выходом блока 1 управления и с первым входом элемента И 12. Элемент И 12 подключен остальными входами к инверсным выходам разрадов делителя 3 частоты и к входам элемента И-НЕ 16. Вьгходы ключей 13 и 15 соединены соответственно с суммирующим и вычитающим входами реверсивного счетчика 17, подключенного выходами к первой группе входов преобразователя 18 код-напряжение. Преобразователь 18 соединен второй группой входов с выходами регистра 6 памяти, а выходом - с управляющим входом генератора 4 опорной частоты. Генератор 4 может быть выполнен, например, содержащим триггер 19, генератор 20 пилообразных импульсов и компаратор 21, первый вход которого является управляющим входом генератора 4, а второй вход подключен к выходу генератора 20 пилообразных импульсов, соединенного утэравляющим входом с выходом компаратора 2 и со счетным входом триггера 19, выход которого является вьгходом генератора 4. Умножитель частоты работает следующим образом. В счетчике 5 за каждый период умножаемой частоты происходит накопление импульсов, поступающих с выхода делителя 3 частоты. По окончании периода умножаемой частоты в этом счетчике устанавливается число о-Т(ьх м- к где f - частота импульсов генератора 4 опорной частоты; Т, - период умножаемой частоты; К - коэффициент деления делителя 3 частоты (коэффициент умножения умножителя частоты). По окончании периода умножаемой частоты сигналом с блока 1 управления в регистр 6 памяти записывается число, находящееся в счетчике 5. Затем сигналом от блока 1 управления счетчик 5 устанавливается в нупевое состояние. Сигналом блока 1 управления в нулевое состояние устанавливается и делитель 3 частоты. После этого начинается процесс накопления импульсов счетчиком 5. Счетчик 7 работает в режиме вычитания. При каждом его обнулении с выхода его по дается импульс, который через открытый элемент И 9 поступает иа выход умножителя частоты. Этот же импульс через формировате 8 импульсов подается на вход управления установкой кода счетчика 7 числа, находящег ся в регистре 6 памяти. Период частоты на выходе умножителя частоты определяется выражением W oпериод частоты генератора 4 опорной частоты. Тогда частота на выходе умножителя частотына входе умножителя часТриггер 2 находится в единичном состоянии, при котором на вход элемента И 9 подается открывающий сигнал. Это состояние триггера подтверждается импульсами входной частоты. При прекращении поступления импул сов входаой частоты происходит полное заполнение счетчика 5 импульсов. Это заполнение происходит периодически через интервалы времени t К N О 5 емкость счетчика 5. где Каждый раз при заполнении счетчика 5 с его выхода подается импульс иа второй вход триггера 2. Триггер 2 обнуляется и элемент И 9 закрывается, что приводит к прекращению прохождения импульсов на выход умножителя частоты. В начальный момент работы умножителя регистр dO заполнен до половины и реверсивный счетчик 17 обнулен. В этом случае, когда число импульсов, поступающее с выхода генератора 4 на вход делителя 3 за период умножаемой частоты, не делится без остатка на коэффициент деления делителя , в делителе 3 в момеит окончания периода умножаемой частоты будет записан остаток от деления. Следовательно, инверсный код остатка, поступающий на элементы И 12 и И-НЕ 16, даст на выходе элемента И-НЕ 16 положительный потенциал, поступающий на вторые ключей 13 и 15. Кроме этого, на первом входе ключа 15 будет положительный потенциал, обусловленный наличием нулевого потетщала на выходе блока 11 сравнения из-за неравенства кодо« на выходах разрядов счетчика 5 и на выходах регистра 10. В результате этого импульс с первого выхода блока 1 управления, поступающий на пер;: вый вход элемента И 12 и третьи входы клю чей 13 и 15, проходит через ключ 15 на суммирующий вход счетчика 17. Это вызывает увеличение кода счетчика 17, а следовательно, и увеличение выходного напряжения преобразователя 18 код-напряжение. При этом масштаб увеличения выходного напряжения преобразователя 18 обратно пропорционален коду частотного, записанного в регистр 6 и поданного на вторую группу входов преобразователя 18. Это необходимо для устранения зависимости шага подстройки опорной частоты от изменения умножаемой частоты. Возросший уровень выходного напряжения преобразователя 18 вызывает увеличение порога срабатывания компаратора 21 генератора 4 н уменьшение частоты сбрасывающих импульсов генератора 20 пилообразных импульсов, а значит и уменьшение выходной частоты генератора 4 опорной частоты. Это в свою очередь вызовет уменьшение кода остатка в делителе 3 в момент окончания следующего периода умножаемой частоты и т. д. Умножитель частоты будет работать по данному алгоритму до тех пор, пока код остатка деления не станет равным нулю (т. е. число импульсов опорной частоты за период умножаемой частоты станет кратным коэффициенту умножения). В этом случае по приходу с первого вь1хода блока 1 управления импульса на первый вход элемента И 12, на выходе элемента Н 12 будет сформирован импульс (так как на остальные входы элемента И 12 поступает инверсный код нулевого остатка делителя 3). Этот импульс по уп- равляющему входу регистра 10 разрешает перезапись кода частного из счетчика 5 в регистр 10. В результате на выходе блока 11 сравнения возникает положительный потенциал, поступающий на первый вход ключа 13. Однако импульс с первого выхода блока 1 управления через ключ 13 на вычитающий вход счетчика 17 не проходит, так как в этот момент времени ключ 13 закрыт нулевым потенциалом, поступающим на его второй вход с выхода элемента И-НЕ 16. Следовательно, величина опорной частоты на выходе генератора 4 не изменяется. Если же в результате воздействия дестабилизирующих факторов опорная частота изменится и в делителе 3 будет ненулевое значенне кода остатка, то стабилизация частоты будет осуществляться аналогично. изложенному. В случае уменьшения опорной частоты код частного в счетчике 5 уменьшается, что вызовет несовпадение кодов на входах блока 11 сравнения и увеличение кода счетчика 17, что приведет к увеличению опорной частоты. Таким образом, предлагаемый умножитель частоты по сравнению с известным обладает более высокой точностью за счет перестройки генератора опорной частоты при иекратиостн количества импульсов опорной частоть :ta период умножаемой частоты коэффициенту умножения. Кроме того, вследстЕне подсчройки оиорпой частоты становился- возможгым изменять в широк гх пределах умножаггчаую частоту и коэффициент умножения при сохранении высокой точности умножения. Указанные обстоятельства оп эеделяют тсхШ1ко-эконом№1ескую э()фективность возможного применения предлатаемого умножителя частоты. Формула изобретен 1, Ум110Ж1ггель частоты следования импуль сов по авт. ев, К 687602, о т п и ч а ю щ и и с я тем, тао, с цел)Ю повьпиення точности умножения, в него дополнительно введены преобразователь код-напряжение. реверсивный счетчик, ключи, инвертор, второй элемент И, элемент И-НЕ, блок сравиенн.я кодов и второй регистр памяти, иодключеннглй информацион11ыми входами к выходам разрядов первого счетчика и к первой группе входов блока сравнения кодов, управ ляющим входом - к вь5ходу второго элемен та И. а выходами - к второй-группе входов бяока сравнения кодов, соединенного вь ходом с первым входом первого ключа и с входом инвертора, подключенного выходом к ,,,. visry BTOpoi:- . соел Т еч-{аго i iopbFi i в( Борьм гоодо - iiejiBoro ;с;:гоча И С п: олом iHihH-in: M--FU а ( iiXijjfOM - с третьим ЯлОЛзтй первого клкг-ч, Шрвым выходом бпок утгравлегп и с петR-1M входом ятпрото ;: лемента И, подключенкого остал1 нымк вxoaa - I к ш1Рерсным выходам разрядов гелитпля частоты и к входам элемента H-fiE, причем выходь; перпог-. и второго ключей соспитюны спотвит-гвгино с суммирующим и вьлпгаюи.щм входами РОБСЛсивного счетчика, иодкт 0чен1юго вь1хп,;.гмп к первой группе входов ;феобразоватоля лох наг ряжение, еоедтгепного Шорой группою дов с вь ходами гюрвого регистра памяти, з выходом -- с управляющим входом rejiC psтора опорной частить;, Л Умиожптель :то п. 1, о т л н ч г :-;1 ij Л1 с а тем, что генератор опорной частоты содержит триггер, ;чллератор гишсоиразных импульсов .и компаратор, первый вход которого является управляюлдим входом генератора опорной частоты, а второй вход подключен к выходу генератора пшюобразньгх 11мпульсов, соединенного vnpaBHHmiiuiM входом с выходом компаратора и со счетным входом триггера, вьлход которого является вьгходом гел.ерэтора огюри.ой частоты. Источ} И1си инф.ормацни, 1П Ш1ягые во внимание при экспертизе L Авторское свидетельство СССР № 687602, кл II 03 К 23/00, 1976 (прототют),

Авторы

Даты

1983-01-23—Публикация

1981-09-25—Подача