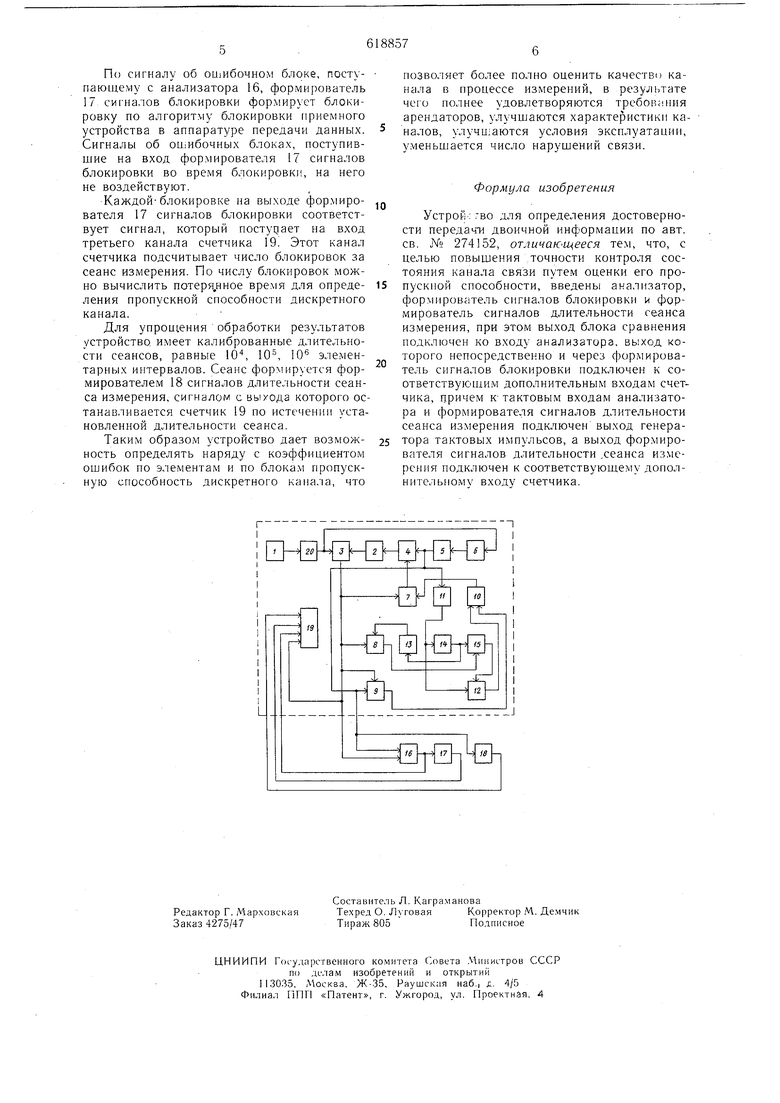

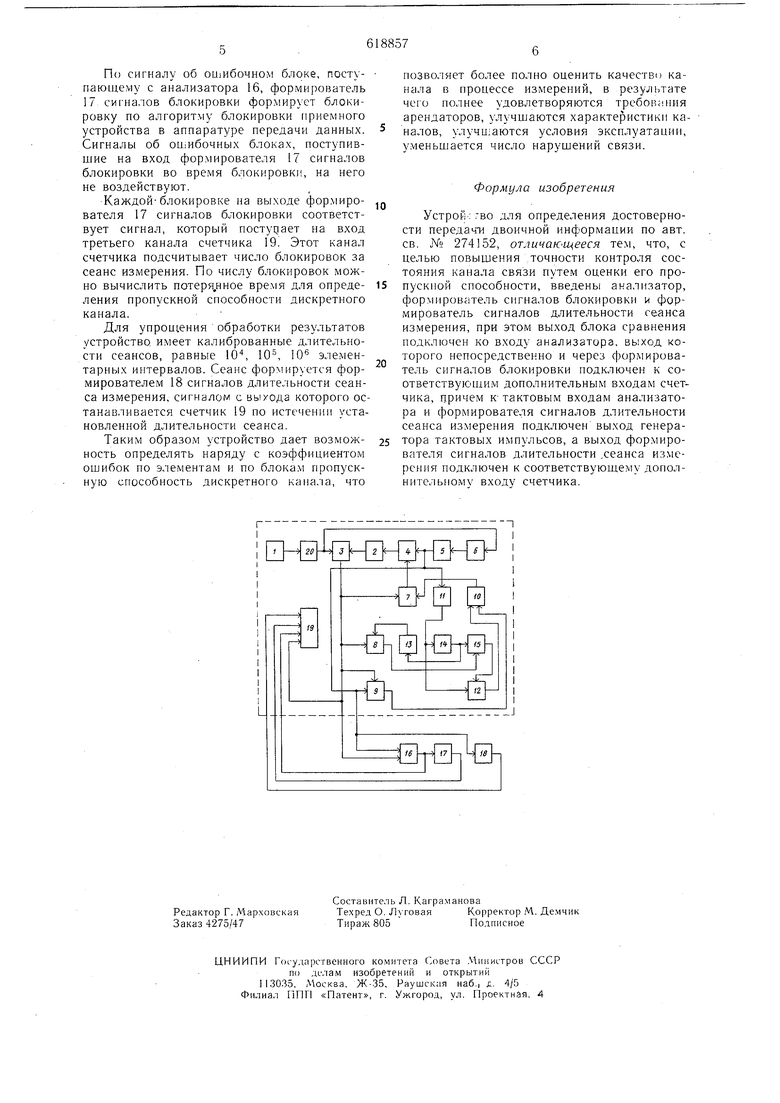

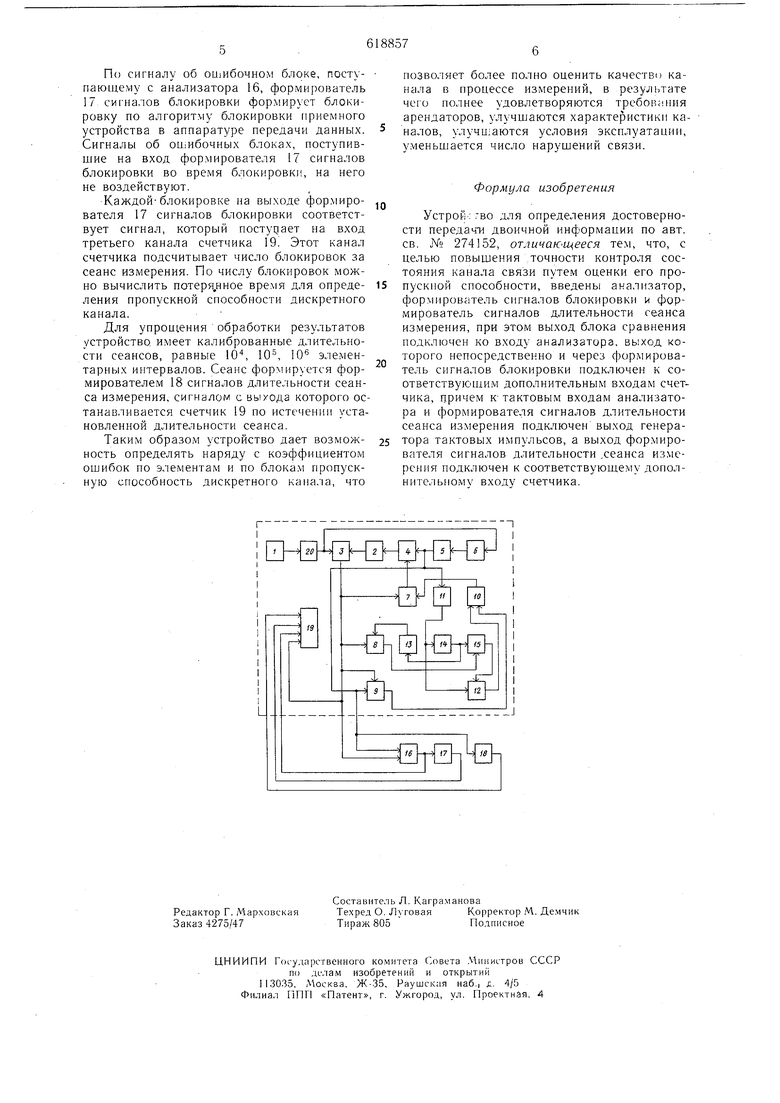

К сбросовому входу интегратора и через элемент задержки и схему запрета - к сброcoBOiViy входу интегратора, причем выход индикатора пораженных циклов соединен с запрещающим входом схемы запрета, а выход интегратора соединен со вторым входом триггера циклового фазирования, выход которого подключен ко второму входу схемы совгшдения, выход которой подключен к запрещающему входу схемы запрета, введены анализатор, формирователь сигналов блокировки и формирователь сигналов длительности сеанса измерения, при этом выход блока сравнения подключен ко входу анализатора, выход которого непосредственно и через формирователь сигналов блокировки подключен к соответствующим дополнительным входам счетчика, причем к тактовым входам анализатора и формирователя сигналов длительности сеанса измерения подключен выход генератора тактовых импульсов, а выход формирователя сигналов длительности сеанса измерения подключен к соответствующему дополнительному входу счетчика. На чертеже приведена структурная электрическая схема -предложенного устройства. Устройство для определения достоверности передачи двоичной информации содержит датчики испытательного 1 и контрольного 2 сигналов, блок 3 сравнения, схему 4 запрета, генератор 5 тактовых импульсов и систему 6 тактовой синхронизации. Выход блока 3 сравнения подключен к одному из входов схемы 7 совпадения, а также к тактово.му входу индикатора 8 пораженных циклов и к сбросовому входу индикатора 9 фазирования. При этом выход генератора 5 тактовых импульсов подключен к тактовому входу индикатора 9 фазирования, соединенному с одним из входов триггера 10 циклового фазирования, а также с управляющим входом генератора 11 меток цикла, выход которого подключен к тактовому входу интегратора 12, через элементы 13, 14 задержки - к сбросовому входу интегратора 12 и через элемент задержки 14 и схему 15 запрета - к сбросовому входу интегратора 12. Причем выход индикатора 8 пораженных циклов соединен с запрещающим входом схемы 15 запрета, а выход интегратора 12 соединен со вторым входом триггера 10. циклового фазирования, выход которого подключен ко второму входу схемы 7 совпадения, выход которой подключен к запрещающему входу схемы запрета; устройство содержит также анализатор 16, формирователь 17 сигналов блокировки и формирователь 18 сигналов длительности сеанса измерения, при этом выход блока сравнения 3 подключен ко входу анализатора 16, выход которого непосредственно и через формирователь 17 сигналов блокировки подключен к соответствующим дополнительным входам счетчика 19, причем к тактовым входам анализатора 16 и формирователя 18 сигналов длительности сеанса измерения подключен выход генератора 5 тактовых импульсов, а выход формирователя 1 сигналов длительности сеанса измерения подключен к соответствующему дополнительному входу счетчика 19, вь1ход датчика испытательного сигнала подается на вход дискретного капала 20, с выхода которого эти сигналы поступают на вход блока 3 сравнения и схему 6 тактовой синхронизации. Устройство работает следующим образом. Датчик 1 испытательного сигнала передает в дискретный канал 20 испытательный сигнал в виде двоичной периодической квазислучайной последовательности, которая имеет однозначно определенную структуру. С выхода дискретного канала 20 испытательный сигнал, подвергщийся действию мешающих факторов в канале (импульсные помехи, перерывы уровня), поступает на испытательный вход блока 3 сравнения, на контрольный вход которого от датчика 2 контрольного сигнала поступает контрольный сигнал, идентичный по структуре неискаженному испытательному сигналу. Блок 3 сравнения поэлементно сравнивает испытательный и контрольный сигналы, и, в случае несовпадения значности элементов сравниваемых сигналов, на выходе блока 3 сравнения появляется сигнал об ощибочном элементе, который засчитывается первым каналом счетчика 19. Число ощибочных эле.ментов за сеанс измерения, деленное на длительность сеанса, выраженную в элементарнькх интервалах, является коэффициентом ошибок по элементам. Для того, чтобы можно было поэлементно сравнивать два периодических сигнала, они должны быть сфазированы по циклу и синхронны. Синхронизация генератора 5 тактовых импульсов, управляющего через схему запрета 4 работой датчика 2 контрольного сигнала, обеспечивается системой 6 тактовой синхронизации. Цикловое фазирование испытательного и контрольного сигналов обеспечивается группой узлов, состоящей из схем запрета 4, 15, схемы 7 совпадения, генератора 11 меток цикла, триггера О циклового фазирования, индикатора 8 пораженных циклов, элементов 13, 14 задержки, индикатора 9 фазирования и интегратора 12. Анализатор 16 делит последовательность тактовых импульсов, поступающих от генератора 5 тактовых импульсов, на отрезки, равные длине блока. Блок информации считается ошибочным, если в течение этого периода на анализирующий вход анализатора 16 поступит, по крайней мере, один сигнал ощибки от блока 3 сравнения. С выхода анализатора 16 сигналы об ошибочных блоках поступают на вход формирователя 17 сигналов блокировки п на вход второго канала счетчика 19. Счетчик 19 подсчитывает число ошибочных блоков за сеанс измерения. Это число, деленное на общее число переданных блоков, является коэффициентом ощибок по блокам. По сигналу об ошибочном блоке, постулающему с анализатора 16, формирователь 17 сисна.юв блокировки формирует блокировку по алгоритму блокировки приемного устройства в аппаратуре передачи данных. Сигналы об ошибочных блоках, поступившие на вход формирователя 17 сигналов блокировки во время блокировки, на него не воздействуют. Каждойблокировке на выходе формирователя 17 сигналов блокировки соответствует сигнал, который поступает на вход третьего канала счетчика 19. Этот канал счетчика подсчитывает число блокировок за сеанс измерения. По числу блокировок можно вычислить потеря.нное время для определения пропускной способности дискретного канала. Для упрон1ения обработки результатов устройство имеет калиброванные длительности сеансов, равные 10, 10, 10® элементарных интервалов. Сеанс формируется формирователем 18 сигналов длительности сеанса измерения, сигналом с выхода которого останавливается счетчик 19 по истечении установленной длительности сеанса. Таким образом устройство дает возможность определять наряду с коэффициентом ошибок по элементам и по блока.м пропускную способность дискретного канала, что позволяет более полно оценить качество канала в процессе измерений, в резу пьтате чего полнее удовлетворяются требования арендаторов, улучшаются характеристики каналов, улучшаются условия эксплуатации, уменьшается число нарушений связи. Формула изобретения Устрой;:во для определения достоверности передач и двоичной информации по авт. св. № 274152, отличающееся тем, что, с целью повышения точности контроля состояния канала связи путе.м оценки его пропускпой способности, введены анализатор, формирователь спгналов блокировки и формирователь сигналов длительности сеанса измерения, при этом выход блока сравнения подключен ко входу анализатора, выход которого непосредственно и через формирователь сигналов блокировки подключен к соответствующим дополнительным входам счетчика, причем к- тактовым входам анализатора и формирователя сигналов длительности сеанса измерения подключен выход генератора тактовых импульсов, а выход формирователя сигналов длительности ,сеанса измерения подключен к соответствующему дополнительному входу счетчика.

| название | год | авторы | номер документа |

|---|---|---|---|

| УСТРОЙСТВО ДЛЯ ОПРЕДЕЛЕНИЯ ДОСТОВ^ЕЦ.ОСТИ ПЕРЕДАЧИ ДВОИЧНОЙ ИНФОРМАЦИИ | 1970 |

|

SU274152A1 |

| Устройство для определения достоверности передачи двоичной информации | 1988 |

|

SU1670794A1 |

| Устройство контроля дискретного канала связи | 1984 |

|

SU1246392A1 |

| Устройство для измерения достоверности передачи информации по дискретному каналу связи | 1982 |

|

SU1113892A1 |

| Устройство фазирования аппаратуры передачи информации циклическим кодом | 1973 |

|

SU658771A1 |

| УСТРОЙСТВО ДЛЯ ПОДСЧЕТА ОШИБОК В ТЕЛЕГРАФНЫХ И ТЕЛЕФОННЫХ КАНАЛАХ СВЯЗИ | 1972 |

|

SU432685A1 |

| Устройство для измерения достоверности передачи информации по дискретному каналу связи | 1989 |

|

SU1658396A1 |

| Устройство для цикловой синхронизации | 1981 |

|

SU1107317A1 |

| Устройство тактовой синхронизации | 1979 |

|

SU932642A1 |

| Устройство для измерения параметров в каналах передачи данных | 1974 |

|

SU493929A1 |

Авторы

Даты

1978-08-05—Публикация

1975-10-20—Подача