(54) УСТРОЙСТВО ДЛЯ ОПРЕДЕЛЕНИЯ ФАЗЫ ПСЕВДОСЛУЧАЙНОГО СИГНАЛА

| название | год | авторы | номер документа |

|---|---|---|---|

| ПРИЕМНИК ПОСЛЕДОВАТЕЛЬНЫХ МНОГОЧАСТОТНЫХ СИГНАЛОВ | 1999 |

|

RU2169993C1 |

| УСТРОЙСТВО ПРИЕМА И ПЕРЕДАЧИ ФАЗОМАНИПУЛИРОВАННЫХ КОДОВЫХ СИГНАЛОВ | 2002 |

|

RU2236086C2 |

| РАДИОПРИЕМНОЕ УСТРОЙСТВО МНОГОЧАСТОТНЫХ СИГНАЛОВ | 2005 |

|

RU2310992C2 |

| УСТРОЙСТВО ДЛЯ ОПРЕДЕЛЕНИЯ ФАЗОВОГО СДВИГА ПСЕВДОСЛУЧАЙНОЙ ПОСЛЕДОВАТЕЛЬНОСТИ | 1991 |

|

RU2013016C1 |

| РАДИОМОДЕМ | 2024 |

|

RU2830959C1 |

| Кодек квазициклического кода | 1986 |

|

SU1349010A1 |

| ПРИЕМОПЕРЕДАЮЩЕЕ УСТРОЙСТВО ШИРОКОПОЛОСНЫХ СИГНАЛОВ С ПОВЫШЕННОЙ ИНФОРМАЦИОННОЙ СКРЫТНОСТЬЮ | 1992 |

|

RU2033692C1 |

| Автокорреляционный измеритель параметров псевдослучайного фазоманипулированного сигнала | 1987 |

|

SU1518894A2 |

| Устройство синхронизации с М-последовательностью | 1981 |

|

SU1003371A2 |

| Система передачи и приема дискретной информации | 1983 |

|

SU1119184A1 |

Изобретение относится к области вычислительной техники и может быть использовано для синхронизации фазы опорного псевдослучайного сигнала на приемной стороне системы.

Известно устройство для определения фазы псевдослучайного сигнала,-содержащее коррелятор, пороговый элемент, ограничитель, мажоритарный элемент, регистры сдвига, сумматоры по модулю два. Однако это устройство не позволяет получать требуемую дсхзтоверность принимаемого сигнала l.

Наиболее близким техническим решением к данному изобретению является устройство для определения фазы псевдослучайного сигнала, содержащее генератор псевдослучайного сигнала, вход которого объединен с первыми входами блока формирования и блсжа управления и подключен к выходу генератора тактовой частоть, а выходы генератора псевдослучайного сигнала соединены со входами группы ключей, управляющие входы которых подключены к первому выходу

блсжа управления, а выходы - к разрядным входам блока преобразования фазы сигнала, первый вход которого объединен со вторым выходом блсжа управления и

подключен к вь1ходу блсжа формирования знака, второй вход соединен со вторым выходом блока управления, а выход является выходом устройства и подключен к первому входу корреляционного анализатора, выход которого соединен с третьим входом блок управления, а второй вход является входом устройства и объединен со входом фильтра низкой частоты, выход которого соединен со входом первого порогового элемента 2.

Однако это устройство обладает недостаточным быстродействием.

Целью изобретения является повышение быстродействТгя устройства.

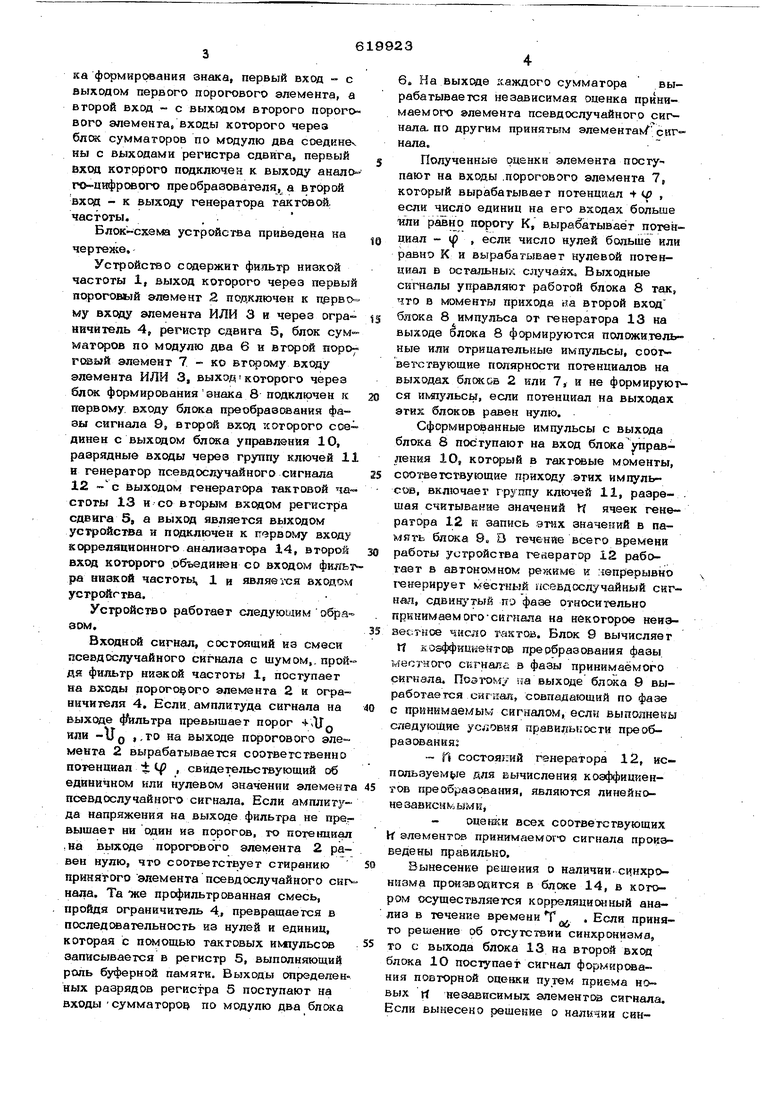

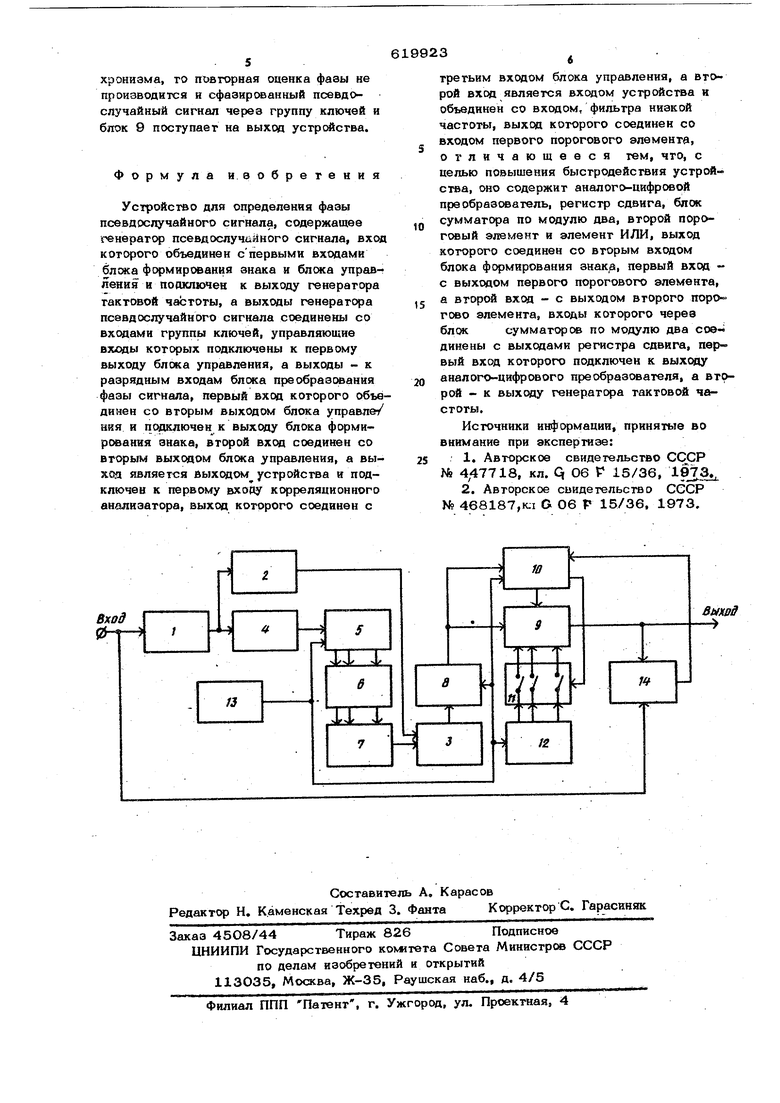

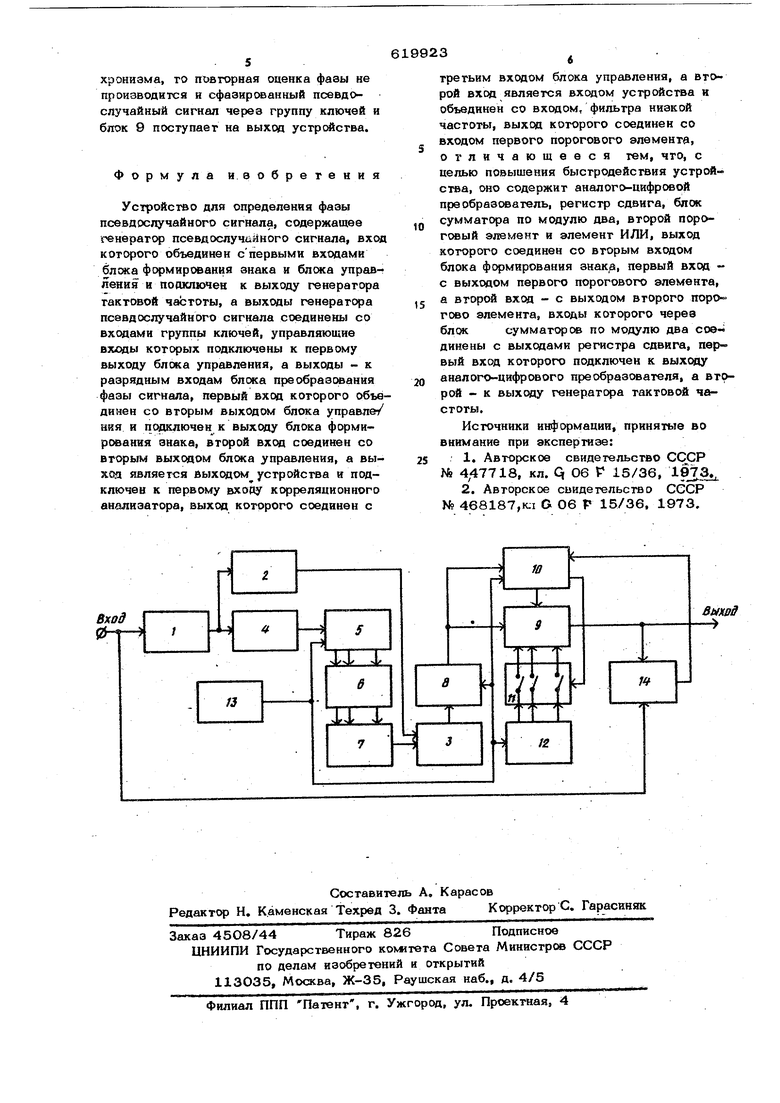

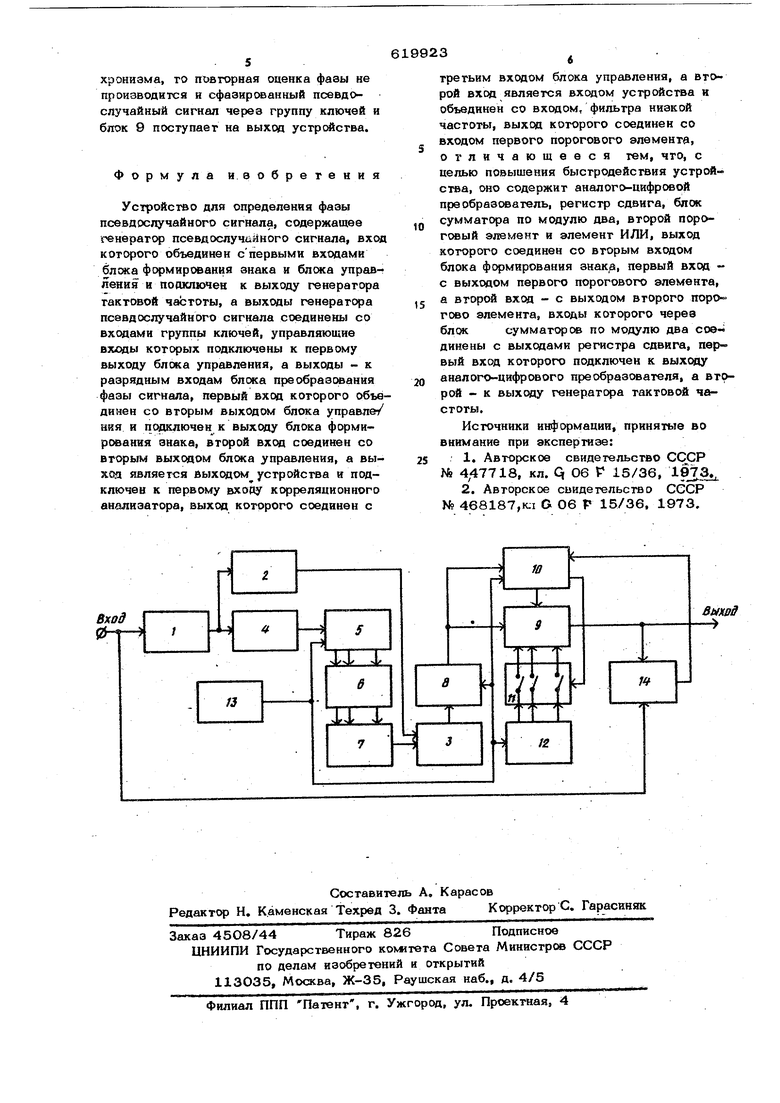

Для достижения поставленной |1ели устройство содержит .аналого-цифровой преобразователь, регистр сдвига, блок сумматоров по модулю два, второй пороговый элемент и элемент ИЛИ, выход

которого соединен со вторым входом блока формирования знака, первый вход - с выходом первого порогового элемента, а второй вход - с выходом второго пороге вого элемента, входы которого через блсж сумматоров по модулю два соединеч иы с выходами регистра сдвига, первый вхш которого подключен к выходу анало го-цифрового преобразователя, а второй вход - к выходу генератора тактовой, частоты. Блок-схэма устройства приведена на чертеже. Устройство содержит фи-льтр низкой частоты 1, выход которого через первый пороговый элемент 2 подключен к церво му входу элемента ИЛИ 3 и через ограничитель 4, регистр сдвига 5, блок сумматс ов по модулю два 6 и второй поро гшый элемент 7. - ко второму входу элемента ИЛИ 3, выход которого через блок формированиязнака 8 подключен к первому входу блсжа преобразования фазы сигнала 9, второй вход которого соа динен с выходом блсжа управлгнИя 1О, разрядные входы через группу ключей 11 и генератор псевдослучайного сигнала 12 с выходом генератора тактовой частоты 13 и со вторым входом регистра сдвига S, а выход является выходом устройства и подключен к первому входу кс реляционного анализатора 14, второй вход которого объединен со входом ра низкой частотьз, 1 и являв л-ся входтэм устройства. Устройство работает следующим обра-« зом. Входной сигнал, состоящий на смеси псевдослучайного сигнала с шумом,, пройдя фильтр низкой частоты 1, поступает на входы порогового элемента 2 к ограничителя 4. Если, амплитуда сигнала на выходе ({Ультра превышает порог -( или ,,то на выходе порогового элемента 2 вырабатывается соответственно потенциал t ф , свидетельствующий об единичном или нулевом значении элемент псевдослучайного сигнала. Если амплитуда напряжения на выходе фильтра не превышает ни один ив порогов, то потенциал ,на выходе порогового элемента 2 равен нулю, что соответствует стиранию принятого элемента псевдослучайного сиг нала. Та -же профильтрованная смесь, пройдя ограничитель 4, превращается в последовательность из нулей и единиц, которая с помощью тактовых иьиульсов записывается в регистр 5, выполняющий роль буферной памяти. Выходы определенных разрядов регистра 5 поступают на входы сумматоров по модулю два блока 6. На выходе каждого сумматора вырабатывается независимая опенка принимаемого элемента псевдослучайного сигнала- по другим принятым алементаь/ сигнала. Полученные оценки элемента поступают на входы .порогового элемента 7, который вырабатывает потенциал - ( , если число единиц на его входах больше или равно порогу К, в.ыраёатываёт потенциал - f , если число нулей больше или равно К и вырабатывает нулевой потенциал в остальных, случаях Выходные сигналы управляют работой блока 8 так, что в моменты прихода на второй вход блока 8 импульса от генератора 13 на выходе лока 8 формируются положительные или отрицательные импульсы, соответствующие полярности потенциалов на выходах блсжов 2 или 7, и не формируют ся икетульсы, если потенциал на выходах этих блоков равен нулю. Сформированные импульсы с выхода блока 8 поступают на вход блока управления 1О, который в тактовые моменты, соответствующие приходу этих импульсов, включает группу ключей 11, разре- . шая считывание значений П ячеек генератора 12 к запись ЭТИХ значений в память блока 9 В течение всего времени работы устройства геаератор 12 работает в автономном режиме к ;ieпF epывнo генерирует местный псевд(случайный сигнал, сдвинутый по фазе относительно принимаем ого-сигнала на некоторое неиэвестное число тактов. Блок 9 вычисляет Я козффицкентсчэ преобразования фазы. местного скгналг в фазы принимаемого скгнйла. Поэтому «-га выходе блока 9 выработается Сигнал, совпадающий по фазе с принимаемым сигналом, если выполнены следующие условия правильности преобразования;- П состояний генератора 12, используем(ю для вычисления коэффициентов преобразования, являются линейнонезависимыми, - оценки всех соответствующих К элементов принимаемого сигнала произведены правильно. Вынесение решения о наличии, синхронизма производится в блсже 14, в осуществляется корреляцисданый анализ в течение времени Т , Если принято решение об отсутствии синхронизма, то с выхода блока 13 на второй вход блока 10 поступает сигнал формирования повторной оценки путем приема новых rt независимых элементов сигнала. Если вынесено решение о наличии сиихронизма, го пх вгорная оценка фазы не производится н сфазированный псевдослучайный сигнал через группу ключей блок 9 поступает на выход устрсЛства. Формула изобретения Устройство для определения фазы псевдослучайного сигнала, содержащее генератор псевдослучайного сигнала, вхо которого объединен спервыми входами блсяса фсфмирования знака и блока управ пения и подключен к выходу генератора тактовой частоты, а выходы генератора псевдослучайного сигнала соединены со входами группы ключей, управляющие входы которых подключены к первому выходу блока управления, а выходы - к разрядным входам блока преобразования фазы сигнала, первый вход которого объе динен со вторым выходом блока управп Нйя и подключен к выходу блока формирования знака, второй вход соединен со вторым выходом бл(жа управления, а выход является выходом устройства и подключен к первому вхо корреляционного анализатора, выход которого соединен с 3. третьим входом блока управления, а второй вход является входом устройства и объединен со входом, фильтра низкой частоты, выход которого соединен со входом первого порогового элемента, отличающееся тем, что, с целью повышения быстродействия устройства, оно содержит аналого-цифровой преобразсжатель, регистр сдвига, блсж сумматора по модулю два, второй пороговый элемент и элемент ИЛИ, выход которого соединен со вторым входом блока формирования , первый вход с выходом первого порогового элемента, а второй вход - с выходом второго порогово элемента, входы которого через блок сумматоров по модулю два соэдинены с выходами регистра сдвига, первый вход которого подключен к выходу аналого-цифрового преобразователя, а второй - к выходу генератора тактовой частоты. Источники информации, принятые во внимание при экспертизе: 1. Авторское свидетельство СССР № 4 47718, кл. Q Об Р 15/36, 1973. 2. Авторское сиидетельство СССР NO 468187,ici О 06 Р 15/36. 1973.

Вход

J/J Ф

т:1х

Авторы

Даты

1978-08-15—Публикация

1976-12-27—Подача