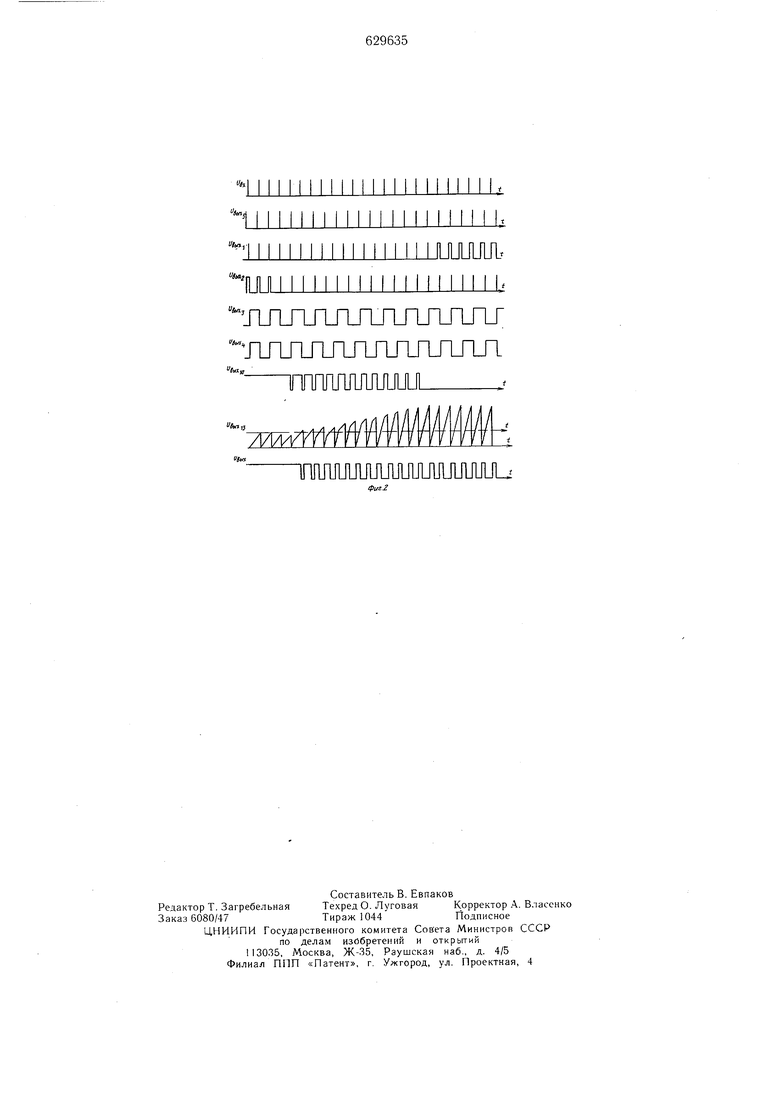

Изобретение относится к области автоматического упраВоТения и может быть использовано для синхронизации вращения электро приводов или колебаний электронных генераторов. Известен частотно-фазовый дискриминатор, содержащий два различающих и два формируюихих триггера, четыре логических элемента И, источник эталонной частоты, две дифференцирующих цепи и сумматор, вход первого различающего триггера соединен с входом частотно-фазового дискриминатора, а его выход - с- логическими элементами И, включенными между выходом третьего и входом четвертого формирующих триггеров, источник эталонной последовательности импульсов соединен со входом второго различающего триггера, выход которого соединен с логическими элементами И, включенными между выходом четвертого и входом третьего формирующих триггеров, выход третьего формирующего триггера соединен с входом второго, а выход четвертого - с входом первого различающего триггера через дифференцирующие цепи, четыре выхода формирующих триггеров соединены с сумматором, выход которого соединен с выходной клеммой дискриминатора. Цель изобретения - регулирование коэффициента передачи при постоянном напряжении питания и периоде повторения импульсов. Это достигается тем, что в известный частотно-фазовый дискриминатор, содержащий два различающих и два формирующих триггера, четыре логических элемента И, источник эталонной частоты, две дифференцирующие цепи и сумматор, источник измеряемой последовательности импульсов, введены пороговое устройство и интегратор, при этом первый и второй входы интегратора соединены соответственно с выходом сумматора и входом дискриминатора, выход интегратора соединен с входом порогового устройства, выход которого соединен с выходной клеммой дискриминатора. При этом выходы формирующих триггеров объединены при помощи сумматора, построенного на двух логических элементах И и логическом элементе ИЛИ. Выход сумматора соединен с первым входом интегратора, а второй вход интегратора соединен с входом.дискриминатора. На фиг. 1 представлена блок-схема частотпо-фазового дискриминатора; на фиг. 2 временные диаграммы, поясняюн ие его работу. Частотно-фазовый дискриминатор содержит два различающих триггера 1 и 2, два формирующих триггера 3 и 4, источник 5 эталонной частоты, две дифференцирующих цепи 6 и 7, логические элементы И 8 и 9, суммато 10, состоящий из. двух логических элементов И 11 и логического элемента ИЛИ 12, интегратор 13, пороговое устройство 14, приче.м выходы различающих триггеров 1 и 2 соединены через дифференцирующие цепи 6 и 7 с выходами фор.мирующих триггеров 3 и 4. Каждый из выходов формирующего триггера 3 соединен с соответствующим выходом различающего триггера 1 и с соответствующим входом формирующего триггера 4 через логический элемент И 8, а каждый из выходов формирующего триггера 4 соединен с соответствующим выходом различающего триггера 2 и с соответствующим входом формирующего триггера 3 через логический эле.мент И 9. Работа дискриминатора осуществляется в .:1,ва этапа. 1. Синфазная память. Формирующие триггеры 3 и 4 находятся во взаимосинфазных положениях (открыты оба левых или оба правых транзистора этих триггеров). При этом на выходе сумматора 10 логическая «1 (высокий уровень напряжения), интегрирование происходит с постоянной времени Cj . Синфазная фиксация. Формирующие триггеры 3 и 4 находятся во взаимосинфазных положениях, а на вы.ходе сумматора логическая «1 (высокий уровень напряжения, который подается па интегратор), интегрирование происходит с постоянной времени Т;. Отличие этого состояния логической части дискри.минатора от предыдуц;его состоит в том, что различающий триггер 1 находится в положении «Разрешено, характеризуемое тем, что напря-. жения с выходов формирующего триггера 3 поступают через логические элементы 8 на входы формирующего триггера 4 и фиксируют его в синфазном (по отношению к формирующему триггеру 3) положении. 2. Противофазная память. Формирующие триггеры 3 и 4 находятся во взаимопротивофазных состояниях и на выходе су.мматора 10 логический «О.-Интегрирование происходит с постоянной времени -Сг- Различающие триггеры 1 и 2 находятся в положении «Блокировка. Противофазная фиксация. Формирующие триггеры 3 и 4 находятся во взаимопротивофазных состояниях, и на выходе сумматора 10 логический «О. Интегрирование происходит с постоянной времени tj. Это состояние отличается от предыдущего тем, что напряжения с выходов формирующего триггера 4 поступают через соответствующие элементы 9 на входы формирующего триггера 3 и фиксируют его в противофазном (по отноп1ению к формирующему триггеру 4) положении. Формула изобретения Частотно-фазовый дискриминатор по авт. св. NO 379049, отличающийся тем, что, с целью регулирования коэффициента передачи при постоянном напряжении питания и периоде повторения импульсов, в него введены пороговое устройство и интегратор, при этом первый и второй входы интегратора соединены соответственно с выходом сумматора и входом дискриминатора, выход интегратора соединен с входом порогового устройства, выход которого соединен с выходной клеммой дискримииатора.

%| . ,.I

UlMi

lUUL

1Ш11Ги1 Г1Г1Л Г1Л Л

. nrJlJTrirLJl n rLrU LrL

1пш1 ишишш1Ж1ииши

IMMJl

| название | год | авторы | номер документа |

|---|---|---|---|

| УСТРОЙСТВО ПОИСКА И СОПРОВОЖДЕНИЯ СИГНАЛА СИНХРОНИЗАЦИИ В СПУТНИКОВЫХ СИСТЕМАХ СВЯЗИ ПО ПРИЕМУ | 1995 |

|

RU2093964C1 |

| Способ определения знака разности частот и устройство для его реализации | 2016 |

|

RU2625054C1 |

| УСТРОЙСТВО ПОИСКА СИГНАЛА СИНХРОНИЗАЦИИ СПУТНИКОВОЙ СИСТЕМЫ СВЯЗИ | 1995 |

|

RU2093963C1 |

| СТАБИЛИЗИРОВАННЫЙ ЭЛЕКТРОПРИВОД | 2016 |

|

RU2621288C1 |

| ЧАСТОТНО-ФАЗОВЫЙ ДИСКРИМИНАТОР | 1973 |

|

SU379049A1 |

| Преобразователь фазового угла в постоянное напряжение | 1978 |

|

SU765747A1 |

| Устройство для передачи и приема многочастотных сигналов с относительной фазовой манипуляцией | 1984 |

|

SU1259500A1 |

| Устройство для управления вентильным преобразователем | 1983 |

|

SU1094129A1 |

| Устройство для управления регулируемым мостовым инвертором | 1988 |

|

SU1548830A1 |

| ДАТЧИК НУЛЕВОГО ТОКА | 2009 |

|

RU2390906C1 |

Авторы

Даты

1978-10-25—Публикация

1976-06-28—Подача