1

Изобретение опнооится ,« зыч/ислительной технике и :маж€т быть использавано для лостроения сдниговых (регИСТ|рО)В -ъ дискретных устройспвах вычислительной техники я автоматики.

Известны -ямейки палгяти для репистр-ов сдвига, (Построенные ;на триггерах потенциального тина .

Наиболее близка по техиичоакой сущности к изобретению 1ячей|к.а 1па|МятИ, содержащая триггер, ,вход (И выход которого яаляютс.я соответственно входом и выходом ячейии (па1мяти .

Одиако В известных ячейках не решена задача 1ко1Нт|роля инфюрмацин, содержащейс,я IB них.

Цель изой|ретения - 1повышение достоBeipiKOCTiH хра.нвН1ИЯ И Н|ф 0 р ма|Ции.

Поставланна.я Цель достигается тем, что в ичейму памяти вюеден счепный триггер, эле-меит НЕРАВНОЗНАЧНОСТЬ и два элемагта ЭКВИВАЛЕНТНОСТЬ, входы первого эле-меита ЭКВИВАЛЕНТНОСТЬ подклюЧбны соответсБнеино к входу и выходу триггера, г .зы.ход - к nepiBoiMy входу элемента НЕРАВВОЗНАЧНО-СТЬ и входусчетного триггера. Выход счетного триггера явЛяется .вторым вьиходом Ячейки .памяти и п-ервым входом втарого элемента ЭКВИВАЛЕНТНОСТЬ, второй вход которого служит BTOipbiiM в.ходом ячейки па(Мл,ти. Выход второго элемента ЭКВИВАЛЕНТНОСТЬ подключен « второму входу элемента НЕРАВНОЗНАЧНОСТЬ, выход iKOTOiporo соединеи :с третьи1М выходом ячейки . Первый элемент ЭКВИВАЛЕНТНОСТЬ прогнозирует пере.к.иочения триггера Ячейки на1мяти и управляет работой счетного триггера та:Ким образом, что есл1И три очередиом сдвиге И нформации в регистре триггер сохраияет свое состояние, то переключается счетный тр:и;ггер, а есл) трипгор переключается в противоположное состояние, го счетный триггер со.мраняет свое состоянше. Второй ,Вход ячейки паад.ятл подключается :к второму выходу .предыдущей ячейки репистра сдвига. Такое шостроение обеспечивает .совладение кодов .на выходах обоих элеменггоа ЭКВИВАЛЕНТНОСТЬ, поэтому подключение их к ахода.м Элемента НЕРАВНОЗНАЧНОСТЬ позволяет .контролировать .информацию, содержащуюся в ячейке 1па1мяти. Едии.ица на выходе элемента НЕРАВНОЗНАЧНОСТЬ овидетельствует об искаже.гии Информа.ции в ячеЙ1ке памяти.

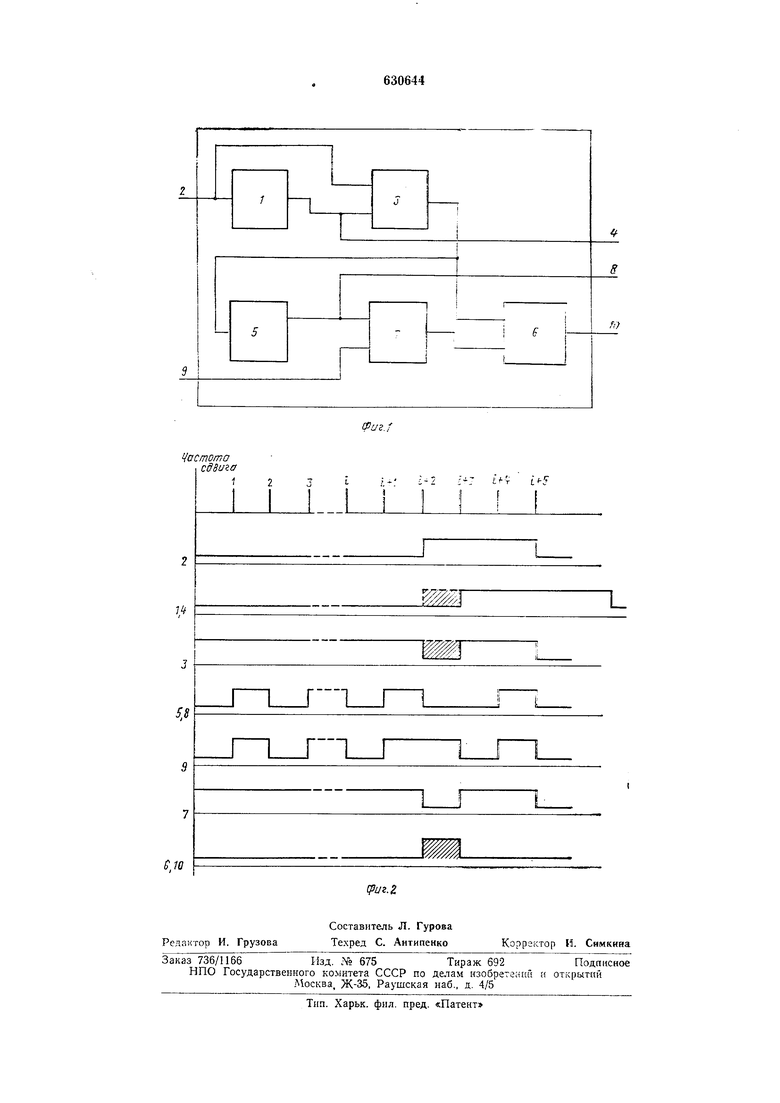

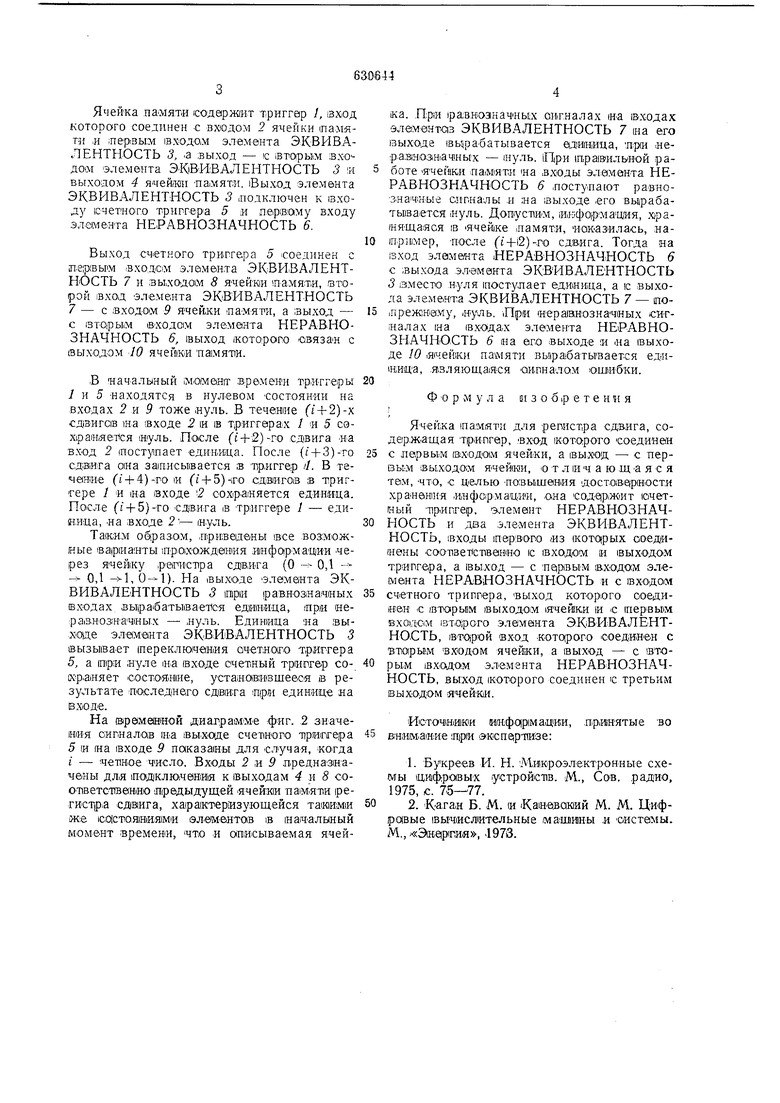

На ф.иг. 1 приведена блок-схема ячейки памятн; иа фшг. 2 - времениая диа;гра1мма ее работы.

Ячейка памяти содержит триггер /, 1зход которого соединен с вхюдом 2 ячейки тамяти .и лервьш 1ВходО;М элемента ЭКВИВАЛЕНТНОСТЬ 3, .а выход - с iBTQpbiM элемента ЭШИВАЛЕНТНОСТЬ 3 к выходом 4 Ячейш ламяти. Выход элемента ЭКВИВАЛЕНТНОСТЬ 3 .подключен к IBXOд} |счетното триггер а 5 и перйюму входу элемента НЕРАВНОЗНАЧНОСТЬ 6.

Выход счетного триггера 5 соединен с 11.е|р1ВЫ1М ;Входс М элемента ЭКВИВАЛЕНТНОСТЬ 7 и зы ходом 8 Ячейюи ша.мяти, зторой вход элемента ЭКВИВАЛЕНТНОСТЬ 7 - с входо1М 9 ячейки па-мяти, а выход - с 1вто|рЫ|М ВХОД01М элемента НЕРАВНОЗНАЧНОСТЬ 6, 1ВЫХОД которого оэязащ с (ВЫХОДОМ 10 ячей1Кй па1МЯ пи.

В нач-альный iMOiMQHiT времена- триггеры / и 5 Находятся в нулевом состоянии на входах 2 и 9 тоже нуль. В течение (i + 2)-x сд1вигс1в ша 1входе 2 н IB Т|риггерах / -и 5 сэхратяепся иуль. После (i+2)-r-o сдвига вход 2 (Поступает единица. После {г+3)-го сд;ви;га 01на затисывается ;в Т)р,иггер //. В течение (1-|-4)-:гои (i + 5}-iro СД|В1ИГО|В s триггере / и «а аходе 2 сохраняется единица. После (г-ь5)-го сдвига в триггере 1 - едииица, и а входе 2- йадь.

Та(ки.м офазом, иривадены все возможные 1ва р1иа1нты 1пр01хожд1вния инфорМации через ячейку р-агистра сдиига (О -- ОД - - 0,1 ,0--1). На выходе элемента ЭКВИВАЛЕНТНОСТЬ 3 гари равиозначных входах выр.абатываетЮя единица, при нерааноэНачны.х - нуль. Единица иа 1выхо)де элемента ЭКВИВАЛЕНТНОСТЬ 3 вызывает (переключения очетиого триггера 5, а при нуле иа входе счетный триггер сокр.аияет Состояние, уста1НО(ви1ВшебСЯ в результате ИОследиего сдв1и;га ири единице на вхОде.

На |вре1меюной диа.г рамМе фиг. 2 значения с;иГНаЛ0|В 1Н:а выходе счетного пришгера 5 и на входе 9 паказаиы для случая, Котда г - ч€т1НОе ЧИСЛО. ВхОды 2 я 9 лреднаЗНзчены ДЛЯ 1Подклк ченИ|Я к выходам 4 и 8 соОТ1ветст1ввН|НО предыдущей ячейжи па1МЯТ1И ipeгиСТ|рл , ха1ра ктер изующейся таии-лии же 1с;астоягаи:Я1ми элементов IB иачалыный момент времени, что и аписываемая ячейка. При 1равноэначнььх сигналах иа входах элементаз ЭКВИВАЛЕНТНОСТЬ 7 на его выходе вьфабатывается единица, п-ря иера;в1нозн1ач ных - нуль. 1При ираюильНОЙ работе Ячейки Памяти «а входы эЛвманта НЕРАВНОЗНАЧНОСТЬ 6 поступают равнозлачные оипиалы и ;на выходе его вьфабатьивается |Нуль. Дошусти, икфор-мащия, xipa/нящаяоя IB ячей|ке иамяти, исказилась, иатример, иосле (1+в)-г-о сдвига. Тогда на 13.ХОД элемента НЕРАВНОЗНАЧНОСТЬ 6 с выхода эл-эмента ЭКВИВАЛЕНТНОСТЬ 3 iBMecTO нуля поступает едииииа, а ю выхода элемента ЭКВИВАЛЕНТНОСТЬ 7 - по1преж1нвму, Иуль. (При иера1нн10знач1ных сигналах 1на 1входах элемента НЕРАВНОЗНАЧНОСТЬ 6 на его выходе и иа выходе 10 1Я1чеЙ1ки пачмяти вы1ра батывается едищища, являющаяся оилналом оивибки.

Форм у л а 3 о б ip е т е н и я

Ячейка памяти для репистра сдвига, содержащая трипгер, .вход котарого соединен с лервым (Выходам ячейки, а выход - с первь:,м ВЫХОДОМ ячейки, о т л и ч а ю щ а я с я тем, что, с целью повышения достов риости хранения инфо рмациИ, она содчрЖит ючетный т|рипге|р, элемент НЕРАВНОЗНАЧНОСТЬ и два элемента ЭКВИВАЛЕНТНОСТЬ, 1ВХОДЫ nepiBODo из которых ооед/инены соот1зеисБввн1НО ic входом и выходом трилгера, а 1вы.ход - с иервым входом элвмента НЕРАВНОЗНАЧНОСТЬ и с входам счетного трилгера, выход которого ооедияен с вторьпм выходом 1ячей1ки 1И с иервым BxofiCiM второго элемента ЭКВИВАЛЕНТНОСТЬ, 1вто1рой (ВХОД -KOTqporo СоедиНбн с вторым входом ячейки, а выход - с вторым входом элемента НЕРАВНОЗНАЧНОСТЬ, выход которого соединен с третьим выходом ячеййи.

Источники итф-чрмащии, ЛринЯтые во inipiH экспе1р ли:зе:

1.Букреев И. Н. МнкроэлектрОнные схемы 1ЦИ|фровыХ устрайст1в. М., COIR, радио, 1975, с. 75-77.

2.Каган Б. М. 1и |Ка1Не(вак1Ий М. М. Ц-ифравые 1вьгЧ1ИСЛ1ительные ма Ш1И1ны и оиствмы. М., к Экарг Ия, 1973.

| название | год | авторы | номер документа |

|---|---|---|---|

| Генератор псевдослучайных чисел | 1980 |

|

SU935951A1 |

| Буферное запомнающее устройство | 1976 |

|

SU630645A1 |

| ПРЕОБРАЗОВАТЕЛЬ КОД — АНАЛОГ | 1973 |

|

SU406318A1 |

| ЭЛЕМЕНТ ВЫЧИСЛИТЕЛЬНОЙ СРЕДЫ | 1970 |

|

SU259475A1 |

| Преобразователь формы представления логических функций | 1983 |

|

SU1164728A1 |

| Многоканальное устройство для обслуживания запросов | 1978 |

|

SU769542A1 |

| Регистр сдвига | 1980 |

|

SU877618A1 |

| Генератор псевдослучайных чисел | 1981 |

|

SU1013955A1 |

| СО АН СССР | 1969 |

|

SU239661A1 |

| Устройство для перебора сочетаний | 1973 |

|

SU512472A1 |

Частота сдЗига

1 2

«

i-Ti -

1

Авторы

Даты

1978-10-30—Публикация

1976-10-04—Подача