I

Изобретение относится к вычисли- ; тельной технике и предназначено для распределения входных импульсов а также импульсов, длительность которых равна периоду следования входных импульсов, по m выходным шинам (m-k, k+1, k+2,...,n), (где .k - номер разряда, на управляющий вход которого подан сигнал управления, an - число разрядов регистра).

Известно устройство, которое содержит в каждом разряде триггер памяти и логические элементы D3«

Однако это устройство вьтолнено на большом количестве оборудования что существенно снижает общую надежность устройства. Кроме того, оно не позволяет распределить входные сигналы по выходным шинам.

Наиболее близким к предлагаемсжу по технической сущюсти является регистр сдвига содержащий коммутационный триггер и IV разрядов, каждый из которых содержит основной триггер

вспомогательньтй триггер и логический элемент И-НЕ 2.

Недостатком известного устройства является его сложность.

Цель изобретения - упрощение устройства.

Поставленная цель достигается тем что в регистр сдвига, содержащий ячейки памяти, каждая из которых состоит из триггера и из первого элемента И-НЕ, первый коммутирующий триггер, первый выход которого соединен с первыми входами первых элементов И-НЕ, вторые входы которых подключены соответственно к шинам управления, первый вход первого коммутационного т-риггера соединен со входом, регистра сдвига, введены второй коммутационный триггер, а в каддую ячейку памяти - второй элемент И-НЕ

ао причем первые входы вторых элемен- тов И-НЕ соединены со входом регистра сдвига, второй вход второго элемента И-НЕ каждой ячейки памяти, кроме первой и последней, соединен с первым выходом триггера предьщущей ячейки памяти,- третий вход второго элемента И-ИЕ каждой ячейки памяти соединен с выходом второго элемента И-НЕ, с первым йходом триггера и выходом предыдущей ячейки памяти, выход второго элемента И-НЕ каждой ячейки памяти соединен с первым входом триггера и выходом данной ячейки памяти и с одним из входив второго элемента И-НЕ последующей ячейки памяти, второй вход триггера каждой ячейки памяти соединен с выходом второго элеме11та И-НЕ и с выходом последующей ячейки памяти третий вход триггера каждой ячейки памяти соединен с выходом первого элемента И-НЕ последующей ячейки памяти, четвертый вход триггера каяэдой ячейки памяти соединен с одним из вы- ходов триггера последующей ячейки памяти, третьи входы первых элементов И-НЕ ячеек памяти соединены со вторым входом первого коммутационного триггера и с выходом последней ячейки памяти, выход триггера которой соединен с третьим входом первого коммутационного триггера, второй выход которого соединен с одним из входов триггера последней памяти, первый вход которого коммутационного триггера соединен с выходом первого элемента И-НЕ первой ячейки памяти, второй вход второго коммутационного триггера подключен к одному из выходов триггера первойячей ки памяти, третий вход второго коммутационного триггера соединен с выходом первого элемента Й-НЕ и и выходо первой ячейки памяти, выход второго коммутационного триггера соеди нен со вторым входом BTQporo элемента И-НЕ первой ячейки памяти.

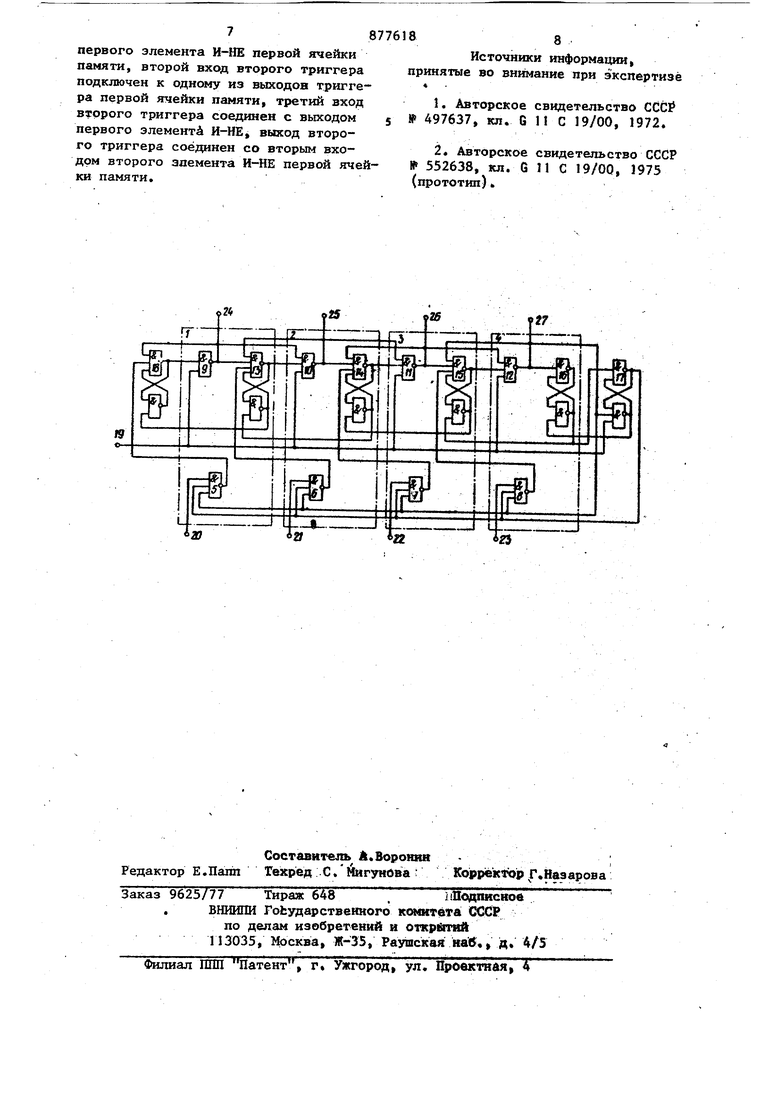

На чертеже изображена функциональная схема регистра сдвига.

Регистр содержит ячейки 1-4 памяти (на чертеже показаны только четыре ячейки памяти), первые элементы И-НЕ 5-8, вторые элементы И-НЕ 9-12, триггеры 13-16 ячеек 1-4 памяти, первый 17 и второй 18 коммутационные триггеры, вход 19 регистра сдвига, шины 20-23 управления и выходы 2427 регистра сдвига.

УстройствЬ работает следукщим образом. ,

В исходном состоянии триггер четвертой ячейки 4 памяти установлен в

единичное состояние, а триггеры 1315 остальных ячеек памяти 1-3 и триггер 18 установлены в нулевое состоя ние {шина установки на чертеже не

показана). Входной сигнал, подаваемый на вход 19, отсутствует (равен логическому нулю). В этом случае на выходах триггера 17 будет сигнал, равный логической единице.

Пусть, например, на шинах 20,

22, 23 присутствует логический нуль, а на шине 21 - логическая единица. Тогда на выходах элементов И-НЕ 5, 7, 8 будет сигнал, равный логической единице, а на выходе - элемента И-НЕ 6 - логический нуль, который установит триггер 13 в единичное состояние.

Поэтому с приходом первого вхОдного сигнала на вход 19 на нулевом вьгходе триггера 17 появляется сигнай, равный логическому нулю, который устанавливает триггер 16 последней ячейки 4 памяти в нулевое состояние.

Одновременно на выходе элемента

И-НЕ 10 появляется сигнал, равный ло гическому нулю, который устанавливает триггер 14 вединичное состояние, при этом на нулевом выходе триггера 13 установится сигнал, равный nojfiiчесйой единице. Наличие связи с выхода элемента И-НЕ 10 на вход элемента И-НЕ 1I .и на единичный вход триггера I3 препятствует появлению на их выходах логического нуля во время действия первого входного сигнала. После окончания действия первого входного сигнала на нулевом выходе триггера 17 установится { сигнал, равный логической единице, а на единичном выходе триггера 17 логический НУЛЬ, который закрывает элементы И-НЕ 5-8. На единичном выходе триггера 13 установится сигнал, равный логическому нулю, который закроет элементы И-Effi 5-8. На единичном вьосбде триггера 13 установится сигнал, равный логическому нулю, который закроет элемент И-НЕ 10.

Таким образом, на выходе элементу

0 И-НЕ 10 будет сформирован сигнал, длительность которого равна длительности входного сигнала, и который с выхода 25 может быть распределен по. одной из последуищих выходных шин.

5 С приходом второго сигнала на вход 19 на выходе элемента И-НЕ 1i появляется сигнал, равный логическому нулю, который устанавливает триггер 5 15 в единичное состояние, при этом н нулевом выходе триггера 14 появляется сигнал, равный логической единице. Наличие связи с выхода элемент И-НЕ 11 на вход элемента И-НЕ 12 и на единичный- вход триггера 14 препятствует появлению на их выходах ло гического нуля во время действия вто рого входного сигнала. После оконча 1ия действия второго входного сигнала на единичном выходе триггера 14 появляется сигнал, равный логи ческому нулю, который закроет элемент И-НЕ 11, Таким образом, с выхода 2fr может быть распределен по следующей выходной шине сигнал, длитель ность которого равна длительности входного импульса. Аналогичным образом с приходом третьего входного сигнала на выходе элемента И-НЕ 12 появляется сигнал, равный логическому иулю, который устанавливает триггер 16 в единичное состояние, при этом на нулевом выходе триггера 15 появляется сигнал, равный логической единице, а на еди ничномвыходе триггера 17 - логическая единица. Наличие связи с выхо да элемента И-НЕ 12 на единичный вхо триггера 15, на нулевой вход триггера 17 и на входы элементов И-ЙЁ 5-8 препятству ет появлению на их выходах логического нуля во время действия третьего входного сигнала. После окончания действия третьего входного сигнала на единичном выходе триггера 15 появляется сигнал, равный логическому нулю который закроет элемент И-НЕ 12, ас выхода 27 может быть распределен сигнал длительность которого равна длитель- иости входного ш«1ульса. Видно, что после окончания действия третьего входного сигнала регистр опять находится в исходномсос тоянии. Если не произойдет изменения сигналов на пганах 20-23, то цикл раб ты регистра повторится Аналогичным образом при наличии на управлякядем входе первого элемент И-НЕ п-го (, 2, 3,...,N) разряда сигнала, равного логической единице, будет осуществляться распределение сигналов по m (, К+1, K+2,...,h), выходным ппшам. Введение в известный регистр сдйи га второго триггера, а в казкдую ячей ку памяти - второга элемента , позволяет исключить из каждой ячей8ки памяти вспомогательный триггер, что ведет к сокращению количества логических элементов, повышению надежности, уменьшению потребляемой мощности. Формула изобретения Регистр сдвига, содержащий ячейки памяти, каждая из которых состоит из триггера и из элемента И-НЕ, первый коммутационный триггер, первый выход которого соединен с первыми входами первых элементов И-НЕ, вторые вхрды которых подключены к шинам управления, первый вход первого коммутационного триггера соединен со входом регистра сдвига, о т л и ч а ю щ и и с я тем, что, с целью упрощения регистра сдвига в него введены второй коммутационный триггер, а в каждую ячейку памяти - второй элемент И-НЕ, причем первые Bxojoibi вторых элементов И-НЕ соединены со входом регистра сдвига, второй вход второго элемента И-НЕ каждой ячейки памяти, кроме первой и последней, соединен с первым выходом триггера предьщущей ячейки памяти, третий вход второго элемента И-НЕ каждой ячейки памяти соединен с выходом второго элемента И-НЕ, с первым входом триггера и выходом предьщущей ячейки памяти, выход второго элемента И-НЕ каждой ячейки памяти соединен с первым входом тригге1ра и выходом данной ячейки памяти и с одним из входов второго элемента И-НЕ последующей ячейки памяти, второй вход триггера ячейки памяти соединен с выходом второго элемента И-НЕ и с вьтходом последующей ячейки памяти, третий вход триггера каждой ячейки памяти соединен с выходом первого элемента И-НЕ последующей ячейки памяти, четвертый вход триггера каждой ячейки памяти соединен с одним из выходов триггера последующей ячейки памяти, третьи входы первых элементов И-НЕ ячеек памяти соединены со вторым входом первого Коммутационного триггера и с выходом последней ячейки памяти, выход триггера которой соединен-с третьим входом первого коммутгщионно- го триггера, второй выход которого соединен с одним из входов,триггера последней ячейки памяти, первый вход второго триггера соединен с выходом

первого элемента И-НБ первой ячейки памяти, второй вход второго триггера подключен к одному из выходов триггера первой ячейки памяти, третий вход второго триггера соединен с выходом первого элемент И-НЕ, выосод второго триггера соединен со вторым входом второго элемента И-НЕ первой ячейки памяти.

Источники информацииI принятые во внимание при экспертизе

4

1.Авторское свидетельство ССС 497637, кл. G 11 С 19/00, 1972.

2.Авторское свидетельство СССР № 552638, кл. G 11 С 19/00, 1973 (прототип)

| название | год | авторы | номер документа |

|---|---|---|---|

| Распределитель импульсов | 1980 |

|

SU884136A1 |

| Многопрограммный делитель частоты | 1980 |

|

SU924866A1 |

| Делитель частоты следования импульсов | 1979 |

|

SU873417A1 |

| Регистр сдвига | 1975 |

|

SU552638A1 |

| Делитель частоты следования импуль-COB HA 15 | 1979 |

|

SU818022A1 |

| МОДУЛЬ МАТРИЧНОГО КОММУТАТОРА | 1996 |

|

RU2116664C1 |

| Делитель частоты следования импульсов | 1980 |

|

SU886248A2 |

| Устройство для сопряжения центрального процессора с группой арифметических процессоров | 1984 |

|

SU1254495A1 |

| Делитель частоты на четыре, пять | 1976 |

|

SU744996A1 |

| Делитель частоты | 1979 |

|

SU845291A1 |

Авторы

Даты

1981-10-30—Публикация

1980-02-15—Подача