Элемент вычислительной среды предназначен для использования в вычислительной технике. Основной областью применения предлагаемого элемента является иоетроение высоконадежных вычислительных сред.

Известны элементы вычислительной среды, в которых с целью повышения надежности используется система настройки, позволяющая локализовать неисправности отдельных элементов.

Предлагаемый элемент отличается от известного тем, что с целью повышения гибкости настройки и эффективности использования вычислительной среды он содержит блок памяти и выбора направлений, выполненный на триггерах, выходы которых соединены со входами схем «И выбора направления передачи возбуждения, входами схем «И выбора на:праБле 1ИЯ иередачи настроечной информации U1 входами схемы «ИЛИ, выход которой через линию задержки и усилитель-формирователь .соедииен со входами схем «И выбора напразлення.

Предлагаемый элемент отличается от известного также тем, что содержит схемы «И выбора направления, первые входы которых соединены с выходом триггера активности, второе входы - с источником импульсов, разрешающих содержимое регистра сдвига передать в блок памяти выбора нанравлений.

третьи входы через инвертор, усилитель-формирователь. ли«ию задерж.ки ц схему «ПЛИ- - с выходами триггеров блока намяти выбора направленнй, четвертые входы - с

Еыходамн регпстра сдвига, а выходы - с единичными входами триггеров блока памяти выбора направлений.

Кроме того, предлагаемы элемент отличается от известного тем, что содержит схемы

«-И выбора наиравления иередачи настроечной информации, первые входы которых соединены с выходами триггеров блока памяти выбора наиравлени, вторые - с выходом последиего триггера регистра сдвига, а выходы - с настроечными выходами элемента.

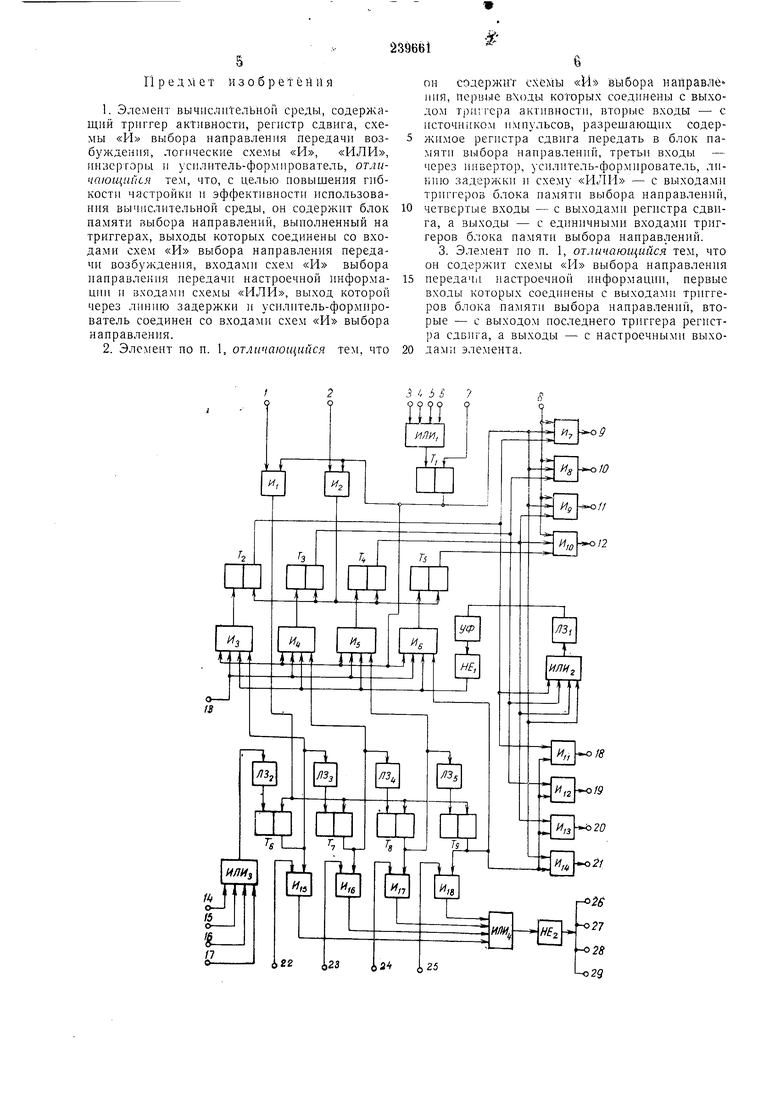

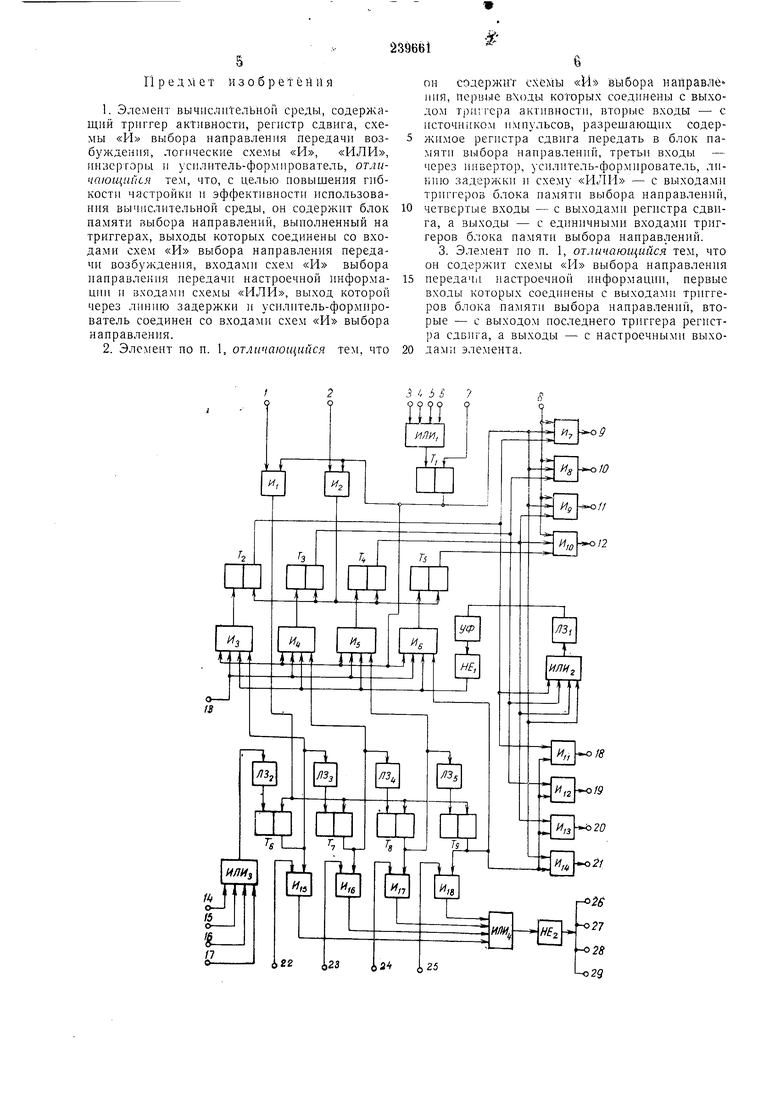

На чертеже прнведена функциональная схема предлагаемого элемента вычислительной среды. Элемент содержит триггеры , логические схемы . реализующие операцию «коиъюнкция, логические схемы ИЛИ1 -- «ИЛИ4, реализующие операцию «дизъюнкция, схемы «nEi и «IIE2, усилитель-формирователь УФ и линии задержки

,/73i-ЛЗ. Триггер Т активности совместно со схемами «Hi -«I-ij, «HEi, усилителемформирователем н лниней задержки ЛЗ управляет работой элемента. Схемы «Из -«Ио предназначены для выбора направлеправления передачи возбуждения, схемы - для выбора направления передачи настроечной информации.

Триггеры Г2-TS образуют блок памяти выбора направления, триггеры 7в-Т,, вместе с линиями задерл ки ЛЗо-ЛЗ образуют регистр сдвига. Логические схемы «His -«Hiy, ИЛИ4 и «НЕо составляют логический элемент.

Вход У предназначен для подачи уиравляющих (сдвигающих) импульсов на регистр сдвига, вход 2 - для установки триггеров иамяти выбора направления в нуль. Входы 3- 6 - возбуждающие входы элемента, на которые поступают сигналы с возбуждающих выходов соседних элементов или извне. Вход 7 предназначен для установки в нуль триггера активности, вход 8 - для подачи импульсов, разрешающих передать содержимое памяти выбора направлений на возбуждающие выходы элемента. Выходы 9-12 - возбуждающие выходы элемента.

Вход 13 предназначен для подачи импульсов, разрешающих содержимое регистра сдвига передать в память выбора направлений; входы 14-/7 - настроечные входы, на которые поступает настроечная информация (код настройки) с настроечных выходов соседних элементов или извне; выходы 18-21 - настроечные выходы; входы 22-25 - логические входы элемента; выходы 26-29 - его логические выходы.

Если триггер активности находится в состоянии «единица, то он выполняет следующие функции: разрешает установить в нуль триггеры блока памяти выбора направлений сигналом, поступающим на вход 2; разрешает переписать код из регистра сдвига в блок памяти выбора направлений сигналом, иоступающим со входа 13 на схемы выбора направлений; разрешает подать в регистр сдвига управляющие сдвигающие импульсы, поступающие на вход /; разрешает передать содержимое блока памяти выбора иаправлений на возбуждающие выходы 9-12, если на вход 8 подан разрещающий сигнал.

Блок памяти выбора направлений предназначен для хранения кода, определяющего, какому из соседних элементов должна передаваться информация настройки. Сигналы с триггеров блока памяти выбора направлений поступают па схемы выбора направления передачи возбуждеиия, разрешающие установить в единицу триггеры активности соседних элементов среды, и на схемы «Иц -«Hi4 выбора нанравления передачи настроечной информации, разрещающие передать содержимое регистра сдвига соседпим элементам.

Регистр сдвига, совместно с сигиалом, подаваемым на вход 13, и сигналом с выхода схемы «ИЛИа выполняет функцию выбора направлений. При этом, если хотя бы один из триггеров памяти выбора иаправлений находится в состоянии «единица, тй состояние блока памяти выбора направлений не изменяется; выполняет функцию запоминания кода настройки логического элемента.

Один из возможных алгоритмов настройки вычислительиой среды, построенной на базе предлагаемого элемента, состоит из следующих этапов: 1. Установка ,в нуль триггеров активности; II. Установка в единицу триггера активности элемента, расположенного на внешней стороне вычислительной среды (для этого подается сигнал на один из входов 3- 6); III. Установ:ка в нуль триггеров блока выбора наиравлений (сигналом, подаваемым на вход 2); IV. Установка IB нуль ралистра сдвига (сигналами, поступающими на вход 1); V. Запись кода выбора направлений в регистр сдвига. Этот код последовательно

иоступает на один из входов 14-17 и по сигкалам, подаваемы.м на вход 1, записывается в регистр овига; VI. Передача содержимого регистра сдвига в блок памяти выбора направлений по сигиалу, поступающему на вход 13;

VII. Для выбора второго элемента цепоч-ки выиолняются этапы //-VI и т. д. до тех пор, пока ие будет выбрана требуемая цепочка; VIII. Запись в ролисрр сдвига иервого элемента выбранной цепочки кода настройки логического элемента последнего элемента цепочки; IX. Сдвиг кода иастройки с репистра первого элемента цепочки в регистр второго элемента и запись в регистр первого элемента кода настройки логического элемента последнего элемента цепочки и т. д. до тех пор, пока все логические элементы цепочки не будут настроены на требуемое состояние.

Таким образом, предлагаемый элемент позволяет построить вычислительную среду, в которой настройка ироизводнтся так, что изменяется состояние только тех элементов, у которых возбул ден триггер активности. Кроме того, введение в элемеит блока памяти выбора наиравлений позволяет элементу среды передать код настройки любому из его соседних элементов, что дает возможность производить настройку вычислительной среды как по одной цепочке, так и по нескольким цепочкам параллельно. Доиускается также перестройка отдельных цепочек элементов и построение новых цепочек без разрушения настроенных цепочек элементов. Это позволяет 1зменять состояние регистров сдвига в цепочках элементов, в которых не было отказов, без изменения содержимого блока памяти выбора направлений, т. е. перестроить логическое поле вычислительной среды, не нарущая уже выбранную последовательность настройки эле.ментов. Предлагаемый элемент позволяет также локализовать любую неисправность в вычислительной среде, независимо от расположения отказавших элементов. Все это приводит к повышению эффективности использования вычислительиой среды.

| название | год | авторы | номер документа |

|---|---|---|---|

| ЭЛЕМЕНТ ВЫЧИСЛИТЕЛЬНОЙ СРЕДЫ С ПЕРЕМЕННОЙ СТРУКТУРОЙ НАСТРОЙКИ | 1969 |

|

SU255654A1 |

| ЭЛЕМЕНТ ВЫЧИСЛИТЕЛЬНОЙ СРЕДЫ | 1970 |

|

SU259475A1 |

| ЭЛЕМЕНТ ВЫЧИСЛИТЕЛЬНОЙ СРЕДЫ С ПЕРЕМЕННОЙ СТРУКТУРОЙ НАСТРОЙКИ | 1970 |

|

SU266361A1 |

| ЭЛЕМЕНТ ВЫЧИСЛИТЕЛЬНОЙ СРЕДЫ С ПЕРЕМЕННОЙ СТРУКТУРОЙ НАСТРОЙКИ | 1970 |

|

SU267183A1 |

| ЭЛЕМЕНТ ВЫЧИСЛИТЕЛЬНОЙ СРЕДЫ | 1972 |

|

SU342180A1 |

| ЭЛЕМЕНТ ВЫЧИСЛИТЕЛЬНОЙ СРЕДЫ | 1972 |

|

SU355611A1 |

| ВЫЧИСЛИТЕЛЬНАЯ СРЕДА | 1970 |

|

SU259474A1 |

| Ассоциативный параллельный процессор | 1981 |

|

SU1166128A1 |

| ЭЛЕМЕНТ ВЫЧИСЛИТЕЛЬНОЙ СРЕДЫ С ПЕРЕМЕННОЙ СТРУКТУРОЙ НАСТРОЙКИ | 1971 |

|

SU314203A1 |

| ЦИФРОВОЕ ВЫЧИСЛИТЕЛЬНОЕ УСТРОЙСТВО | 1973 |

|

SU368605A1 |

Даты

1969-01-01—Публикация