Изобретение отнооится к области вычислительной техники и мо-жет быть пр.именено для упра вления очередностью обращения нескольких абон антов к общему ресурсу .в системах реального .масштаба времени. Известно устройство для обработки запросов с контролем их очередности 1, содержащее щ.ифратор, яч-ейки памят,и, входы которых через схемы И подклю1чены к -выходам щи фра тор а, зап.исываЮЩий кольцевой 1счетч:ик и схему ИЛИ. Недостатком устройства является его низкая надежность, обусловленная воЗМОжностью насыщения устройства при увеличении потока заявок от одного (,ил-и нескольких) абонентов, связа.Бного со сбоем или неи1сп.равностью абонента. Пря возникновении насыщения часть заявок те.ряется, а обслуживание лаходящихся в очереди задерживается, что ирнводит к уста|реванию деформации и уп1р.а1вляющих воздействий. Пр;и этом управляющая система практически перестает выполнять свои функции. Известно устройство для обслуживания запросов в порядке их поступления 2, содержащее регистры, триггеры занятости, считььвающие элементы И и гасящие элементы И, причем нулевые входы триггеров залятостл соединены с выходами соответствующих гасящнх элементов PI, первые входы котО|рых подключены ко входу гащения. Единичные выходы триггеров занятости соединены с первым аходальи соответствующих считывающих элементов И, . вторые входы которых подключены к раз;решающему входу устройства. Недостатком устройства является его низкая надежность, обусловленная .возможностью хранения в очереди двух и более одноименных запросаз, что приводит к насыщению оистемы прерывания ,;управляющей системы. Известно .многоканальное устройство для организащги очереди {3, содержащее реверошвный счетчик, элемент ИЛИ, , а, в каждом канале-триггер и элемент И, .первые входы которого соединены с выходом триггера. При поступлени.и заявки в счетчик каждого .канала записывается об.ратный код числа, содержащегося в реверсивном счетчике. Код в реверсивном счетчике увеличив-ается на един.ицу с поступлением каждой заявки и уменьщается .пр.и посту.плен;и.и на устройство сигнала о выполнении очередной заявки. Сигналом выполнения очередной заявки прибавляется единица к счетчика1М каналов, в которых хранятся заявки,

ожидающие обслуживания. Заявка лоступает на ОбслуЖ|И,ва.ние в момент появления сигнала переноса iB одном из счетчиков каналов. Устройство позволяет обслуж)ивать поступающие заявки по принципу «первЫ|М пришел - inepiBbiM обслужился.

Недостатком усиройства является низкая надежность, обусловленная тем, что ври одновременном ло-ступлении запросов по двум :ка налам в счетчики обоих «аналов заоишется одинаковый ;код, оба счетчика одновременно сфор мируют требование ла обсл:у к ива,ние, в результате чего управляющая яычислительЕая (машина перейдет на иесущест1вующую трограм/му и начнет выдавать на абоненты ложные управляющие воздействия, т. е. вся управляющ:ая система перестанет выполнять свои фун:кци1и.

Аналогичное искажение хода управляющего процесса возникает при одно:временHOiM поступлении внещнего запроса и выдачл сигнала завершения обслуживания оче(редной заявки.

Известно многоканальное устройство для управления 0 черадностью обработки запросов 4, содер/кащее счетчик, элемент задержки, инвертор, элементы И и ИЛИ, а в каждам канале-триггер.

Недостатком устройства является низкая надежность, связанная с возможностью нахождения в очереди двух и более одноименных запросов, что -ведет к насыщению Зстройства.

Низкая надежность успройства обусловлена та.кже тем, что пфи одновременном поступлении двух разных запросов может быть Произведен их одновременный прием (т. е. IB регИСтры двух каналов запищется один и тот же код счетчика), что приведет к одновременно му опросу двух разных источников инфо|рмации :и, следовательно, к выдаче в уп«ра1вляющую вычислительную машину неправильной К01.ман1ды перехода.

Наиболее близким к изобретению по технической сзщности и достигавмо1му эффекту является многоканальное устройство для обс луживания запросов 5, содержащее шифратор, схему выявления разрешенных прерываний, регистр защиты, элемент ИЛИ, элемент НЕ, два элемента задержки, а в каждом канале - два т риггера, четыре элемента И ,и два элемента НЕ.

Недостатком устройства является его низкая наделсность, обусловленная невозможностью хранения в очереди более одного запроса, что 1может привести :к потере запросов.

Цель изобретения - повышение надежности.

Поставленная цель достигается тем, что в .многоканальное устройство для обслуживания запросов, содержащее шифратор, элемент ИЛИ, элемент НЕ и элемент задерж1КИ, -а ;в каждам канале - два т риггера и три элемента И, причем выход первого

триггера канала соединен с первым входом первого элемента И .канала, запросные входы устройства соединены со вторыми входами первых элементов И каналов, первые входы вторых элементов И каналов соединены с выходом элемента задержки, выход третьего элемента И .канала соедкнен со вторым входо.м второго элемента И канала, выходы первого и второго элементов И канала соединены со входами второго триггера канала, выходы третьих элементов И .каналов соединены со входами шифратора, а первый управляющий вход устройства соединен со входом элемента НЕ введены группа репистрав, .два дешифратора, реверсивный счетчнк, триггеры блокировки и синхронизации и фиКсирующий элемент И. Выходы шифратора соединены с первой группой входов регистров. Выходы регистра сое.динены со второй группой .входов после.дующего рег.истра, .а выходы последнего репистра - с информационными входами первого дешифратора и с группой выходов Зстройства. Выходы первого дешифратора

соеди нены с первыми входаМ1и первых триггеров .ка.налов. Выходы .-вторых триггеров каналов через элемент И соединены со входом эле.ме1нта задержки, с сум мирующим в.ходо.м реверсивного счетчика и с -правляющим входом второго дешифратора, зыходы .которого соединены с управляющи.ми щхода.ми регист ров. Тактовые входы регистров и юыч.итающий вход реверсивного счетчйка соединены с прЯ1МЫ1М выходом трлггера синхр.онизащии, .инверсный выход .которого соединен с управляющим входом первого дешифратора .и с первым .входом фиксирующего эле.мента И, .второй вход « выход которого соединены соответственно с

призна.ковькм выходом последнего репистра и .с .выходом .устройства, второй и третий управляющие входы устройства соединены соответственно с .первьв.м .и вторым уста.ноВОЧНЫ1МИ входами тр.иггера си-нхро.низации,

первый и второй гасящие входы которого соединены с четвертьпм управляющим входом устройства. Выход элемента задержки соединен с гасящим входом триггера блокировки, устано1вочный вход и инверсный

1ВЫХОД которого соединены соответственно с первьим управляющим входом устройства « с нервЫ|М.и входами т ретыих элементов И каналов. Вторые входы третьих элементов И кана.лов соединены с выходом элемента НЕ.

Третий вход третьего элемента И канала соединен с выход;0.м второго тр.йггера ,ка.нала, выход - с четвертым входом третьего элемента И последующего .канала, а .выход второго триггера канала - со вторым входом первого тр1иггера канала.

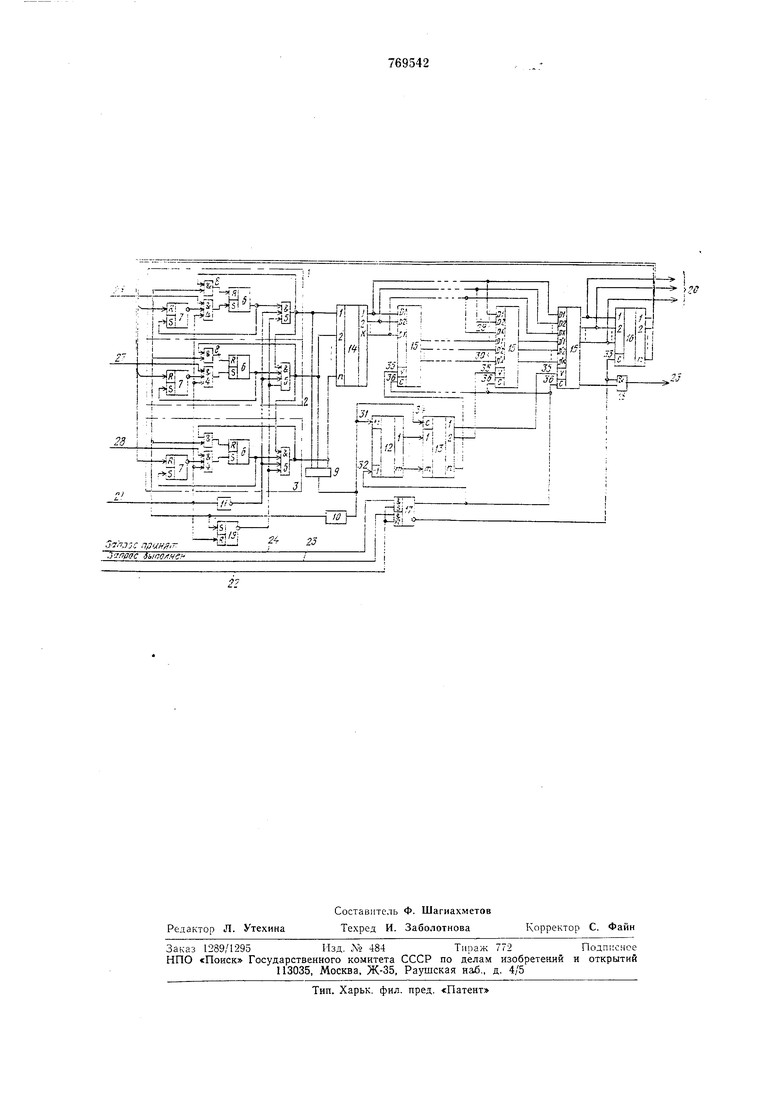

Стр.уктурная схема устройства представлена на чертеже.

Многоканальное устройство для обслуживания запросов содержит 1каналы 1-3,

каждый из которых содержит элементы И 4, 5, второй триггер 6, первый триггер 7 я эле;М1енть1 И 8. Кроме того, устройство содержит элементы ИЛИ 9, элемент задержки 10, элемент НЕ 11, реверсивный счетчик 12, второй дешифратор 13, шифратор 14, группу регистров ,15, первый дешифратор 16, триггер 17 синхро;н,иза|ц;ии, фикоирующий элемент И 18, триггер 19 блокировки, выходы 20, первый управля1ош,ий вход 21, четвертый 22, третий 23 я иторой 24 управляющдае входы, .выход 25, запросные входы 26-28. На чертеже приняты следу1ош,ие обозначения: 29, 30 - соот1ветствен но первая и вто(рая группы входов регистра, 31, 32 - су1М.МИрующпй и |ВЫчитаюш,ие входы реверсивного счетчика, 33, 34 - упра;вляк пхие входы соответственно первого и второго дешифраторов, 35 - управля1ош.ие входы регистров, 36 - тактовые входы регистров. Рассмотрим работу устройства при поступлении внешних запросов одновременно ;на входы 26, 27 и, с некоторой задержкой- на вход 2S. В ИСХОДНОМ состоянии все регистры 15 и все триггеры устройства установлены в иулевое состояние. Работа устройства синх,ронизируется двумя .И1мпульсны1ми последовательностями, сдви;нуты1м,и одна относительно другой на половину периода и поступающими .на устройство по входу 21 («Такты записи) и по входу 22 («Такты считывания). Пусть внешние запросы поступают на выходы 26, 27. Прием виешлих запросов в триггефы 6 праизводится через элемент И 4 iBO вре;мя действия такта записи. В это же время через эле.мент НЕ // яа элембнтах И 5 блокируется тарохождение принятых запросов на выход соответствующего ка.нал.а. Выход}1Ы|М потенциалом с триггеров 6 устанавливаются в единичное состояние триггеры 7 каналов /, 2. Выходными потенциалами триггеров 7 на первых в.ходах эле ментов И 4 блокируется прием внешиих запросов в каналы /, 2. Одновременно ;оигиал с выхода триггеров 6 поступает на третьи входы элементов И 5. На элементах И 5 собран-а схема приоритета, предназначенная для разделения во времени одновременно поступи.вших iHa устройство внешних запросов, причем уровень приоритета уменьшается с увеличением .номера канала. Это обес.печивается блокировкой э.лемента И 5 ,каждого последующего канала с выхода элемента И 5 предыдущего. По окончатии действия такта зап.и;ои (когда .на выходе элемента НЕ 11 уста.но1вится разрешаюший уровень потенциала) сипнал ic выхода элемента И 5 канала 1 поступает на вход :шифратора 14, на выходе которого формируется код команды первого запроса, и через элемент ИЛИ 9 - на 1ВХОД 3d реверсивного счетчика 12. Сипнал, поступающий .на «вход 1, должен быть укорочея по .переднему ронту на велпч-ину, определяемую максиальным в:реме.нем распространения сипнаа блокировки с аыхода элемента И 5 каала / до четвертого входа элемента .И 5 канала 3. Этим сигналам про1и31ВО1Дится р Ибавление к реверСИВ(НОму счетчику 12 единицы и через элемент задержки 10, время задержки которого .равно cyiMMe времеи Срабатывания счетчика 12, времени срабатывания дешифратора 13 и в,ремени записи в регистр 15, у.станавли1вается в единичное состояние триггер 19 бло.к.ировк)и (установка его в .нулевое состояние производится тактам1И записи), .запреща я пря этом на элементе И 5 канала 2 в текущем цикле записи про.хождение на :кодированне запроса с выхода ка.нала 2. Одновременно сигналом с выхода элемента задержки 10 сбрасывается триггер 6 канала 1. Сброс обеспечивается наличием разрешающего потенциала на втором выходе второго- эле мeнтa И 8. Сигнал, поступающий на вход 34 дешифратора 13, должен быть укорочен ло переднему и заднему фронтам ,на .величину, превышающую время срабатыван ия счетчика 12. На .инфор;мацио.нные входы дешифратора 13 с выхода счетчик.а 12 поступает код адреса первого регистра 15. Выходным сигналом с дешифратора 13 прОИззодится запись ,кода внешнего запроса с выхода шифратора 14 в /(-1 разряды первого регистра 15. В УС-й разряд этого регистра запи.сы.вается еди.иица, которая определяет .наличие кода в регистре. После приема кода в первый регистр 15 на группе ВЫХОДОВ 20 устройства .и на выходе 25 появляются соответственно код команды и признак команды пере.хода, поступающие В ЦВМ. Дешифратор 16 расшлфровывает но,мер опроса (в рассматриваемом случае «первый), .и сигналом с его первого выхода устанавливается в нулевое состояние Т1риггер 7 канала /. После поступления очередного таКта записи сбрасывается в .нулевое состояние триггер 19 блокировки, и по окончана и такта заПИси появляется сигнал на вы.чоде эле.мента И 5 ка.нала 2. Кодирование и установка в очередь (запись ВО второй регист.р 15) запроса, принятого а .ка.нал 2, .производится а.налогично описанному выше. Во время .кодирования и зап..иси второго запроса по входу 24 поступает управляющий сигнал «Запрос принят, определяющий принятие на :выполнен1ие в ЦВ.М первого запроса. Сигнал «Запрос принят, тростробирован.ный тактом Считывания, устанавливает триггер 17 СИ1Нхрон|Изап,ии в ед1И.нич.НОе СО|СтоЯ|Вие. П.ри этом потенциалом с его нулевого выхода блокируется выход дешифратора 16 и на фиксирующем элементе И 18 блокируется выдача приэна-ка жома.нды перехода. Сигналом с единичного плеча триггера 17 обеспечивается сдвиг содержимого регистров 15 вшраво, т. е. содержимое второго регистра ,/5 переписывается ъ первый, содержимое Т1ретьего регистра - во второй и т. д.

Одновремйнно производится -вычитание единицы из содержимого счетчика 12. Та.мим- образом, :в -первом регистре -15 оказывается код второго запроса. Прием, а о|дирование и заллсв запроса, постулгиишего ,на вход калала 3, производятся а.налогйчио первым двум. При это.м код претьего запроса записывается во второй регистр 16.

По окоичаняи программы, выполнявмой по парвоаму запросу, по входу 23 поступает оипнал «Запрос выполнен, который, будучя простробировап тактом Считываяля, устанаШпивает тр иггер 17 синхродизацяя в .нулевое состояние. Пр.и этом ic выхода элемента И ,18 выдается признак команды, по которому осуществляется прием в ЦВМ с выхода регистра 15 команды перехода. Одтновременно сигналом со второго выхода дешифратора 16 устанавливается в нулевое состояние триггер 7 :канала 2. После поступления из ЦВМ сигнала «Запрос принят на элементе И 18 блокируется выдача в ЦВМ признака .команды перехода, осуществляется сдвиг информаадии в регистрах 15 на один регистр вправо ,и вы1Ч1итапие единицы ,из содержимого счетчИКа 12.

Прием внешнего запроса, -его кодированяе и установка в очередь осуществляются за половину периода тактов зап1иси, т. е. до прихода очередного такта считывания. Этим исключается В|0змож ность искажения информации в устройстве при одновременном поступлемим внешнего запроса и силналов «Запрос принят иди «Запрос выполнен из ЦВМ, т. е. исключается сдвиг регистров в момент записи в ,кода запроса с выхода щифратара 14.

Таким о бразом, .введение новых элементов св уст|ройство повышает надежность его работы за счет возможности хранения более чем одного запроса, т. е. исключения потери запросов.

Ф о р м л а и 3 о б р е т е н ,и я

Многоканальное устройство для обслуживаняя запросов, содержащее шифратор, элемент ИЛИ, элемент НЕ и элемент задерж:ки, а в каждом канале - два триггера п три элемента И, причем выход первого триггера канала соединен с первым входом первого элемента И канала, запросные 1ВХОДЫ устройства соединены со вторыми входами первых элементов И каналов, первые входы вторых элементов И .каналов соединены с выходом элемента задержки, выход третьего элемента И канала соединен со вторым входо.м второго элемента PI канала, выходы первого и вто.рого элеме.нтов PI канала соединены со входам.н второго триггера канала, выходы третыих элементов

И каналов соединены со входами ш.ифр.атора, а первый управляющий вход устройства соединен со входом элемента НЕ, о тлячающееся тем, что, с делью новыщевия .надежности, оно содерж1ит группу регистров, два дещифратор.а, реверсивный счетчик, тр.иггары бло.к1ировКИ я синхро/яизащии и фикаирующий элемент И, выходы шифратора соединены с первой группой входов регистров, .выходы 1регистра .соединены со второй группой входов последующего регистра, выходы 1последнего регистра .со-единены с информационными входами .первого дешифратора и с группой выходоа устройства, выходы первого дещифратора соеди.нены с первьгми входами первых триггеров каналов, выходы вторых триггеров .каналов через элемент И соединены со входом эле.мента задержки, с .Иру1Ощим входам реверсивного .счетчика и с управляющим входом второго дешифратора, выходы :которого соединены с управляюнли-м.и входами регистров, тактовые входы регистров и вы1читающий 1ВХО.Д .реверснвого счетчика соединены с прямым выходом триггера синхронизации, инвер.аный выход которого соединен с управляющим входом первого дешифратора и с первьим входам фиксирующего элемента И, второй вход .и выход которого соединены соответственно с признаковым выхо.дам последнего регистра я с выходом устройства, второй и третий управляющие входы устройства соединены соответственно с первым и вторым установоч/ными входами триггера синхранизации, .первый и второй гасящие входы которого .соединены с четвертым управляющим входом устройства, выход элемента за.держки соединен с гасящим входо.м триггера |блокиро.вки, установочный вход и инверсный выход которого соединены соответственно с первым управляющим входом устройства и с первыми входами третьих элементов И каналов, вторые входы третьих элементов И каналов соединены с выходом элемента НЕ, третий вход третьего элемента И канала соединен с выходом второго триггера канала, выход третьего элемента И канала соединен с четвертым входом третьего элемента И последующего канала, а выход второго триггера канала соединен со вторым входом первого триггера канала.

Источники информации, принятые во внимание при экспертизе:

1.Авторское свидетельство СССР Ло Э50005, кл. G 06 F 15/46, 1972.

2.Авторское свидетельство СССР 522500, кл. G 06 F 9/18, 1976.

3.Авторское св1идетельство СССР № 561186, кл. G 06 F 9/00, 1977.

4.Авторское свидетельство СССР ЛЬ 496558, кл. G 06 F 15/46, 1972.

5.Авторское свидетельство СССР № 439812, кл. G 06 F 9/18, 1972 (прототип).

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для обмена информацией между цифровой вычислительной машиной и внешними устройствами | 1981 |

|

SU1003066A1 |

| Устройство для обмена информацией | 1982 |

|

SU1048468A1 |

| Устройство для обмена информацией между цифровой вычислительной машиной и внешними устройствами | 1982 |

|

SU1062681A2 |

| Устройство для обмена информацией между ЦВМ и внешними устройствами | 1980 |

|

SU907537A1 |

| Устройство для сопряжения цифровой вычислительной машины с каналом связи | 1991 |

|

SU1837301A1 |

| УСТРОЙСТВО ДЛЯ СОПРЯЖЕНИЯ ВЫЧИСЛИТЕЛЬНОЙ МАШИНЫ С КАНАЛАМИ СВЯЗИ | 1990 |

|

RU2020565C1 |

| Имитатор абонентов | 1983 |

|

SU1291987A1 |

| Устройство для ввода информации | 1982 |

|

SU1130854A1 |

| УСТРОЙСТВО ДЛЯ СОПРЯЖЕНИЯ ЦВМ С КАНАЛОМ СВЯЗИ | 1991 |

|

RU2011217C1 |

| Аналого-цифровая вычислительная система и аналоговая вычислительная машина (ее варианты) | 1983 |

|

SU1259300A1 |

Авторы

Даты

1980-10-07—Публикация

1978-07-07—Подача