(54) БУФЕРНОЕ ЗАПОМИНАЮЩЕЕ УСТРОЙСТВО

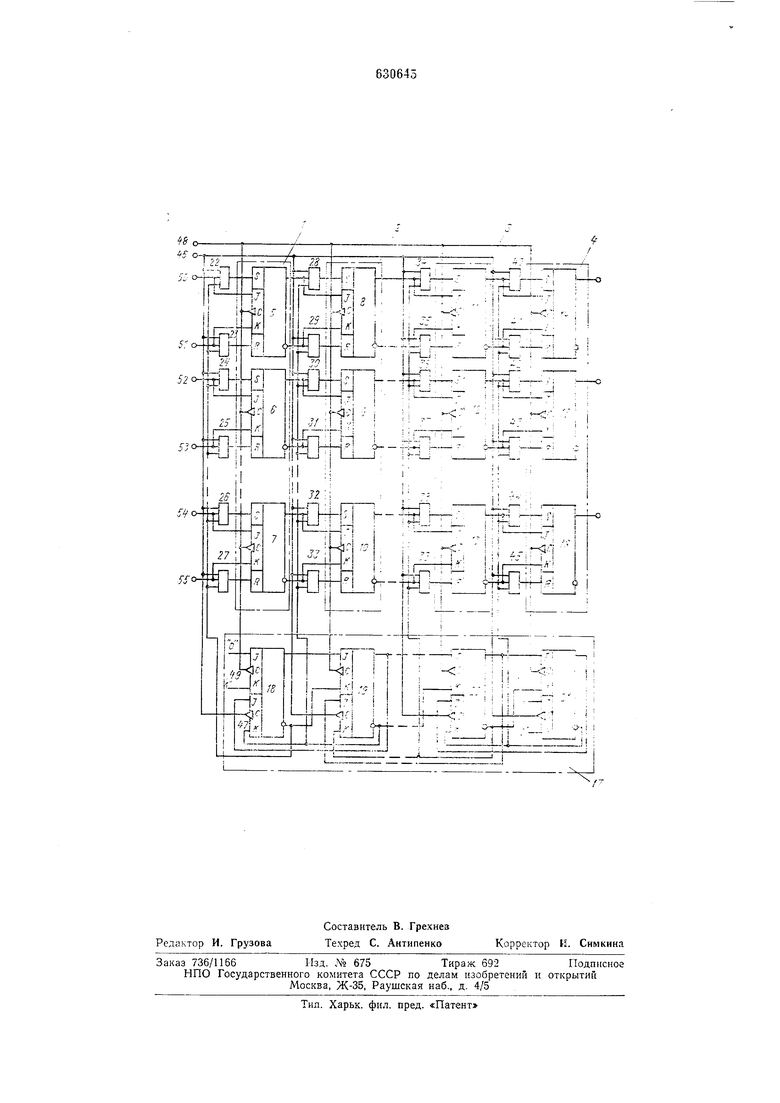

сдвига влево регистра 17, та ктнруемые входы perHCTpOiB /-4 тодключены К шине 48 считывания и к входу 49 сдвига регистра /7.

Работает устройство следующим образом.

В исходном положении все триггеры 18-21 управляющего регистра П находятся IB Нулевом состоянии. Триггеры 5-16 регистров I-4 хранения чисел могут находиться в любом состоянии. Поступающий на шину 46 записи имиульс затиси информащии опрашивает (все элементы И 22-45 устройства. Поскольку триггеры /S-21 управляющего регистра 17 в нулевом состоянии, то все эламенты И открыты и первое слово с ВХОДНЫХ информационных шин 50-55 inepвписывается IB регистр 1 хране«ия информации (в трилгеры 5, 6, 7). Элементы И 28-33 также открыты, лоэтому «слово переписывается далее в регистр 2 (з триггеры 5, 9, 10), затем в регистр 3 и далее В регистр 4.

Та-ким образом, одним импульсо.м записи информация сразу же записывается в регистр 4. По заднему фронту импульса записи происходит сдвиг влево IB управляющем регистре 17. Так как «а ;вход / тр.иггера 21 постоянно ;подан с 1гнал, равный логической единице, а на вход К - сигнал, равный логичеокаму нулю, то триггер 21 уста-навливается в единичное состояние и сигналом, равным логическому нулю, с нулевого выхода закрывает эл-аменты И 40-45. Поэтому приход второго импульса записи последнего разряда управляющего регистра 17 свидетелыствует о том, что информации в

буферном запоминающем устройстве нет и считывание производить не следует.

Поскольку в предлагаемОМ устройстве не требуется п дополнительных такто.вых Ичмпульсав для упорядочения информации, отпадает необходимость :в до;поЛНительном генераторе синхросерий и надежность его повыщается.

Формула изобретения

Буферное :за1поминающее устройство, содержащее регистры };ранения чисел, управляющий реверсивный регистр сдвига, элементы И, ШИ1НЫ датиси и считывания, отличающееся тем, что, с Целью товышения надежности устройства, в нем выходы разрядов каждого регистра хранения чисел соединены с входами одноименных разрядов тоследующето регистра хранения чисел через эламенты И, которые соединены с щиной записи и с 1входом сдвига влево управляющего реверсивного регистра сдвига, тактируемые входы регистров хранения

чисел соединены с щиной считывания и с входом сдвига вправо управляющего реверсивного регистра сдвига, выходы которого соединены с управляющими входами элементов И.

Источники информации, принятые во внимание при экспертизе:

1. Авторское свидетельство СССР Л 407396, ,кл. G 11 С 19/00, 1972. 2. Заянка ,Д1 2323403/18-24, кл. G 11 С 19/00, 13.02.76, по которой принято решение о выдаче авторского (свидетельства.

So

S C-:

| название | год | авторы | номер документа |

|---|---|---|---|

| Буферное запоминающее устройство | 1978 |

|

SU750568A1 |

| Буферное запоминающее устройство | 1977 |

|

SU739645A1 |

| Буферное запоминающее устройство | 1978 |

|

SU746720A1 |

| ВЫЧИСЛИТЕЛЬНАЯ ОТКРЫТАЯ РАЗВИВАЕМАЯ АСИНХРОННАЯ МОДУЛЬНАЯ СИСТЕМА | 2009 |

|

RU2453910C2 |

| Запоминающее устройство | 1979 |

|

SU842967A1 |

| БУФЕРНОЕ ЗАПОМИНАЮЩЕЕ УСТРОЙСТВО | 1972 |

|

SU407396A1 |

| ВЫЧИСЛИТЕЛЬНОЕ УСТРОЙСТВО | 1969 |

|

SU255993A1 |

| Запоминающее устройство | 1973 |

|

SU496604A1 |

| Долговременное запоминающее устройство | 1979 |

|

SU847371A1 |

| Постоянное запоминающее устройство | 1979 |

|

SU849303A1 |

Авторы

Даты

1978-10-30—Публикация

1976-12-16—Подача