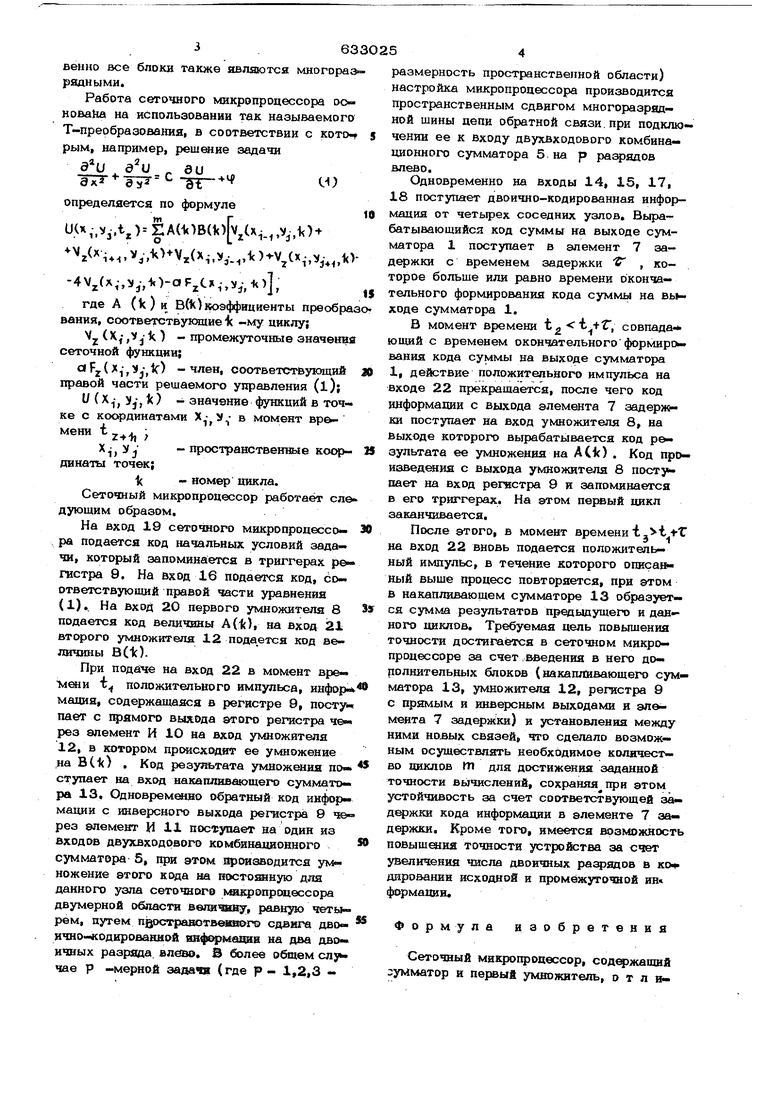

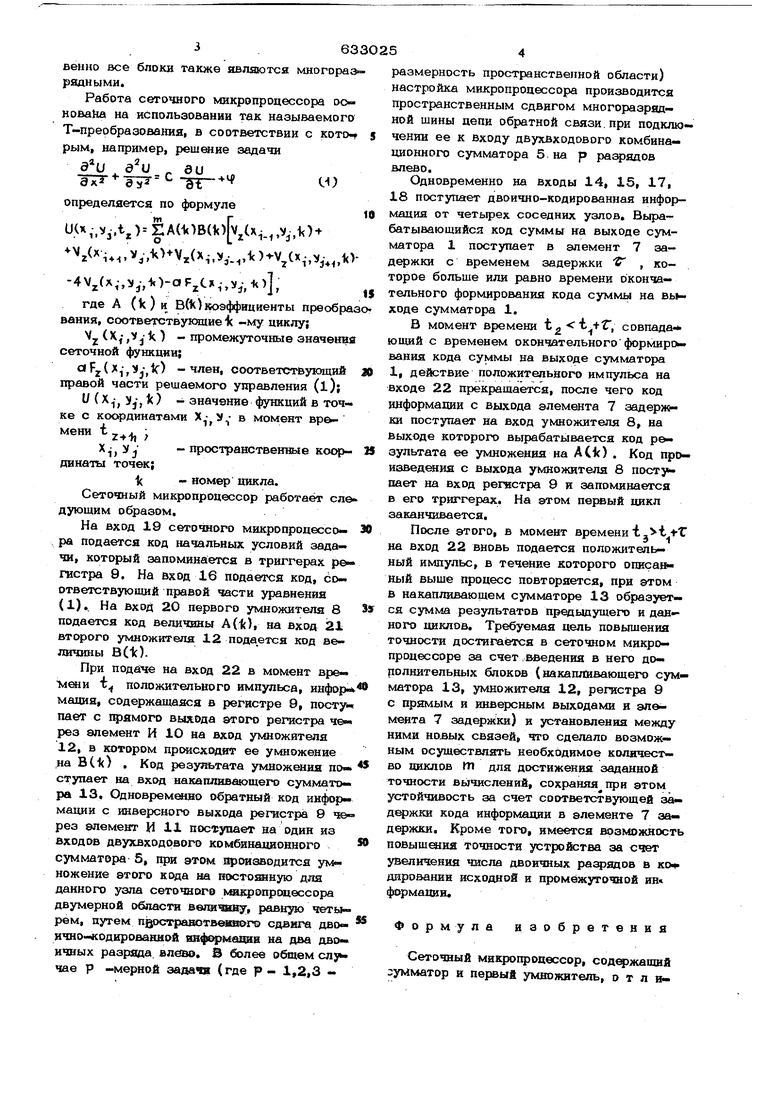

Изобретение относится к аналоговой вычислительной технике, в частности к электрическому моделированию. Известна модель сеточной области, используемая в устройстве для решения заД1Ч теплопроводности ij, содержащая блок ввода, регистр,сумматор и блок умножения. Наиболее близким техническим решением к данному изобретению является сеточный- микропроцессор 2, содержаший сумматор, первый умножитель, цифровой интегратор п инвертор. Известные устройства не обеспечивают необходимую точность. Цель изобретения - повышение точности. Это достигается тем, что сеточный микропроцессор содержит элемент задер)ки,второй умножитель, элементы И, регистр и накапливающий сумматор, вход KCN торого подключен к выходу второго умнсь жителя, вход которого соединен с выходом первого элемента И, первый вход которого подключен к управляющей шине, вт рой вход первого элемента И соединен с прямым выходом регистра, Ш1версный выход которого подключен к первому входу второго элемента И, второй вход которого соединен с управл5пощей шиной, выход второго элемента И подключен к одному входу сумматора, другие входы которого являются входами сеточного микропроцессора, выход сумматора через элемент задержки подключен ко входу первого умножителя, выход которого соединен с информационным входом регистра. На чертеже показана блок-схема сеточного микропроцессора. Сеточный микропроцессор содержит сумматор 1, состоящий из двухвходовых комбинационных сумматоров 2-6, элемент 7 задержки, первый умножитель 8, р&гнстр 9 (типа RS) с прямым и инверсным выходами, элементы И 10 и 11, второй умножитель 12, накапливающий сумматор 13, Позициями 14-18 обозначены входы сеточного микропроцессора. Все связи на чертеже, обозначенные стрелками, многоразрядные, и соответственно все блоки также являются многоразрядными. Работа сеточного микропроцессора ос кобаНа на использовании так называемого Т-преобрааования, в соответствии с котоп рым, например, решед1ие задачи аи 5Топределяется по формуле U(x,,V3.t,|:AU)B(1)Vj,U.,V,,,1) .,,(x-.,..,1c)-.V(x.,,., -4V(x-,,-,),-,i), где А (k) н B(ii)коэффициенты преобраз вания, соответствукяцие i: -му циклу; У- ( Х(,V - 1с ) - промежуточные значения сеточной функции; а F., {X ,, 5 VА - член, соответствующий J / правой части решаемого управления (1J; и (К,У:) - значение функций в точке с координатами в момент вр&мени t Xjj :y.j-пространственные KOf динаты точек; |( - номер цикла. Сеточный микропроцессор работает еле дующим образом. На вход 19 сеточиого микропродессо- ра подается код начальных условий задачи, который запоминается в триггерах ре гистра 9. На вход 16 подается код, соответствующий правой части уравнения (1)., На вход 20 первого умножителя 8 подается код величзаны А{(), на вход 21 второго умножителя 12 подается код величины В(1(). При подале на вход 22 в момент времени t положительного импульса, инфор мания, содержащаяся в регистре 9, поступает с 1ФЯМОГО выяода этого регистра че«« рез элемент И 10 на вход умножителя 12, в котором прсжсходит ее умножение на В(1) , Код результата умножения по- ступает на вход накапливающего сумматора 13, Одновременно обратный код инфор мации с инверсного выхода решстра 9 через элемент И 11 поступает на один из входов двухвходрвого комбинационного сумматора 5, гфи этом а оизводится умножение этого кода на несто ную для данного узла сеточного ьшкропрещессора двумерной обпасга , равную четырем, путем пзостравотвеш го сдвига дво«ично-кодированвой нвфсфмвцив на два двоичных разряда, влбво, В лее общем сл; чае р -мерной задачи (где р - 1,2,3 размерность пространственной области) настройка микропроцессора производится пространственным сдвигом многоразрядной шины цепи обратной связи.при подключении ее к входу двухвходового комбинационного сумматора 5 на р влево. Одновременно на входы 14, 15, 17, 18 поступает двоично-кодированная информация от четырех соседних узлов. Вырабатывающийся код суммы на выходе сумматора 1 поступает в элемент 7 с временем задержки У , которое больше или равно времени окончательного формирования кода суммы на вььходе сумматора 1. В момент времени . совпада- ющий с временем окончательногоформирования кода суммы на выходе сумматора 1, действие положительного импульса на входе 22 прекращается, после чего код информации с выхода элемента 7 задерг ки поступает на вход умножителя 8, на выходе которого вырабатывается код результата ее умножения на A(i() . Код извед«1ия с выхода умножителя 8 поступает на вход регистра 9 и запоминается в его триггерах. На этом первый цикл заканчивается. После этого, в момент времени на вход 22 вновь подается положительный импульс, в течение которого описаэный выше процесс повторяется, при этом в накапливающем сумматоре 13 образуется сумма результатов предыдущего и данного циклов. Требуемая цель повышения точности достигается в сеточном микропроцессоре за счет.ведения в него до- ролнительных блоков (накапливающего сумматора 13, умножителя 12, регистра 9 с прямым и инвержным выходами я элемента 7 задержки) и установления между ними новых связей, что сделало возможным осуществлять необходимое количество циклов m для достижения заданной точности вычислений, сохраняя при этом устойчивость за счет соответствующей за- кода информации в элементе 7 задержки. Кроме того, имеется юзможность повышшия точности устройства за счет увеличения числа двоичных в коч дированин исходной и промежуточной ин« формации Формула изобретения Сеточный микропроцессор, содержащий сумматор и первый умножитель, о т л н

| название | год | авторы | номер документа |

|---|---|---|---|

| Контроллер измерительного преобразователя | 1988 |

|

SU1541632A1 |

| Устройство для преобразования по функциям Уолша | 1983 |

|

SU1137479A1 |

| Цифровой коррелятор | 2020 |

|

RU2735488C1 |

| Преобразователь код-напряжение | 1984 |

|

SU1197084A1 |

| Устройство для моделирования динамических процессов | 1990 |

|

SU1817107A1 |

| Устройство для обнаружения и исправления ошибок в кодовой последовательности | 1984 |

|

SU1238078A1 |

| Вычислительное устройство | 1988 |

|

SU1532917A1 |

| Устройство для формирования информативных признаков при распознавании изображений | 1986 |

|

SU1361591A1 |

| УСТРОЙСТВО УМНОЖЕНИЯ | 1998 |

|

RU2148270C1 |

| УСТРОЙСТВО ФОРМИРОВАНИЯ ЛИНЕЙНО-ЧАСТОТНО-МОДУЛИРОВАННОГО СИГНАЛА | 1996 |

|

RU2110145C1 |

Авторы

Даты

1978-11-15—Публикация

1977-06-10—Подача