1

Изобретение относится к информацион-но-измерительной технике, в частности к измерительным преобразователям цифрового слова в аналоговый выходной сигнал.

Целью изобретения является повышение надежности и точности преобра.зователя код-,напряжение путем упрощения устройства и расширения диапазона компенсации погрешностей, обусловленных изменением элементов схе.мы.

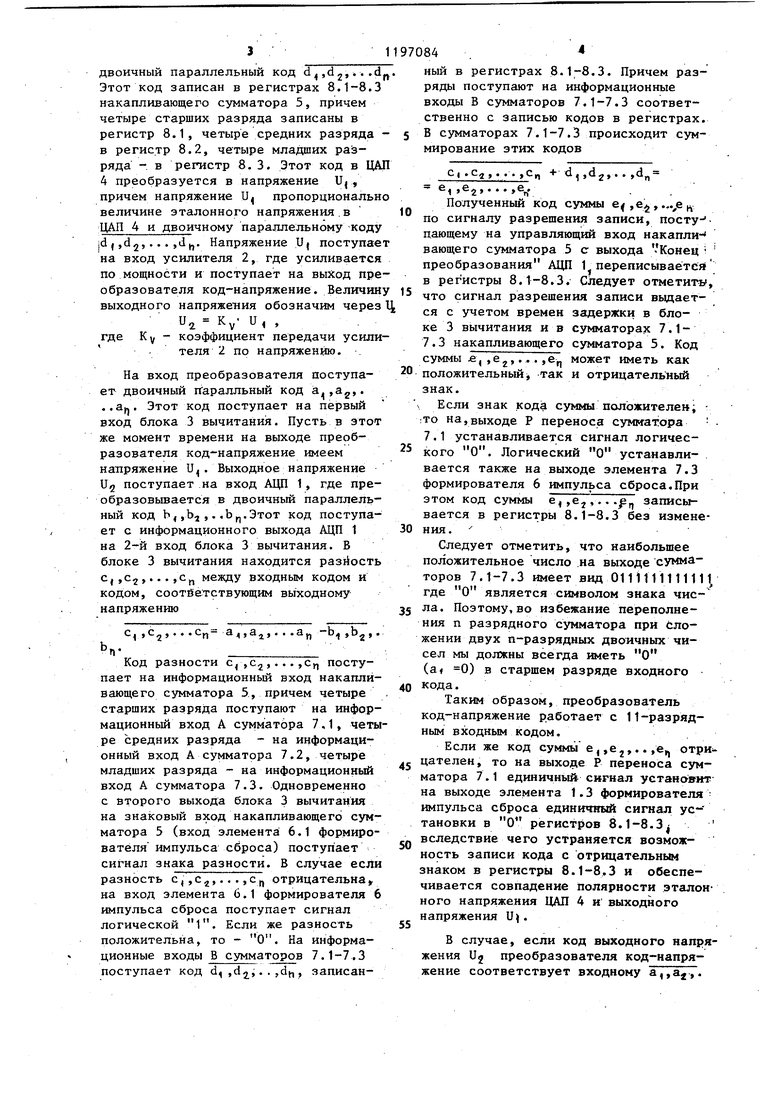

На чертеже представлена функциональная схема предлагаемого преобразователя.

Устройство содержит аналого-цифровой преобразователь (АЦП) 1, усилитель 2, блок 3 вычитания, цифроаналоговый )еобразователь (ЦАП) 4, накапливающий сумматор 5. .

Выход ЦАП 4 через усилитель 2,выход которого является выходной шиной,соединен с входом АЦП 1. Первые выходы АЦП 1 подключены к первым входам блока 3 вычитания, вторые входы которого являются шинами входного кода.

Накапливающий сумматор 5 содержи формирователь 6 импульсов сброса, последовательно соединенные сумматоры 7 комбинационного типа и регистры 8. Выходы регистров соединены с входами ЦАП и с вторыми входами сумматоров 7 комбинационного типа, третьи входы которых подключены к соответствующим первым выходам блока 3 вычитания. Второй выход блока 3 вычитания подключен к первому входу формирователя 6 импульсов сброса, второй вход которого соединен с выходом переноса сумматора 7 комбинационного типа старших разрядов . Выход формирователя 6 подключе к входу установки в О регистров 8,входы разрешения записи которых соединены с вторым выходом АЦП 1. Информационные входы регистров 8 подключены к соответствующим выходам сумматоров 7 комбинационного типа. Первый вход (переноса) сумматора 7.3 комбинационного типа младших разрядов соединен с шиной нулевго потенциала. Третий вход формирователя 6 импульса сброса Соединен с шиной постоянного потенциала.

Преобразователь код-напряжение работает следующим образом.

7084 . . 2

Входной параллельный двоичный код поступает на второй вход блока 3 вычитания, на первый вход, которой с выхода АЦП поступает код, соответствующий величине выходного напряжения. .

С второго выхода блока 3 вычитания цифровой код, представляющий собой разность этих двух кодов, поступает на третьи (информационные) входы накапливающего сумматора 5. На второй (знаковый) вход накапливающего сумматора 5 подается сигнал знака разности с первого выхода блока 3 вычитания, а на первый (.управляющий} вход накапливающего сумматора 5 поступает сигнал Конец преобразования с второго выхода АЦП 1. Код разности поступает на инфор-

0 мационные входы А малоразрядных сумматоров 7.1 - 7.3 накапливающего сумматора 5. На информационные входы В данных сумматоров 7.1-7.3 поступает код с выходов параллельных

5 регистров 8.1-8.3. На второй вход элемента 6.3 в формирователе 6 .через элементы 6.1 и 6.2 подается сигнал знака разности. С выходов сумматоров |7.2-7.3 полученный код суммы поступад ет на информационные входы D трех параллельных регистров 8.1-8.3. Запись кода суммы в регистры в случае ее положительного знака происходит по управляющему сигналу Конец преобразования,, поступающему do второго вы хода АЦП 1. При этом на выходе переноса старших разрядов устанавливается сигнал логический Q.

Если код суммы становится отрицательным, то единичный сигнал на выходе переноса старших разрядов с сумматора 7.1 установит на выходе формирователя 6 импульса сброса, выполненного, например на трех двухвходовых элементах ИСКЛЮЧАЮЩЕЕ ИЛИ на, капливающегд сумматора 5, единичный сигнал установки в О регистров 8.1-8.3. При этом на выходе данных регистров устанавливаются логические О.В ЦАП4 цифровой код преобразуется в напряжение, соответствующее коду на входе ЦАП 4. Выходное напряжение ЦАП 4 усиленное по мощности усилителем 2, поступает на выход устройства и одновременно на вход АЦП 1.

5 Рассмотрим один цикл работы преобразователя код-напряжение.

Допустип, в каком-то момент времени на вход ЦАП 4 поступает разрядный двоичный параллельный код d jdg, .d Этот код записан в регистрах 8.1-8.3 накапливающего сумматора 5, причем четыре старших разряда записаны в регистр 8.1, четыре средних разряда в регистр 8.2, четыре младших разряда - в регистр 8. 3. Этот код в ЦА 4 преобразуется в напряжение Uj, причем напряжение U пропорциональн величине эталонного напряжения.в ЦАП 4 и двоичному параллельному коду jd , ,d2,... ,tif,. Напряжение и( поступае на вход усилителя 2, где усиливается по мощности и поступает на выход пре образователя код-напряжение. Величин выходного напряжения обозначим через KV и, , где Ку - коэффициент передачи усили . теля 2 по напряжению. . На вход преобразователя поступает двоичный паралльный код &,а.у,. ... Этот код поступает на первый вход блока 3 вычитания. Пусть в этот же момент времени на выходе преобразователя код-напряжение имеем напряжение U. Выходное напряжение и поступает на вход АЦП 1, где преобразовьшается в двоичный параллельный код Ь, ,5,..Ь.Этот код поступает с информационного выхода АЦП 1 на 2-й вход блока 3 вычитания. В блоке 3 вычитания находится разйость с,,С2с„ между входным кодом и кодом, соответствующим выходному напряжению . ...а„ -Ь,Ь-,. П Код разности с jCj ,... ,с, поступает на информационный вход накапливающего сумматора 5, причем четыре старших разряда поступают на информационный вход А сумматора 7.1, четы ре средних разряда - на информационный вход А сумматора 7.2, четыре младших разряда - на информационный вход А сумматора 7.3. Одновременно с второго выхода блока 3 вычитания на знаковый вход накапливающего сумматора 5 (вход элемента 6.1 формирователя импульса сброса) поступает сигнал знака разности. В случае если разность с,,С2,...,с отрицательна на вход элемента 6.1 формирователя 6 импульса сброса поступает сигнал логической 1. Если же разность положительна, то - О. На информационные входы В сумматоров 7.1-7.3 поступает код d, ,d2,..,dn, записан84 , ный в регистрах 8.1-8.3. Причем разряды поступают на информационные входы В сумматоров 7.1-7.3 соответственно с записью кодов в регистрах. В сумматорах 7.1-7.3 происходит суммирование этих кодов С|.с,...,с + d, ,d2,.. ,d , , е 2,..., е. Полученный код суммы е,е. по сигналу разрешения записи, посту-. дающему на управляющий вход накапли- вающего сумматора 5 с выхода .Конец преобразования АЦП 1 переписывается в регистры 8.1-8.3. Следует отметить, что сигнал разрешения записи вьщается с учетом времен задержки в блоке 3 вычитания ив сумматорах 7.17.3 накапливающего сумматора 5. Код суммы в, , е 2,..., еу, может иметь как положительныйi так и отрицательный Если знак кода суммы положителен; ;то на,выходе Р переноса сумиатора 7.1 устанавливается сигнал логического О. Логический О устанавливается также на выходе элемента 7.3 формирователя 6 импульса сброса.При этом код суммы е, ,e,j, - - записывается в регистры 8.1-8.3 без изменения. Следует отметить, что наибольшее положительное число на выходе сумматоров 7.1-7.3 имеет вид 0111111111111 где О является символом знака числа. Поэтому, во избежание переполнения п разрядного сумматора при Сложении двух п-разрядных двоичных чисел мы должны всегда иметь О (а« 0) в старшем разряде входного кода. Таким образом, преобразователь код-напряжение работает с 11-разрядным входным кодом. Если же код суммы е,,е j,..,е отрицателен, то на выходе Р переноса сумматора 7.1 единичный сигнал устаногит на выходе элемента 1.3 формирователя импульса сброса единичный сигнгш установки в О регистров 8.1-8.3, вследствие чего устраняется возможность записи кода с отрицательным знаком в регистры 8.1-8.3 и обеспечивается совпадение полярности эталонного напряжения ЦАП 4 и выходного напряжения Uj. В случае, если код выходного напряжения и преобразователя код-напряжение соответствует входному а,а,. ..а,получаем а (,а b,,b.j, ,bj.Тогда код разности с,,с,..,,с равен О и е,,е Напряжение U на выходе преобразова теля остается неизменньм. В случае изменения входного кода а,а, ,..а или изменения параметров элементов устройства (колебания опор ного напряжения ЦАП 4, изменения коэффициента преобразования ЦАП 4 Кп или коэффициента усиления усилителя К у получаем а,,а,..,а Ь, ,Ь, ..,,Ь„. , 84« Тогда на выходе блока 3 вычитания появляется код разности с/,с, .. ..р; ,aj, ... ,а - b,,b2,.. . ,Ь„ f 0. Далее имеем е/,ег,...,е„ d,,d4,,, , с.Код на входе ЦАП 4изменяется таким образом, чтобы компенсировать разность между входным кодом и кодом, соответствующим выходному напряжению преобразователя Ug . Таким образом, преобразователь код-напряжение отслеживает изменения входного кода и компенсирует погрешности, вызванные колебаниями параметров элементов схемы.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для измерения скорости изменения частоты | 1989 |

|

SU1620952A1 |

| Параллельно-последовательный аналого-цифровой преобразователь | 1985 |

|

SU1305851A1 |

| Способ преобразования угла поворота вала в код и устройство для его осуществления | 1988 |

|

SU1647901A1 |

| Устройство для формирования фигур конического сечения на экране электронно-лучевой трубки | 1982 |

|

SU1101877A2 |

| Аналого-цифровой инкрементный дифференциатор | 1985 |

|

SU1343410A1 |

| Устройство для контроля аналоговых объектов | 1985 |

|

SU1288702A1 |

| Формирователь сигналов с заданным законом изменения фазы | 1986 |

|

SU1385239A1 |

| Устройство для воспроизведения аналогового сигнала | 1988 |

|

SU1524175A1 |

| Устройство для контроля аналоговых объектов | 1986 |

|

SU1397941A1 |

| Цифровое устройство для управления трехфазным широтно-импульсным инвертором | 1987 |

|

SU1576944A1 |

ПРЕОБРАЗОВАТЕЛЬ КОД-НАПРЯЖЕНИЕ, содержащий аналого-цифровой преобразователь; усилитель, выход которого является выходнрй шиной, блок вычитания и цифроаналоговый преобразователь, выход которого через, усилитель соединен с входом аналого-цифрового преобразователя, первые выходы которого соединены с первыми входами блока вычитания, вто рые входы которого являются шинами входного кода, отличающийс я тем, что, с целью повьш1ения надежности и точности путем расширения диапазона компенсации погрешностей,в него введен накапливающий сумматор , выполненный на формирователе импульса сброса, последовательно соединенных сумматорах комбинационного типа и регистрах, выходы которых соединены с входами цифроаналогового преобразователя и с вторыми входами сумматоров, третьи входы которых подключены к соответствующим первым выходам блока вычитания, второй выход которого соединен с первым входом формирователя импульса сброса, второй вход которого подключен к выходу переноса сумматора комбинационного типа старших разрядов, а выход к входу установки в О регистров, i входы разрешения записи которых соединены с вторым выходом аналого-циф(Л рового преобразователя, а информационные входы - с соответствующими информационными выходами сумматоров комбинационного типа, первый вход сумматора комбинационного типа младших разрядов соединен с шиной нулевого потенциала, при этом третий вход формирователя импульса сброса CD соединен с шиной постоянного потенциала . Х 4

| СПОСОБ ИСПЫТАНИЙ НА УДАРНЫЕ ВОЗДЕЙСТВИЯ | 2008 |

|

RU2386939C1 |

| Патент ФРГ № 3003099, кл | |||

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

Авторы

Даты

1985-12-07—Публикация

1984-06-14—Подача