1

Изобретение отпоеится i siidJiioBOii технике н может быть ncno,ib:uj3a но в /етройствах, где оеу1иестЕ5ляется прием и дешифрация кодированной штфоп..-ацип.

Известно устройство для ipi:e :a ннформации, содержандее раснределнтель разрядов, поразрядные фиксаторы приема чнсла, логические элементы И,ЧР. И, времязадерживаюнще. ценочки 1 .

Недостатками нзвестногч) ххтройства является недостаточная помехохстойчивость, обусловленная возможностью приема не только полезных еи1т-1а,1он, т. е. сигналов с заданными параметрами, но и ложных сигналов, т. е. сигналов, параметры которых отличаются от заданных, в частности, но д.1ите.1ьности и нериод} с,1ед( та., и недостаточно высокое быстродейст1 ие устройства, обусловленное обязательным наличием паузы между принимаемым ; соседними числами. Длительность этой 1;аузы до.лжна быть не менее двух период с.1едования тактов принимаемого чис.та.

Наибо.тее б.1изким техническим решеннем к данному изобретешгю является устройство для приема ннформации, содержащее раснределитель тактов, дискретный , приемный регистр, иричем вход г)асн|)еделитс 1я

2

тактов соединен со входом д:;с1 ретпого фильтра |2|. Нсдостат| ам11 нзнсслшго xcTpoiicTва явля1огся нев1 1сокое оыстрсхчействне и недостаточная 1К1мехо,ии1ипиепн;)ст1.

Це,1Ь;о нзобретення яв/;яотся новьпненне номехохстойчивости и быстродействия стpofiCTBa.

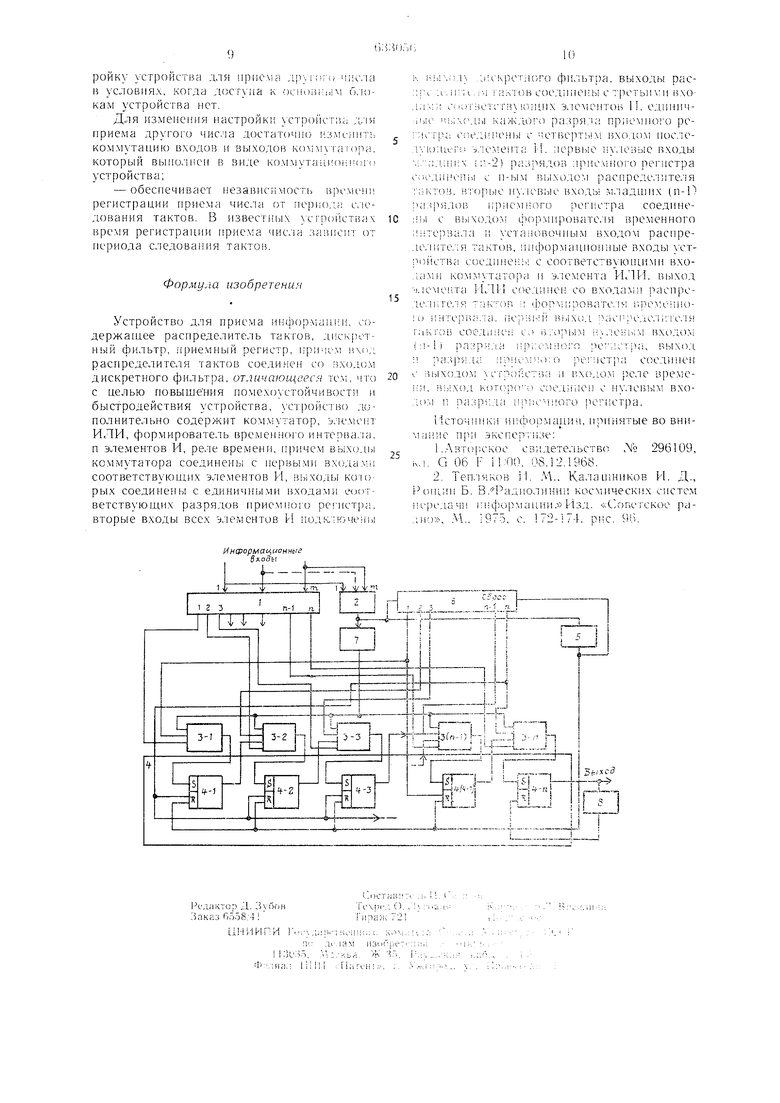

-казаиная нель достиг-ается тел;, что устройство Д1) 1нпте, 1ьно солсрйчнг коммхтагоп. элел-,мг ITilT (iopMi;poiiaTe, временного и1 те1М}ала, п э,1е :ентов 11. pc,ie времени,

нрнчем выходы ;чомм тато -а соединены е nepBbiMi р, соответствуюни1х э.тементов И, выходь которых с еднннчными входами соответетвхтонщх разрядов приемного регнстпа, вторые входы зсех элементов 1л подключены к выходу дискретного

5 4)и,. выхо,, р; снре;.е. тактов соединены с третьими входами соответствуюHUix элементов П, сдпнич;1Ь1е выходы каждого разряда )ro регистра соединены с четвер7151 входом иослел 1ои;сго э.чемента

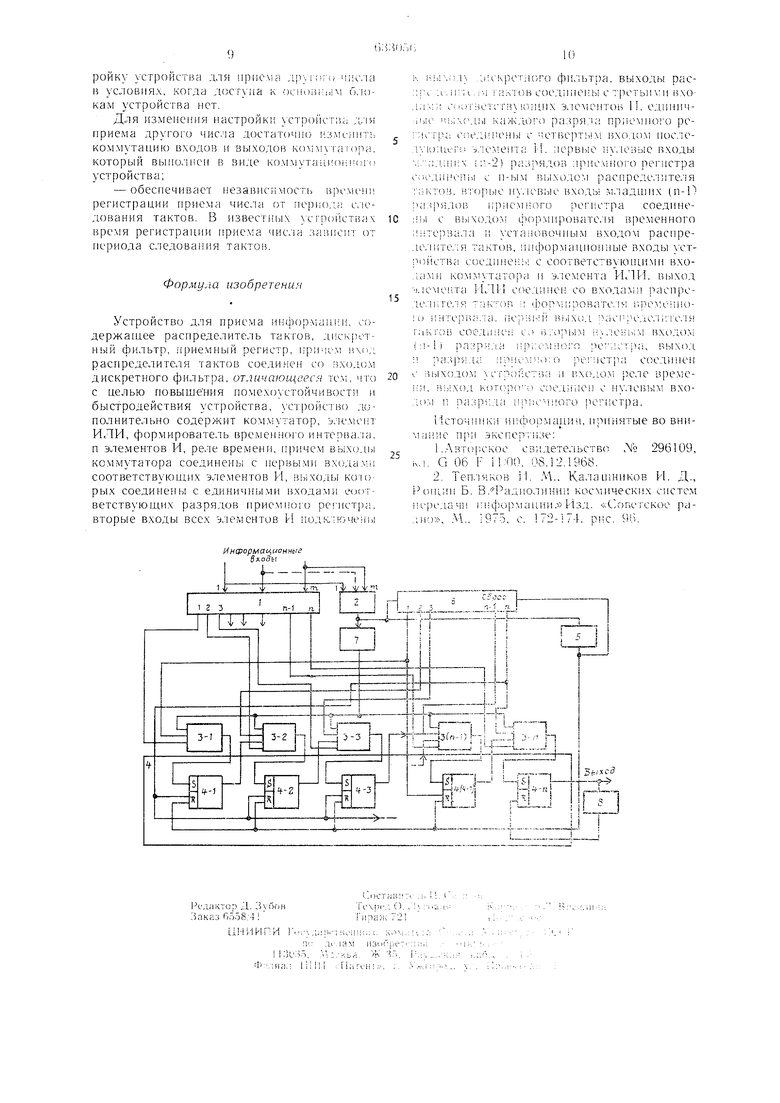

1Л, ncnu,e )е входы м,1ад111их (п-2) разояд,.Г;;; и:)исл:но Ч; peiHiCTpa. соединены с з;дходом рас:|реде,1н:с,1я гактов. втоpi ie нч-лсв ме вход;.; :ладн; ;х (n-ii разрядов :риел ;;ri: pei;:cT:-ia соединен1 1 с выходом фор:.1:;р::;и тсля ;;pe:.-c;iHoro интервала и становочным входом распределителя тактов, информационные входы устройства, соединены с соответствующими входами коммутатора и элемента ИЛИ, выход элемента ИЛИ соединен со входами распределителя тактов и формирователя временного интервала, первый выход распределителя тактов соединен со вторым нулевым входом (п-1) разряда приемного регистра, выход п. разряда приемного регистра а единеи с выходом устройства и входом реле времени, выход которого соединен с нулевым входом п разряда приемного регистра. На чертеже представлена блок-схема устройства для приема информации, передаваемой п разрядным кодом с основанием т. Устройство содержит коммутатор , элемент ИЛИ 2, элементы И (3-1) -ЦЗ-п), приемный регистр 4, формирователь временного интервала 5, распределитель тактов 6, дискретный фильтр 7, реле времени 8. Информационные входы устройства соединены с соответствующими входами коммутатора 1 и элемента ИЛИ 2, выходы коммутатора 1 соединены с первыми входами соответствующих элементов И 3, выходы которых соединены с единичными входами соответствующих разрядов приемного регистра 4, вторые входь всех элементов И 3 объединены и соединены с выходом дискретного фильтра 7, выходы распределителя тактов 6 соединены с третьими входами соответствующих элементов И 3, единичные выходы каждого разряда приемного регистра 4 соединены с четвертым входом последующего элемента И 3, первые нулевые входы старших (п-2) разрядов приемного регистра 4 объединены и соединены с выходом распределителя тактов 6, вторые нулевьк; входы первых (п-1) разрядов приемного регистра 4 объединены и соединены с выходом формирователя временного интервала 5 и нулевым входом распределителя тактов 6, входы распределителя тактов 6, формирователя временного интервала 5 и дискретного фильтра 7 объедняены- и соединены с выходом элемента ИЛИ 2, первый выход распределителя тактов 6 соединен со вторым нулевым входом (п-1) разряда приемного регистра 4 соединен с выходом устройства и входом реле времени 8, выход которого соединен с нулевым п разрядом приемного регистра 4. В исходном состоянии, т. е. в отсутствии сообщения, формирователь временного интервала 5, предназначенный для контроля периода следования тактов сообщения, формирует импульсы сброса, с помощью которых распределитель тактов 6 и все триггеры приемного регистра 4, кроме триггера 4-п, удерживаются в «нулевом состоянии. Удерживание в «нулевом состоянии триггера (4-п) осуи1ествляется импульсом, подааемым на его нулевой вход с выхода реле ремени 8. В качестве формирователя временного нтервала 5 использован управляемый генератор импульсов, период следования коорых вщбран из условия , где: Т - период следования импульсов сброа в исходном состоянии; Тп- период следования тактов сообщения. В качестве распределителя тактов 6 может быть использован, например, сдвиговый регистр. В качестве реле времени 8 использован управляемый генератор импульсов, период следования которых выбран равным времени регистрации приема сообщения. п разрядная информация числа в виде последовательного кода с основанием m tio m щинам поступает на m входов коммутатора 1 и элемента ИЛИ 2, предназначенного для формирования тактов сообщения. С выхода элемента ИЛИ 2 такты поступают на входы формирователя временного интервала 5, распределите Ш тактов 6, днскретного фильтра 7. По каждому такту сообщения в формирователе е.ременного интервала 5 осуществляется сброс времязадающей цепочки и поэтому, если интервал между тактами сообщения це превышает г ериода следования импульсов формирователя временного интервала 5, то ирлпульс сброса во время приема сообщения не будет вырабать ваться и, таким образом, формирователь временного интервала 5 не будет оказывать какого-либо влияния на работу устройства во время приема сообщения. Если интервал времени между любыми соседними разрядами числа превысит период следования импульсов формирователя временного интервала 5 (такой случай .может иметь место при пропадании одного или нескольких тактов сообщения, npi; увеличении периода следования тактогз сообщения, а также после последнего такта сообщения), то через интервал времени, равный периоду следования импульсов формирователя временного интервала 5 после приема соседнего разряда числа формирователе.м временного интервала 5 вырабатывается импульс сброса, по -которому распределитель тактов 6 и триггера приемного регистра 4 (кроме триггера 4-п) устанавливаются в исходное состояние, т. е. осуществляется сброс ранее принятой информации. Распределитель тактов 6 имеет п выходов (по числу тактов (разрядов) в пркнимземом числе). После прихода первого такта (иервого разряда) выходной сигнал распределителя тактов 6 появляется только на первом выходе, после прихода второго такта (второго разряда) числа - только на втором выходе, после прихода п-го такта (разряда) числа - только на п-ом выходе. Выходы распределителя тактов 6 соединены с третьими входами одноименных элементов И 3, кроме того, первый выход распределителя тактов б соединен с н -левым входом триггера 4- (n-i) приемного регистра 4, а п-ый выход - со вторыми входами триггеров (4-1) - 4-(п-2) приемного регистра 4. Коммутатор I, используемый в предлагаемом устройстве, имеет m входов и п выходов, причем количество выходов равно количеству разрядов п в принимаемом сообщении, а количество входов - основанию кода гп, с помощью которого передается сообщение. Входы и выходы в коммутаторе 1 соединены между собой в соответствии с кодом числа, на прием которого настроено устройство. В качестве примера рассмотрим коммутацию входов и выходов в коммутаторе I для приема числа 3i214, передаваемого в виде шестиразрядного сообщения кодом с основанием четыре. В этом случае в коммутаторе. 1 первый вход соединен со вторым, четвертым и шестым выходами, второй вход - с. тертьим выходом, третий вход - с первым выходом, четвертый вход - с пятым выходом. При такой коммутации входов и выходов Б коммутаторе I при поступлении на его входы числа 31214 выходной сигнал на его первом выходе появится после прихода первого разряда числа, на втором -после прихода второго, четвертого и шестого разрядов, на третьем - после прихода третьего разряда, на четвертом - после прихода второго, четвертого и шестого разрядов, на пятом - после прихода пятого разряда, на шестом - после прихода второго, четвертого и aiecToro разрядов. Выходы коммутатора I соединены с первыми входами одноименных элементов И 3. Дискретный фильтр 7 предназначен для повышения помехоустойчивости устройства и установлен в тракте его приема, в частности в цепи токов. Если длительность тактов на выходе элемента ИЛИ 2 превысит определенную величину, определяемую постоянной времени дискретного фильтра 7, то на выходе дискретного фильтра 7 будет сформирован импульс (или серия импульсов), длительность которого много меньше длительности выходного сигнала. Выходной сигнал дискрст1юго фильтра 7 подается на вторые входы элементов И 3 для онроса на ннх выходов коммутатора 1, распределителя тактов б, состояний триггеров приемного регистра 4. В качестве примера рассмотрим работу устройства при приеме числа 312141, причем длительность символов числа и период следования тактов не отличаются от заданных. После прихода первого разряда числа сигнал появ.чяется одновременно на первом выходе коммутатора 1, на первом вь1ходе распределителя тактов б и на выходе дисКретного фильтра 1; и поэтому сигналом элемента И 3- происходит установка триг гера 4-1 приемного регистра 4 в единичное состояние н, следовательно, снятие блокировки для срабатывания элемента И 3-2 по входу 4. Одновременно с приходом первого разряда числа сигналом с первого выхода распределителя тактов 6 осуществляется установка в «нулевое состояние триггера 4-5 приемного регистра 4. После прихода второго разряда числа одновремеиио сигнал появляется на втором выходе коммутатора 1, на втором выходе распределителя тактов 6, на- выходе дискретного фильтра 7 и поэтому сигналом с элемента 3-2 происходит установка триггера 4-2 приемного регистра / в единипиое состояи.ие, и следовлтельно, снятие блокировки для срабатывания элемента И 3-3 по входу 4. Аналогичным образом после прихода третьего разряда числа будет записана едиинчиая информация в триггер 4-3, после прихода четвертого разряда - в триггер 4-4. после прихода пятого разряда - в триггер 4-5. после прихода шестого разряда - в трипер 4-6, свидетельствуя тем самым о приеме числа 3I214I. После установки триггера 4-6 в единичное состояние осуществляется пуск реле времени 8. Через интервал времени, определяемым постоянной времени реле времени 8, формируется на выходе реле времени 8 импульс, которым осуществляется установка в «иу.яевое состоя11ие триггера 4-6 по ну.1евому входу ч тем самым прекращается регистрация правильности приема чнсла 312141. Одновременно с приходом последнего шестого разряда сигналом с шестого выхода распределителя тактов 6 нронсходит установка в исходное «нулевое состояние триггеров (4-i) -Сч-4) Г1рие П1ого регистра 4 по первому нулевому входу, тем самым оОсснечивая готовность устройства для п|)нема очередного слова. Если два числа будут поступать на вход устройства без паузы, т. е. интервал между последним тактом первого числа и первым тактом второго чнсла равен nepuo;i,y с,педоEaHiJH тактоБ сообщения, то может происходить Паралле.гьно и регистрация прав льности приема первого слова н )ИСг, второго слова, причем время выдержки pe.ie времени 8 должно быть выбрано в этом случае таким- образом, чтобы к моменту приема последнего разряда второго слова регистрация аравильности приема первого слова должна быть закончена. Если между ноступающнмн числами имеется пауза, превышающая два периода следования тактов сообщения, то установка всех триггеров нриемного регистра 4, кроме (4-n) будет происходить по импульсу сброси формируемому формирователем временного интервала 5 через интервал времени Т после последнего такта сообщения, а устано 5ка триггера 4-п приемного регистра 4 -- но импульсу реле времени (8). Рассмотрим работу устройства нри приеме числа 312141, в котором интервал между четвертым и пятым разрядами превьпиаот 1,5 Т. Прием первых трех разрядов числа произойдет так же, как и прием числа 312141, в котором интервал между всеми разрядами равен Т. В связи с тем, что интервал между четвертым и нятым раз|)ядами превышает 1,5 Т, то-есть величину Т. то в этом интервале будет формировате.юм временного интервала 5 сформирован импульс сброса, по которому будет осушлчтвлен сброс единичной информаиии, зашканной в триггерах 4-1, 4-2, 4-3, 4-4 приеммоч) регистра 4. После прихода 11ято1о разряда числа выходной сигнал появится на выходе коммутатора 1, на пятом выходе распределителя тактов 6, на вьходе дискретного фильтра 7, но заги-iCb единично) информации в триггер 4-5 ириелиюго peincTра 4 не произойдет, так как прохождение сигнала на единичный вход трпгчч ра 4-5 не произойдет из-за блокировки И 3-5 по входу 4 сигналом, подаваемым с единичного выхода триггера 4-4. Ана;1огичн| м образом не будет принят и Н1естой разряд слова. Таким образом число, интерва. мсж.чу любыми соседними тактами кото)ого отличается от заданного более чем в 1,5 раза, не будет принято данным устройством. Рассмотрим работу устройства, настроенного на прием слова 312141, ири ириеме слова, например, 313141. . Так как первый и второй разряды поступающего на вход устройства числа совнадают с первым и вторым разрядом числа, на прием которого настроено устройстгю. то они будут приняты аналогично описанному выше. При поступлении на вход устройства третьего разряда числа на третьем выходе коммутатора 1 сигпала не будет (выходной сип1ал будет только на пepБo i выходе коммутатора 1), следовате.льно, не будет сигнала и на выходе элемента И 3-3 и поэтому единичная информация ие будет записана в триггер 4-3 приемного pei-истра 4 и не будет снята блокировка элемента 4-4 по входу 4. При поступ.1ении на вход устройства четвертого разряда числа появятся сигналы на четвертом выходе коммугатора 1. на четвертом выходе раснределителя тактов 6 и на выходе дискретного фильтра 7. но из-за присутствия запрещающего сигнала на входе 4 элемента И ,4-4 запись единичной информации в триггер 4-4 прием110|-о регистра не ироизойдет. По аналогичной иричине не произойдет запись едииичеюй информации в триггер 4-5, 4-6 приемного |ieгисгра 4 1ри ПОСТ , нлспии нятого и нкчтого разрядов ,ia. Таким образом, нри постунленни lia вход устройства числа, код ксггорого от;1ичается от Ko;ia чнсла. д.1я нриема которого ностроено устройство, хотя бы в о.июм разряде, такое число не будет н)инят() устройством. Рассмотри.м работу устройства нри нрисме 4HC,i;i 312141, у которого длите.чьность )лов всех разрядов, кроме нятого, .и период следоваи1;я тактов не отличаются от задаииых. Д.лител1ди)сть же си.мво.ча пятого ра.зряда мепьи;е заданной. Прием первых чет1лрсх разрядов числа будет ocyHiecTB.ieii аналогично OHHcai-noMy, т. с. неред приемом нятого разряда числа сдипнчная И1к}и)рмаиия будет за.сисана 13 Tpnfiooax |4-П - i4-4; приемного рсчпс ра 4. При HocTyineHHH i;a вход x cTpoHCTJsa HHTOix) разряда чис. на 1, 3, 4 входах элсviCMia Н 3-5 будут пазрсигакмиис с1Пна:п,1. ио на 2 э.юмепта И 3-5 си1нала не из-за . что днскрстн1 11 филыр 7 ходной ciiiH;}., длите.пыюсть которо;() менее за.чанной. не «нропустит. ()тс тст15ие ISMHy.ibca онроса на вых(}де дискиетшмч) (Ьильтра 7. и следоватоль;1о, i; ип входе 2 4, :еммга И 3-5, npi; ( :;ято1о р;;нрмда числа не иозволит записат едини;ij-/K) ин1|:)ормаиию в триптр -1-5 птиелиюго регистра 4. При поступлении на вход устп;.Истип niccioro разряда чис.та кшвятся pa:5pe;iaioi;u:e си1иа;;ы на входах 1, 2. 3 . П 3-п, 1К) из-за присутствия заирещак)Н;с1о сигнал;; на входе 4 элемента И 3-6. с триггера 4-5, запись единиЧ|пй ;i:;i;:0ii :;. iiUH в триггер 4-6 iipneMioro :)ei iv-Tpa ис произойдет. Таким образом, число, длите. хотя бы одио1(. ;побого символа Koropoixj Оу,и-т MiMice заданной, не будет принято ): устройством. Предлагаемое устройстве д.тя цэиома чпсе. I н 1год1И) от,|нчастся от 1гч НСТ1;ых Tcvi. что обладает noBiiiHicHHijiM на сравиешпо с известны п1 устройствами бысгродеихтвис.м. что выражается в том. что: --обеспечивает ирием двух n.iii бо.чее чисел, передаваемых друг за друго.м с i-ii-:Tepiia.TO.M ие меиее одного такта сося щения; - об.ладает )енчой но сравненщо с нзвестиыми устройствами номсхохстойчиностыо, что выражается в том. чтч) устройством не и)пнимаются .ia, на|)а.мстры сигна.тов которых - - в частчости с.чедовання тактов и длительность oiMc.ibiKjri.) символа. ()т;1нчак)тся от зада1;1Н)1х; - обеспечивает прием чисе,1. нерсд;1ваемых не TO.iLiKO Д1и)ичным кодом (ко.чом с основанием 2). как это имеет icc o в п/;вест ых устройствах, ио i: чисе;:, licpe/iaiinvмых кодом с ocHOBaifiiCM более 2; 1 0315оляет оперативно iciMeiinib пас-;

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для приема информации | 1975 |

|

SU639003A1 |

| УСТРОЙСТВО ДЛЯ СОПРЯЖЕНИЯ ЭВМ С КАНАЛОМ СВЯЗИ | 1992 |

|

RU2043652C1 |

| МНОГОКАНАЛЬНАЯ СИСТЕМА ПЕРЕДАЧИ И ПРИЕМА ДИСКРЕТНОЙ ИНФОРМАЦИИ | 2001 |

|

RU2207729C2 |

| Многоканальный преобразователь кода во временной интервал | 1983 |

|

SU1100728A1 |

| Устройство для приема информации | 1982 |

|

SU1045242A1 |

| Цифровой демодулятор сигналов относительной фазовой манипуляции | 1986 |

|

SU1374443A1 |

| Устройство для цикловой синхронизации | 1981 |

|

SU1107317A1 |

| СПОСОБ И УСТРОЙСТВО ДЛЯ ПЕРЕДАЧИ И ПРИЕМА СИГНАЛОВ С ОГРАНИЧЕННЫМ СПЕКТРОМ (ВАРИАНТЫ) | 2004 |

|

RU2265278C1 |

| СИСТЕМА ДЛЯ ПЕРЕДАЧИ И ПРИЕМА ИНФОРМАЦИИ КОДОМ ПЕРЕМЕННОЙ ДЛИНЫ | 1996 |

|

RU2123765C1 |

| Система для передачи и приема дискретной информации | 1979 |

|

SU903850A1 |

Авторы

Даты

1978-11-15—Публикация

1975-04-11—Подача