1

Изобретение относится к области вычислительной техники и предназначено для использования в составе приборов и систем управления различными объектами.

Известно устройство для дифференцирования l , содержащее генератор опорной частоты, пять счетчиков, делитель, счетчик результата, триггер, четыре группы схем запрета (элементов И) и одну схему запрета (элемент И) . Устройство l предназначено для вычисления производной обратной величины от входного кода. Путем добавления одного дополнительного счетчика результата и повторения цикла преобразования, устройство l может быть использовано для дифференцирования входного сигнала. Недостатками устройства 1 являются: узкие функциональные возможности, связанные с отсутствием возможности вычисления второй производной; низкое быстродействие за счет необходимости двухкратного преобразования кода во временной интервал (для каждого отсчета входной последовательности) и низкая точность в связи с тем, что дифференцирование осуществляется без сглаживания случайных оимбок.

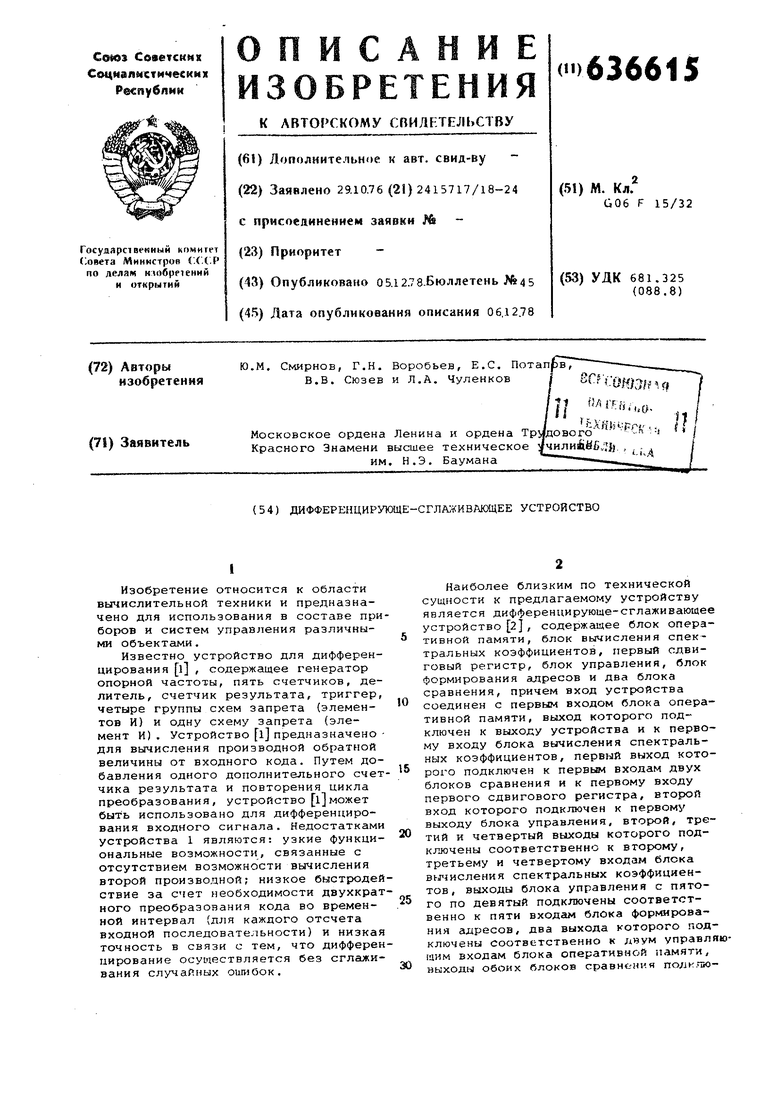

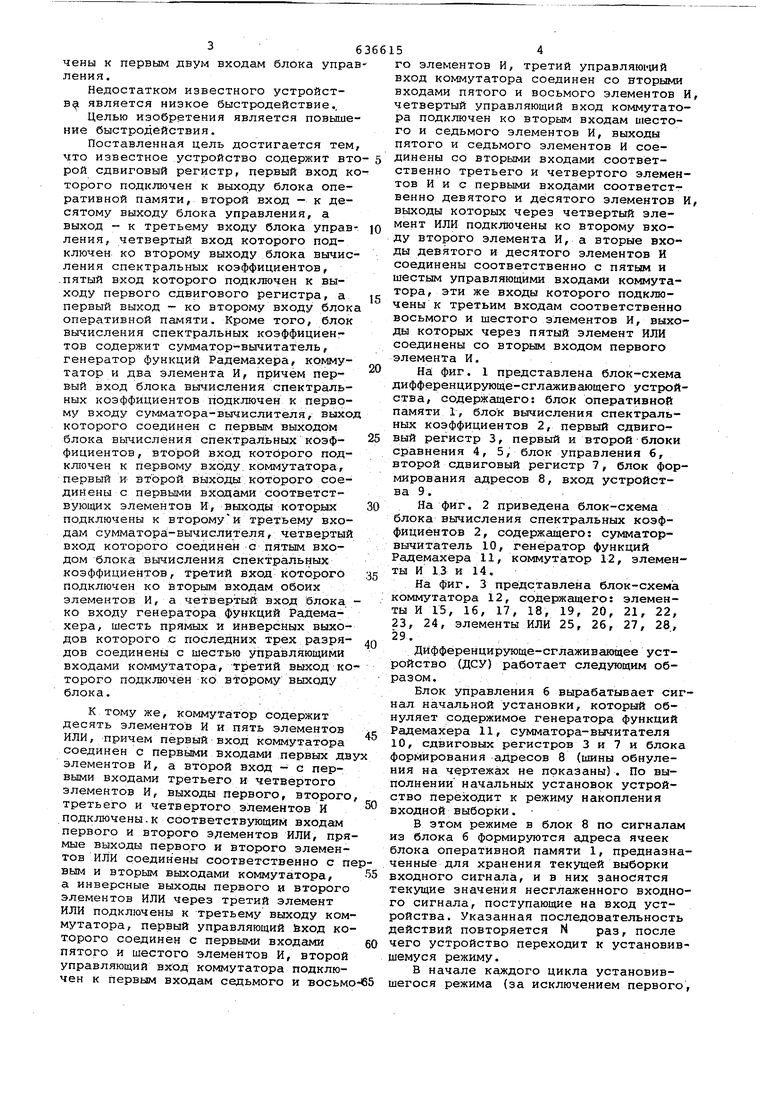

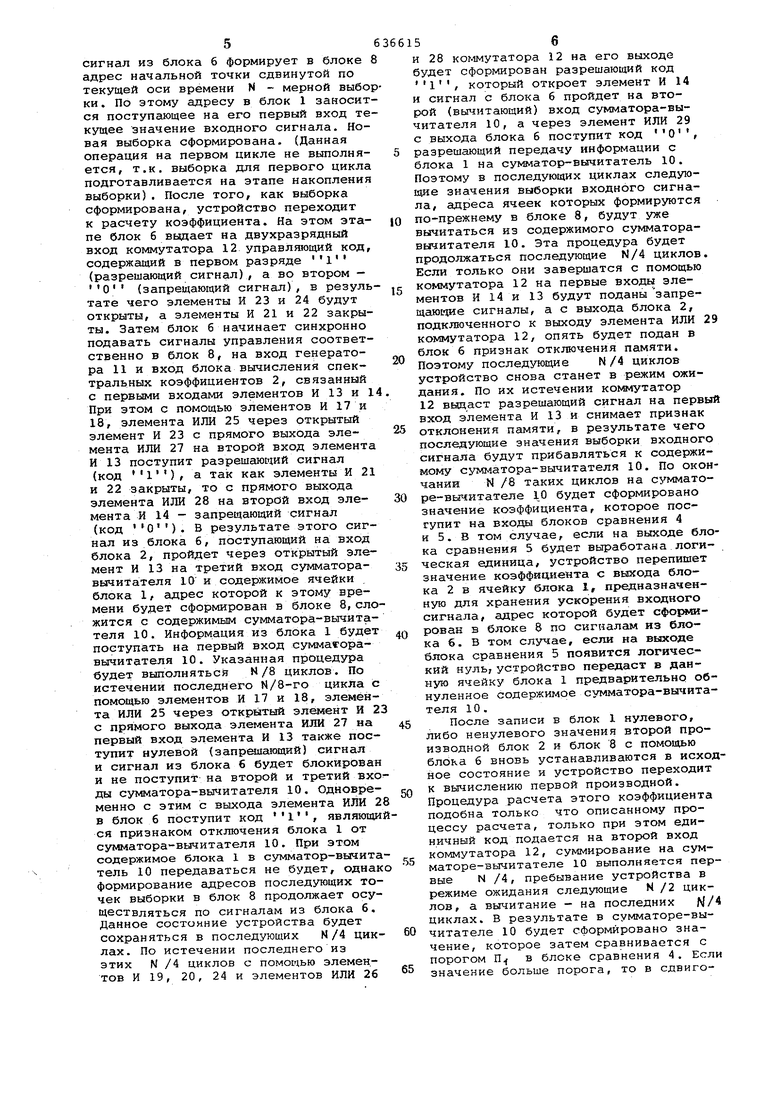

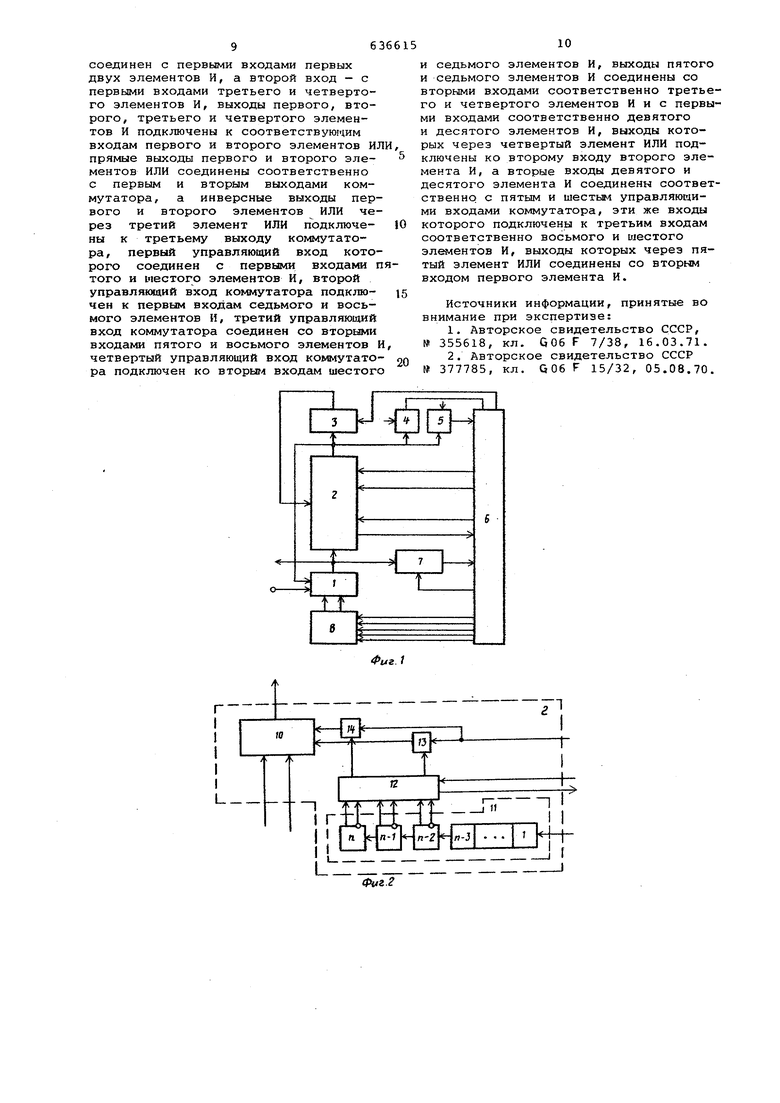

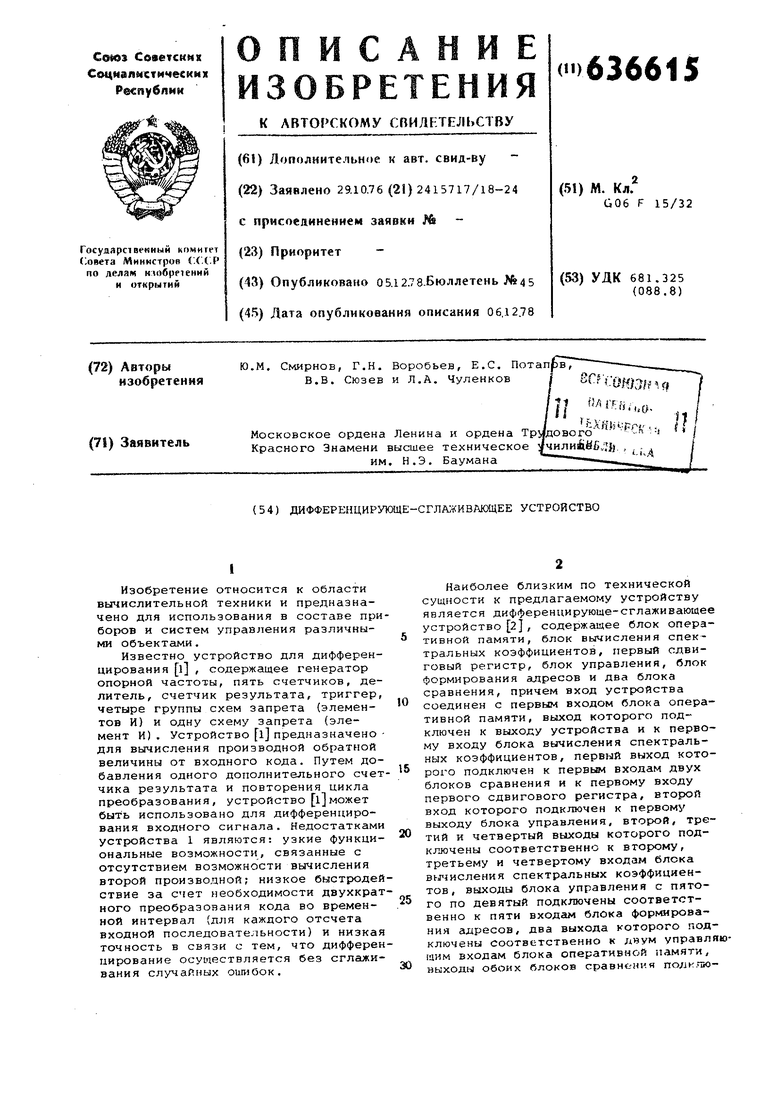

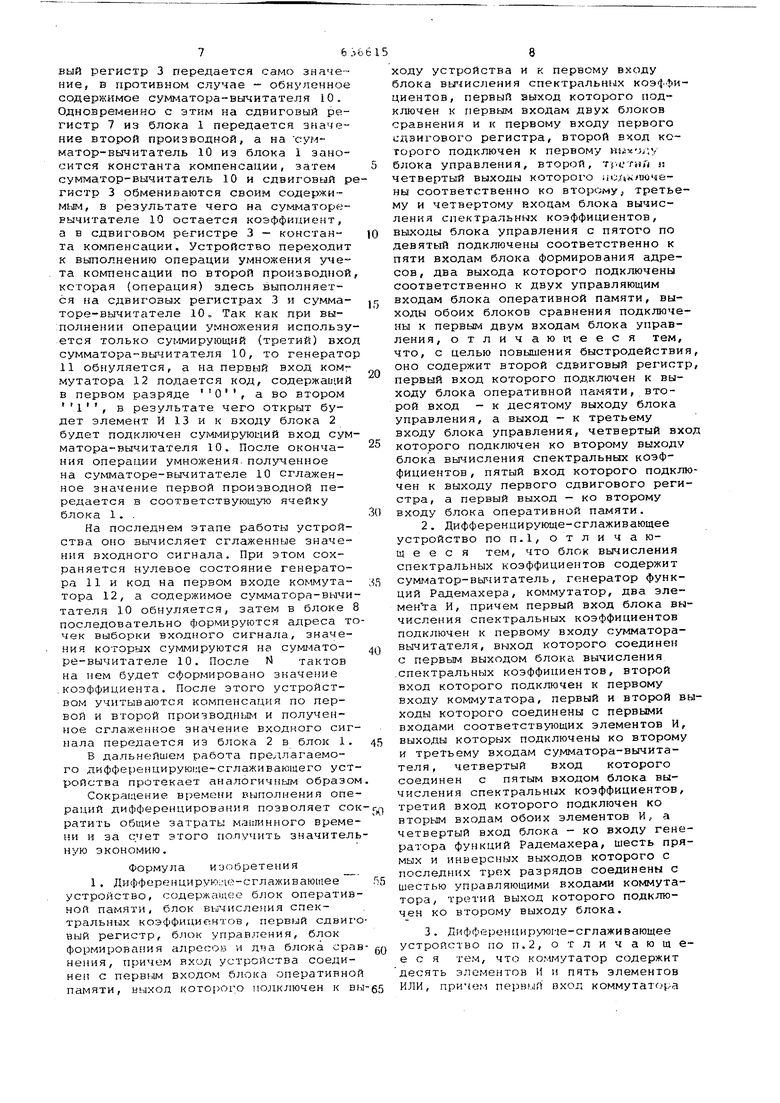

Наиболее близким по технической сущности к предлагаемому устройству является дифференцируюше-сглаживающее устройство 2, содержащее блок оперативной памяти, блок вычисления спектральных коэффициентов, первый сдвиговый регистр, блок управления, блок формирования адресов и два блока сравнения, причем вход устройства соединен с первым входом блока оперативной памяти, выход которого подключен к выходу устройства и к первому входу блока вычисления спектральных коэффициентов, первый выход которого подключен к первьви входам двух блоков сравнения и к первому входу первого сдвигового регистра, второй вход которого подключен к первому выходу блока управления, второй, третий и четвертый выходы которого подк.п}очены соответственно к второму, третьему и четвертому входам блока вьмисления спектральных коэффициентов, вь1ходы блока управления с пятого по девятый подк.пючены соответственно к пяти входам блока формирования адресов, два выхода которого подключены соответственно к двум управляющим входам блока оперативной памяти, выходы обоих блоков сравнсН .я полк.гао3чены к первым двум входам блока упра ления. Недостатком известного устройству является низкое быстродействие.. Целью изобретения является повыше ние быстродействия. Поставленная цель достигается тем что известное устройство содержит вт рой сдвиговый регистр, первый вход к торого подключен к выходу блока оперативной памяти, второй вход - к десятому выходу блока управления, а выход - к третьему входу блока управ ления, четвертый вход которого подключен ко второму выходу блока вычис ления спектральных коэффициентов, -ПЯТЫЙ вход которого подключен к выходу первого сдвигового регистра, а первый выход ко второму входу блок оперативной памяти. Кроме того, блок вычисления спектральных коэффициентов содержит сумматор-вычитатель, генератор функций Радемахера, коммутатор и два элемента И, причем пер вый вход блока вычисления спектральных коэффициентов подк.шочен к первому входу сумматора-вычислителя, выхо которого соединен с первым выходом блока вычисления спектральных коэффициентов, второй вход которого подключен к первому входу.коммутатора, первый и второй выходы,которого соединены с первыми вх.ояами соответствующих элементов И, выходы которых подключены к второму и третьему входам сумматора-вычислителя, четвертый вход которого соединен с .пятым входом блока вычисления спектральных коэффициентов, третий вход которого подключен ко вторым входам обоих элементов И, а Четйертый вход блока ко входу генератора функций Радемахера, шесть прямых и инверсных выходов которого с последних трех разрядов соединены с шестью у-правляющими входами коммутатора, третий выход ко торого подключён ко второму выходу блока.. К тому же, коммутатор содержит десять элементов И и пять элементов ИЛИ, причем первый вход коммутатора соединен с первыми входами первых дв элементов И, а второй вход - с первыми входами третьего и четвертого элементов И, выходы первого, второго третьего и четвертого элементов И подключены.к соответствующим входам первого и второго элементов ИЛИ, пря мые выходы первого и второго элементов иЛи соединены соответственно с п вым и вторым выходами коммутатора, а инверсные выходы первого и второго элементов ИЛИ через третий элемент ИЛИ подключены к третьему выходу ком мутатора, первый управляющий Ьход ко торого соединен с первыми входами пятого и шестого элементов И, второй управляющий вход коммутатора подключен к первым входам седьмого и восьм 54 го элементов И, третий управляю1№1й вход коммутатора соединен со вторыми входами пятого и восьмого элементов И, четвертый управляющий вход коммутатора подключен ко вторым входам июстого и седьмого элементов И, выходы пятого и седьмого элементов И соединены со вторыми входами соответственно третьего и четвертого элементов И и с первыми входами соответственно девятого и десятого элементов И, выходы которых через четвертый элемент ИЛИ подключены ко второму входу второго элемента И, а вторые входы девятого и десятого элементов И соединены соответственно с пятым и шестым управляющими входами коммутатора, эти же входы которого подключены к третьим входам соответственно восьмого и шестого элементов И, выходы которых через пятый элемент ИЛИ соединены со вторым входом первого элемента И. . На; фиг. 1 представлена блок-схема дифф|еренцир тоще-сглаживающего устройства, содержащего: блок оперативной памяти 1, блок вычисления спектральных коэффициентов 2, первый сдвиговый регистр 3, первый и второй блоки сравнения 4, 5, блок управления 6, второй сдвиговый регистр 7, блок формирования адресов 8, вход устройства 9 . На фиг. 2 приведена блок-схема блока вычисления спектральных коэффициентов 2, содержащего: сумматорвычитатель 10, генератор функций Радемахера И, коммутатор 12, элементы И 13 и 14. На фиг. 3 представлена блок-схема коммутатора 12, содержащего: элементы И 15, 16, 17, 18, 19, 20, 21, 22, 23, 24, элементы ИЛИ 25, 26, 27, 28, 29.,. Дйфференцирующе-сглаживающее устройство (ДСУ) работает следующим образом. Блок управления 6 вырабатывает сигнал начальной установки, который обнуляет содержимое генератора функций Радемахера 11, сумматора-вычитателя 10, сдвиговых регистров 3 и 7 и блока формирования адресов 8 (шины обнуления на чертежах не показаны). По выполнении начальнь1Х установок устройство переходит к режиму накопления входной выборки. В этом режиме в блок 8 по сигналам из блока б формируются адреса ячеек блока оперативной памяти 1, предназначенные для хранения текущей выборки входного сигнала, и в них заносятся текущие значения несглаженного входного сигнала, поступающие на вход устройства. Указанная последовательность действий повторяется N раз, после чего устройство переходит к установившемуся режиму. В начале каждого цикла установившегося режима (за исключением первого. сигнал из блока б формирует в блоке адрес начальной точки сдвинутой по текущей оси времени N - мерной выбо ки. По этому адресу в блок 1 заносит ся поступающее на его первый вход те кущее значение входного сигнала. Новая выборка сформирована. (Данная операция на первом цикле не вьтолняется, т.к. выборка для первого цикла подготавливается на этапе накопления выборки). После того, как выборка сформирована, устройство переходит к расчету коэффициента. На этом этапе блок 6 вьщает на двухразрядный вход коммутатора 12 управляющий код, содержащий в первом разряде Ч (разрешающий сигнал), а во втором - О (запрещающий сигнал), в резуль тате чего элементы И 23 и 24 будут открыты, а элементы И 21 и 22 закрыты. Затем блок 6 начинает синхронно подавать сигналы управления соответственно в блок 8, на вход генератора 11 и вход блока вычисления спектральных коэффициентов 2, связанный с первыми входами элементов И 13 и 1 При этом с помощью элементов И 17 и 18, элемента ИЛИ 25 через открытый элемент И 23 с прямого выхода элемента ИЛИ 27 на второй вход элемента И 13 поступит разрешающий сигнал (код ), а так как элементы И 21 и 22 закрыты, то с прямого выхода элемента ИЛИ 28 на второй вход элемента И 14 - запрещающий сигнал (код О). В результате этого сигнал из блока 6, поступающий на вход блока 2, пройдет через открытый элемент И 13 на третий вход сумматоравычитателя 10 и содержимое ячейки блока 1, адрес которой к этому времени будет сформирован в блоке 8, сло жится с содержимым сумматора-вычитателя 10. Информация из блока 1 будет поступать на первый вход сумматоравычитателя 10. Указанная процедура будет выполняться N/8 циклов. По истечении последнего N/8-го цикла с помощью элементов И 17 и 18, элемента ИЛИ 25 через открытый элемент И 2 с прямого выхода элемента ИЛИ 27 на первый вход элемента И 13 также поступит нулевой (запрещающий) сигнал и сигнал из блока 6 будет блокирован и не поступит на второй и третий вхо ды сумматора-вычитателя 10. Одновременно с этим с выхода элемента ИЛИ 2 В блок б поступит код являющи ся признаком отключения блока 1 от сумматора-вычитателя 10. При этом содержимое блока 1 в сумматор-вычита тель 10 передаваться не будет, однак формирование адресов последующих точек выборки в блок 8 продолжает осуществляться по сигналам из блока 6, Данное состояние устройства будет сохраняться в последующих N/4 циклах. По истечении последнего из этих N /4 циклов с помощью элементов И 19, 20, 24 и элементов ИЛИ 26 и 28 коммутатора 12 на его выходе будет сформирован разрешающий код , который откроет элемент И 14 и сигнал с блока 6 пройдет на второй (вычитающий) вход сукматора-вычитателя 10, а через элемент ИЛИ 29 с выхода блока 6 поступит код разрешающий передачу информации с блока 1 на сумматор-вычитатель 10. Поэтому в последующих циклах следующие значения выборки входного сигнала, адреса ячеек которых формируются по-прежнему в блоке 8, будут уже вычитаться из содержимого сумматоравычитателя 10. Эта процедура будет продолжаться последующие N/4 циклов. Если только они завершатся с помощью коммутатора 12 на первые входы элементов И 14 и 13 будут поданы запрещаю15ие сигналы, а с выхода блока 2, подключенного к выходу элемента ИЛИ 29 коммутатора 12, опять будет подан в блок 6 признак отключения памяти. Поэтому последующие N/4 циклов устройство снова станет в режим ожидания. По их истечении когдалутатор 12 выдаст разрешающий сигнал на первый вход элемента И 13 и снимает признак отклонения памяти, в результате чего последующие значения выборки входного сигнала будут прибавляться к содержимому сугф атора-вычитателя 10. По окончании N /8 таких циклов на сумматоре-вычитателе 10 будет сформировано значение коэффициента, которое поступит на входы блоков сравнения 4 и 5. В том случае, если на выходе блока сравнения 5 будет выработана логическая единица, устройство перепишет значение козффициеита с выхода блока 2 в ячейку блока 1, предназначенную для хранения ускорения входного сигнала, адрес которой будет сформирован в блоке 8 по сигналам из блока 6. В том случае, если на выходе блока сравнения 5 появится логический нуль, устройство передаст в яаннуто ячейку блока 1 предварительно обнуленное содержимое сумматора-вычитателя 10. После записи в блок 1 нулевого, либо ненулевого значения второй производной блок 2 и блок 8 с помощью блока 6 вновь устанавливаются в исходное состояние и устройство переходит к вычислению первой производной. Процедура расчета этого коэффициента подобна только что описанному процессу расчета, только при этом единичный код подается на второй вход коммутатора 12, суммирование на сумматоре-вычитателе 10 выполняется первые N /4, пребывание устройства в режиме ожидания следующие N /2 циклов, а вычитание - на последних N/4 циклах. В результате в сумматоре-вычитателе 10 будет сформировано значение, которое затем сравнивается с порогом П в блоке сравнения 4. Если значение больше порога, то в сдвигевый регистр 3 передается само значение, Б противном случае - обнуленное содержимое сугФштора-вычитателя 10. Одновременно с этим на сдвиговый регистр 7 из блока 1 передается значение второй производной, а на сумматор-вьгаитатель 10 из блока 1 заносится константа компенсации, затем сумматор-вычитатель 10 и сдвиговый р гистр 3 обмениваются своим содержимом, в результате чего на сумматоревычитателе 10 остается коэффициент, а в сдвиговом регистре 3 - константа компенсации. Устройство переходит к вьлполнению операции умножения учета компенсации по второй производной которая (операция) здесь выполняется на сдвиговых регистрах 3 и сумматоре-вычитателе 10„ Так как при вы:полнении операции умножения использу ется только суммирующий (третий) вхо сумматора-вычитателя 10, то генерато 11 обнуляется, а на первый вход коммутатора 12 подается код, содержащий в первом разряде О, а во втором , в результате чего открыт будет элемент И 13 и к входу блока 2 будет подключен сумдмируюиий вход сум матора-вычитателя 10. После окончания операции умножения-полученное на сумматоре-вычитателе 10 сглаженное значение первой производной передается в соответствующую ячейку блока 1. . На последнем этапе работы устройства оно вычисляет сглаженные значе ния входного сигнала. При этом сохраняется нулевое состояние генератора 1 1 и код на первом входе коммутатора 12, а содержимое сумматора-вычи тателя 10 обнуляется, затем в блоке последовательно формируются адреса т чек выборки входного сигнала, значения которых сумглируются на сумг аторе-вычитателе 10. После Н тактов на нем будет сформировано значение .коэффициента. После этого устройством учитываются компенсация по первой и второй производным и полученное сглаженное значение входного сиг нала передается из блока 2 в блок 1. В дальнейшем работа пре лагаемого диффе)енцирую1пе-сглаживаю1цего уст ройства протекает аналогичным образо Сокращение времени выполнения опе раций дифференцирования позволяет со ратить общие затраты маишнного време ни и за счет этого получить значител ную экономию. Формула изсэбретения 1 . Дифференцирую;пе-сглаживаюшее устройство, содержсидее блок оператив ной памяти, блок вичисления спектральных коэффициентов, первый сдвиг вый регистр, блок управления, блок формирова ия адресов и дтза блока сра нения, прзичем вход устройства соединен с перв,1м входом блока оперативно памяти, выход которого подключен к в 6 8 ходу устройства и к первому входу блока вы исления спектральных коэффициентов, первый выход которого подключен к первым входам двух блоков сравнения и к первому входу первого сдвигового регистра, второй вход которого подключен к первому ых .);;у блока управления, второй, TCCTijjj з четвертый выходы которого мо.а ;лючены соответственно ко второму, третьему и четвертому нхоцам блока вычисления спектральных коэффициентов, выходы блока управления с пятого по девятый подключены соответственно к пяти входам блока формирования адресов, два выхода которого подключены соответственно к двух управляющим входам блока оперативной памяти, выходы обоих блоков сравнения подключены к первым двум входам блока управления, отличающееся тем, что, с целью повышения быстродействия, оно содержит второй сдвиговый регистр, первый вход которого подключен к выходу блока оперативной памяти, второй вход - к десятому выходу блока управления, а выход - к третьему входу блока управления, четвертый вход которого подключен ко второму выходу блока вычисления спектральных коэффициентов , пятый вход которого подключен к выходу первого сдвигового регистра, а первый выход - ко второму входу блока оперативной памяти. 2.Дифференцирующе-сглаживающее устройство по П.1, о тли ч ающ е е с я тем, что блок вычисления спектральных коэффициентов содержит сумг атор-вы штатель, генератор функций Радемахера, коммутатор, два элемента И, причем первый вход блока вычисления спектральных коэффициентов подключен к первому входу сумматоравычитателя, выход которого соединен с первым выходом блока вычисления .спектральных коэффициентов, второй вход которого подключен к первому входу коммутатора, первый и второй выходы которого соединены с первыми входами соответствующих элементов И, выходы которых подключены ко второму и третьему входам сумматора-вычитателя, четвертый вход которого соединен с пятым входом блока вычисления спектральных коэффициентов, третий вход которого подключен ко вторым входам обоих элементов И, а четвертый вход блока - ко входу генератора функций Радемахера, шесть прямых и инверсных выходов которого с последних трех разрядов соединены с шестью управляющими входами коммутатора, третий выход которого подключен ко второму выходу блока. 3.Дифференцирующе-сглаживающее устройство по п.2, о т л и ч а ю щ ее с я тем, что коммутатор содержит десять элементов И и пять элементов ИЛИ, причем первый вхол коммутатора 96 соединен с первыми входами первых двух элементов И, а второй вход - с первыми входами третьего и четвертого элементов И, выходы первого, второго, третьего и четвертого элементов И подключены к соответствую цим входам первого и второго элементов И прямые выходы первого и второго элементов ИЛИ соединены соответственно с первым и вторым выходами коммутатора, а инверсные выходы первого и второго элементов ИЛИ через третий элемент ИЛИ подключены к третьему выходу коммутатора, первый управляющий вход которого соединен с первыми входами п того и шестого элементов И, второй управляющий вход коммутатора подключен к первым входам седьмого и восьмого элементов И, третий управляющий вход коммутатора соединен со вторыми входами пятого и восьмого элементов четвертый управляющий вход коммутато ра подключен ко вторым входам шестог и седьмого элементов И, выходы пятого и седьмого элементов И соединены со вторыми входами соответственно третьего и четвертого элементов И и с первыми входами соответственно девятого и десятого элементов И, выходы которых через четвертый элемент ИЛИ подключены ко второму входу второго элемента И, а вторые входы девятого и десятого элемента И соединены соответственно с пятым и шестьгл управляющими входами коммутатора, эти же входы которого подключены к третьим входам соответственно восьмого и шестого элементов И, выходы которых через пятый элемент ИЛИ соединены со вторым входом первого элемента И. Источники информации, принятые во внимание при экспертизе: 1.Авторское свидетельство СССР, № 355618, кл. G06 F 7/38, 16.03.71. 2.Авторское свидетельство СССР № 377785, кл. G06 F 15/32, 05.08.70.

| название | год | авторы | номер документа |

|---|---|---|---|

| Дифференцирующе-сглаживающее устройство | 1975 |

|

SU610115A1 |

| Устройство для выполнения быстрого преобразования Фурье | 1983 |

|

SU1159031A2 |

| Дифференцирующе-сглаживающее устройство | 1974 |

|

SU714404A1 |

| Специализированный процессор обработки данных | 1982 |

|

SU1062715A1 |

| Устройство для анализа характеристик спектра | 1983 |

|

SU1142844A1 |

| Устройство для вычисления коэффициентов дискретного преобразования Хаара | 1982 |

|

SU1061151A1 |

| Устройство для вычисления спектра Фурье | 1983 |

|

SU1121678A1 |

| Дифференцирующе-сглаживающее устройство | 1975 |

|

SU577531A1 |

| Устройство для обращения матриц | 1988 |

|

SU1647591A1 |

| Анализатор спектров | 1982 |

|

SU1023341A1 |

I

Фиг.г

фцг.З

Авторы

Даты

1978-12-05—Публикация

1976-10-29—Подача