рой коммутаторы, сдвиговый коммутатор и блок нормализации, первый выход которого соединен с входами разрядов порядка выходного регистра первым входом первого коммутатора и входом вычитаемого вычитателя порядков, выход знакового разряда которого подключен к второму вхрду первого ком1 татора и первому входу второго коммутатора, первый выход которого соединен с входом сдвигового коммутатора, выход которого соединен с первым входом сумматора, второй вход которого подключен к выходу второго коммутатора, второй вход которого соединен с информационным выходом первого регистра, .информационный .выход входного регистра подключен к информационным входам регистров пятой труппы, информационные выходы которых соединены с информационными входами регистров пятой группы, входом первого уменьшаемого вычитателя порядков, третьим входом первого коммутатора и информационными входами регистров шестой группы, информационные выходы которых подключены к первому входу сумматора порядков, выход которого соединен с информационным входом второго регистра, информационный выход которого подключен к входу второго уменьшаемого илчитателя порядков и четвертому входу первого коммутатора, выход которого соединен с информационными входами регистров седьмой группы, информационные выходы которых подключены к первому входу блока нормализации, второй выход которого .соединен с разрядгиии мантиссы выходного регистра и третьим входом четвертого коммутатора, четвертый вход которого подключен к информационным выходам регистров первой группы, информационный выход входного регистра соединен с информационными входами регистров восьмой группы, информационные выходы которых соединены с вторым входом сумматора порядков, выход разрядов числа вычитателя порядков соединен с управляющим входом сдвигового ко1имутатора, информационные выходы регистров четвертой группы соединены с вторым входом блока нормализации, причем блок управления содержит генератор импульсов, первый и второй триггеры, элемент ИЛИ, элемент И, дешифратор кода операции , первый и второй распределители импульсов, группу элементов И и группу элементов ИЛИ, выход дешифратора кода операций соединен с первыми входами элементов И группы и входами элемента ИЛИ, выход которого подключен к входу первого

триггера, выход которого, соединен с первым входом элемента И, выход, которого подключен i входам первого и второго распределителей импульсов , выходы которых соединены соответственно с вторым и третьим входами элементов И группы, выходы которых подключены соответственно к входам элементов ИЛИ группы, выход второго триггера соединен с вторым входом элемента И, третий вход которого подключен к выходу генератора импульсов, выход первого элемента ИЛИ группы соединен с управляющими входами регистров первой и пятой групп, выход второго элемента ИЛИ группы соединен с управляющими входами регистров второй и восьмой групп, выход третьего элемента ИЛИ группы соединен управлякицими входами регистров третьей и шестой трупп, выход четвертого элемента ИЛИ группы подключен к управляющему входу умножитея, выход пятого элемента ИЛИ соеинен с входом разрешения приема второго уменьшаемого вычитателя, выход шестого и седьмого элементов ЛИ подключены к управляющим вхоам соответственно первого и втоого коммутаторов, выход восьмого лемента ИЛИ группы соединен с вхоом разрешения приема первого меньшаемого вычитателя, выход девятого элемента ИЛИ группы подключен к управляющим входам регистров четвертой и седьмой групп, выход первого распределителя импульсов блока управления соединен с входом коммутатора адресных сигнгшов, информационный выход счетчика циков подключен к входу второго триггера блока управления, выход блока сравнения соединен с четвертым входом последнего элемента И группы блока управления, информационный выход регистра кода операции подключен к входу дешифратора кода операции блока управления,

2. Устройство по п. 1, отличающееся тем, что блок нормализации содержит сумматор порядков, кс 1мутатор, шифратор и сдвиговый коммутатор, выход коммутато-i а соединен с входом шифратора, выход которого подключен к упвавяющему входу сдвигового коммутатора и первому входу сумматора порядков , первый вход которого является первым входом блока нормализации,

входы разрядов сдвигового кокпчутатора объединены с входами разрядов коммутатора и являются вторым входом блока нормализации, причем управляющие входы коммутатора объединены с входами первых двух разрядов коммутатора, выход сумматора

порядков.и выход сдвигового коммутатора являются соответственно

первым и вторым выходами блока нормализации.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для вычисления элементарных функций | 1983 |

|

SU1145340A1 |

| Специализированный процессор | 1983 |

|

SU1144117A1 |

| Устройство для вычисления функции синуса | 1987 |

|

SU1474642A1 |

| Арифметическое устройство | 1989 |

|

SU1656525A1 |

| Арифметическое устройство | 1984 |

|

SU1193661A1 |

| Устройство для умножения и деления с плавающей точкой | 1985 |

|

SU1278837A1 |

| Устройство для сложения и вычитания чисел с плавающей запятой | 1980 |

|

SU959070A1 |

| Арифметическое устройство с плавающей точкой | 1985 |

|

SU1259248A1 |

| Вычислительное устройство | 1988 |

|

SU1545215A1 |

| Устройство для формирования спектров с постоянным относительным разрешением по направлениям | 1984 |

|

SU1229775A1 |

1. СПЕЦИАЛИЗИРОВАННЫЙ ПРОЦЕССОР ОБРАБОТКИ ДАННЫХ, содержащий четыре группы регистров, входной регистр, выходной регистр, умножитель, сумматор, регистр, три счетчика адреса, первый регистр кода операций, регистр числа операций, счетчик циклов, два счетчика текущих значений адреса, коммутатор адресных сигналов, блок сравнения, регистр адреса, счетчик числа операций, блок управления, информационный выход входного регистра соединен с инфор1-1ационными входаьш. регистров первой и второй групп, информационные выходы которых подключены к информационным входам регистров соответственно первой и второй групп, информационные выходы регистров первой группы подключены к информационным выходам регистров третьей группы, информационные выходы которых соединены с первым входом умножителя, выход которого подключен к информационному входу регистра, информационные выходы регистров второй группы соединены с вторым входом умножителя, информационный выход входного регистра подключен к ;информационному входу регистра кода операции, информационным входам трех счетчиков адреса, информационному входу счетчика циклов и информационному входу регистра числа операций, информационный выход которого подключен к первому входу блока сравнения,, второй вход которого соединен с информационным выходом счетчика числа операций, информационные выходы первого и второго счетчиков адреса соединены с информационными входами соответственно первого и второго счетчиков текущих значений адреса, информационные выходы которых подключены к информационному входу регистра адреса, информационный выход которого является выходом адреса процессора, СЛ первый выход коммутатора адресных сигналов соединен с управляющими, входами двух счетчиков текущих значений адреса и счетчика числа операций, второй выход коммутатора адресных сигналов подключен к управляющему входу регистра адреса, информационный вход которого соединен с информационным выходом третьего счетчика адреса, управляющий вход которого подключен к третьему выходу коммутатора адресных сигналов, четвертый выход которого соединен с управляющими входами первого и второго счетчиков адреса, пятый выход крммутатора адресных сигналов подключен к управлякицему входу счетчика циклов, информационный вход входного регистра и информационный выход выходного регистра являются соответственно информационным входом и информационным выходом процессора, отличающий ся тем, что, с целью повышения точности, в него введены пятая, шестая, седьмая и восьмая группы регистров, сум матор порядков, второй регистр, вычитатель порядков, первый и ато

Изобретение относится к вычислительной технике и предназначено для обработки массивов данных при решении задач спектрального анализа.

Известно устройство для выполнения быстрого преобразования Фурье, содержащее четыре входных регистра, регистры комплексной весовой функции, коммутатор сомножителей, блок управления, блок умножения, регистры произведений, коммутатор слагаемых, сумматор, регистры сумкы СП.

Данное устройство не позволяет /обрабатывать массивы данных с высокой точностью, т.е. в формате с плавающей запятой.

Наиболее близким к предлагаемому является устройство, содержащее вхоной регистр, вход которого является входом устройства, а выход подключен к первым входам первого и второто блоков регистров стекового типа, первого, второго и третьего счетчиков адреса, счетчика циклов, к входс1м регистра кода операции и егистра числа операции, выход которого подключен к первому входу схемы сравнения, вторые входы первого и второго счетчиков адреса, первые входы первого и второго счетчиков текущего адреса, вторые входа третьего счетчика адреса и счетчика цилов, вход счетчика числа операций соединены с 5выходами коммутатора адресных сигналов, выход счётчика числа операций соединен со вторым входом схемы сравнения, выходы первого и второго счетчиков адреса соединены с вторыми входами первого и второго счетчиков текущего адреса, выходы которых и выход третьего счетчика гщреса подключены к первому, второму и третьему входам регистра адреса, выход которого является адресным выходом устройства, а четвертый вход соединен с выходом коммутатора адресных сигналов, выход первого блока регистров стекового типа соединен со своим вторым входом и с информационным входом третьего блока регистров стекового типа, выход второго блока регистров стекового типа соединен со CBOHKJ вторым входом и с первым входом перемнсэжителя, второй вход которого соеданен с выходом третьего блока регистров стекового типа, выход перемножителя соединен с входом первого промежуточного регистра, выход сумматора соединен с информационным входом четвертого блока регистров стекового типа, выход выходного регистра является информационным выходом устройства, входы блока управления соединены ,с выходом

0 регистра кода операции и с выходами схема сравнения и счетчика циклов, выходы блока управления соединены с управляющими входами блоков регистров стекового типа и перемножителя C2J.

5

Недостатком этого устройства является то, что в нем массивы данных могут обрабатываться только в

0 формате с фиксированной запятой. В этом случае оно эффективно при обработке однородных массивов, характеризующихся небольшим динамическим диапазоном. Обработка неод5нородных массивов данных с большим динамическим диапазоном в формате с фиксированной запятой связана с большими пограиностями. Кроме того, при выполнении алгоритма быстрого :

0 преобразования Фурье в формате с фиксированной запятой результат умножения исходных данных на значения синусно-косинусной матрицы получается двойной длины. Для полу5чения результата той же разрядности , что имеют входные данные, применяется маскирование - выделение старших разрядов результата. Старший значащий разряд при этом задается nporpaNMiCTOM. Возможны ситу0ации, при которых значащими разрядами результата будут несколько мпадиих разрядов, а остальные разряды будут иметь нулевое значение. Маскирование такого результата и

5 использование его в качестве исходных данных для последующего этапа ВПФ приводит к искажению реаль- , ного массива, который подвергается анализу. Во избежание этого в

0 устройстве при выполнении операции БПФ -росле каждого этапа обработки необходимо проводить сдвиг результата влево с запоминанием количества сдвигов. Выполнение указанных

5 процедур требует и дополнительного . Оборудования, и усложнения математического обеспечения. Целью изобретения является повы шение точности обработки дацных. Поставленная цель достигается тем, что в специализированный процессор обработки данных, содержащи четыре группы регистров, входной регистр, выходной регистр, умножитель, сумматор, регистр, три сче чика адреса, первый регистр кода операций, регистр числа операций, счетчик циклов, два счетчика текущих значений адреса, ко1 мутатор ад ресных сигналов, блок сравнения,, регистр .адреса, счетчик числа опер ций, блок управления, информационн выход входного регистра соедийен с информационными входами регистров первой и второй групп, информационные выходы которых подключены к информационным входам регистров соответственно первой и второй групп, информационные выходы регист ров первой группы подключены к информационным выходам регистров третьей группы, информационные выходы которых соединены с первым входом умножителя, выход которого подключен к информационному входу регистра, информационные выходы рёги ров второй группы соединены с вторым входом умножителя, информационный выход входного регистра подключен к инс юрмаци:онному входу регистра кода операции, информационным входам трех счетчиков адреса, инфор мационному входу счетчика циклов , и информационному входу регистра числа операций, информационный выход которого подключен к первому входу блока сравнения, второй вход которого соединен с информационным выходом счетчика числа операций, информационные выходы первого и вто рого счетчиков адреса соединены с информационными входами соответс венно первого и второго счетчиков текущих значений адреса, информационные выходы которых подключены к информсщионному входу регистра адреса, информационный выход которого является исходом адреса процессора, первый выход коммутатора адресных сигналов соединен с управляющими входами двук счетчиков текущих значений адреса и счетчика числа операций, второй выход комму татора адресных стгналов подключен к управляющему входу регистра адреса, информационный вход которо го подсоединен к информационному выхо ду третьего счетчика адреса, управ ляющий вход которого подключен к т тьему выходу коммутатора адресных сигналов, четвертый выход которого со1динен с управляющими входами первого и второго счетчиков адреса, пятый выход коммутатора адресных сигналов подключен к управляющему входу счетчика циклов, информационный вход входного регистра и информационный выход выходного регистра являются соответственно информационным входом и информационным выходом процессора, введены , шестая, седьмая и восьмая группы регистров, сумматор, порядков, второй регистр, вычитатель порядков, первый и второй коммутаторы, сдвиговый коммутатор и блок нормализации,, перв.ый выход которого соединей с входами разрядов порядка выходного регистра, первым входом первого коммутатора и входом вычитаемого вычитателя порядков, .выход знакового разряда которого подключен к второму входу первого коммутатора и первому входу второго коммутатора, первый выход которого соединен с входом сдвигового коммутатора, выход которого соединен с первым входом сумматора, второй вход которого подключен к выходу второго коммутатора, второй вход которого соединен с ин-. формационным выходом первого регистра, информационный выход входного регистра подключен к инфорМсщионным входам регистров пятой группы, информационные выходы которых соединены с информационными входами регистров пятой группы, ВХОДОМ первого уменыиаемого вычитателя порядков, третьим входом первого коммутатора и информационными входами регистров шестой группы, информационные выходы которых подключены к первому входу сумматора порядков, выход которого соединён с инфор -1ационным входом второго регистра, информационный выход которого подключен к входу второго уменьшаемого вычитателя порядков и четвертому вхоДу первого коммутатора, выход которого соединен с информационными входами регистров седьмой группы, информационные, выходы которых подключены к первому входу блока нормализации, второй выход которого соединен с, разрядами мантиссы выходного регистра и третьим входом четвертого коммутатора, четвертый вход которого подключен к информационным выходам регистров первой группы, информационный выход входного регистра соединен с информационными входами регистров восьмой группы, информационные выходы которых соединены с вторым входом сумматора порядков, выход разрядов числа вычитателя порядков соединен с управлякхцим входом сдвигового коммутатора, ииформационные выходы регистров четверToft группы соединены с вторым входом блока нормализации, причем блок управления содержит генератор импульсов, первый и второй триггеры, элемент ПЛИ, элемент И, дешифратор кода операции, первый и второй распределители импульсов, группу элёменгов И и группу элементов ИЛИ, выход дешифратора кода операций соединен с первыг.и входами элементов И группы и входами элемента ИЛИ, выход которого подключен к входу первого триггера, выход которого соединен с первым входом элемента И, выход которого подключен к входам первого и второго распределителей иг тульсов, выходы которых соединены.соответственно с вторым и третьим входами элементов И группы, выходы которых подключены соответственно к входам элементов НЛН группы, выход второго триггера соединен с вторым входом элемента И, третий вход которого подключен к выходу генератора импульсов, выход первого элемента ИЛИ -группы соединен с управляющими входами регистров первой и пятой групп, выход второго элемента ИЛИ группы соединен с управляющими входами регистров второй и восьмой групп, выход третьего элемента ИЛИ группы соединен с управляюгцимк входами

.регистров третьей и шестой групп, выход, четвертого элемента ИЛИ группы подключен к управляющему входу умножителя, выход пятого элемента ИЛИ соединен с входом разрешения приема второго уменьшаемого вычитателяу выход шестого и седьмого элементов ИЛИ подключены к управляющим соответственно первого и второго коммутаторов, выход восьмого элемента ИЛИ группы соединен с входом разриаения приема первого уменьшаемого вычитателя выход девятого элемента ИЛИ группы подключен к управляющим входам регистров четвертой и седьмой групп, выход первого распределителя импульсов блока управления с входом коммутатора адресных сигналов, информационный выход счетчика циклов подключен к входу второго триггера блока управления, выход блока сравнения соединен с четвертым входом последнего элемента И группы блока управления, а информационны выход регистра кода опера.ции подключен к входу дешифратсфа кода операции блока управления.

Кроме того, блок нормализации содержит сумматор порядков, коммутатор, шифратор и сдвиговой коммутатор, выход коммутатора соединен с входом шифратора, выход которого подключен к управляющему входу

сдвигового коммутатора и первому входу сумматора порядков, первый вход которого является первым входом блока нормализации, входы разрядов сдвигового коммутатора объединены с входами разрядов коммутатора и

являются вторым входом блока нормализации, причем управляющие входы коммутатора объединены с входами первых двух разрядов коммутатора, выход сумматора порядков и выход сдвигового коммутатора являются соответственно первым и вторым выходами блока нормализации.

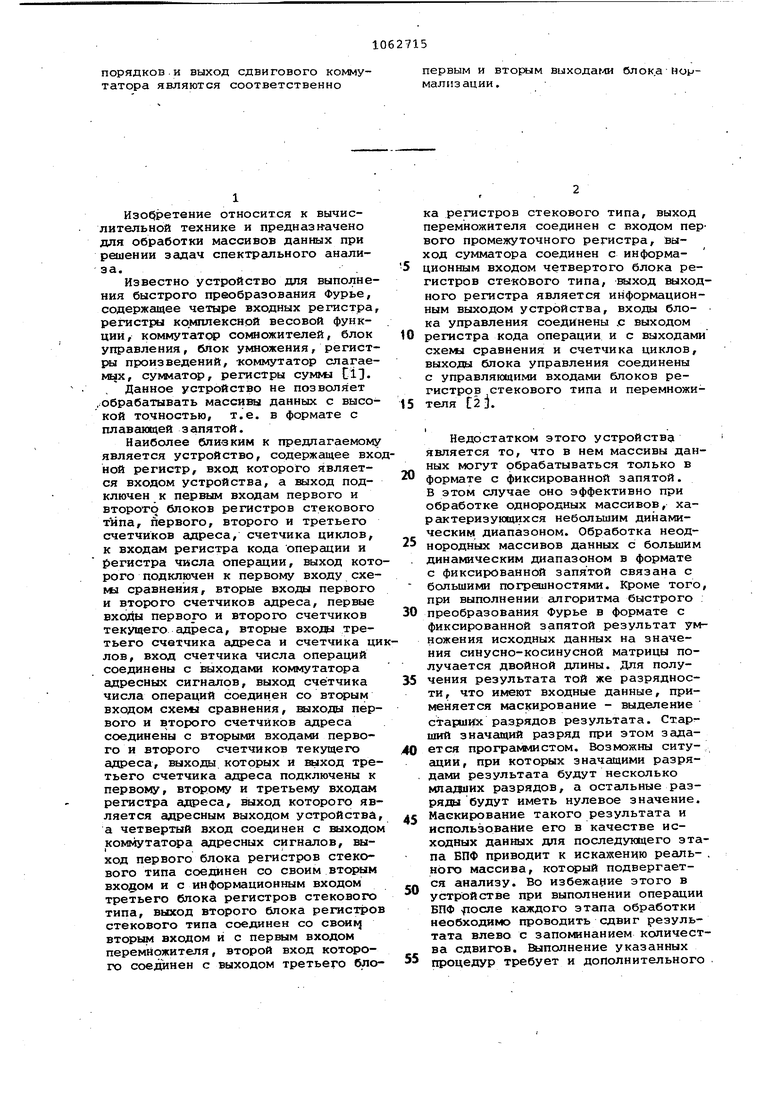

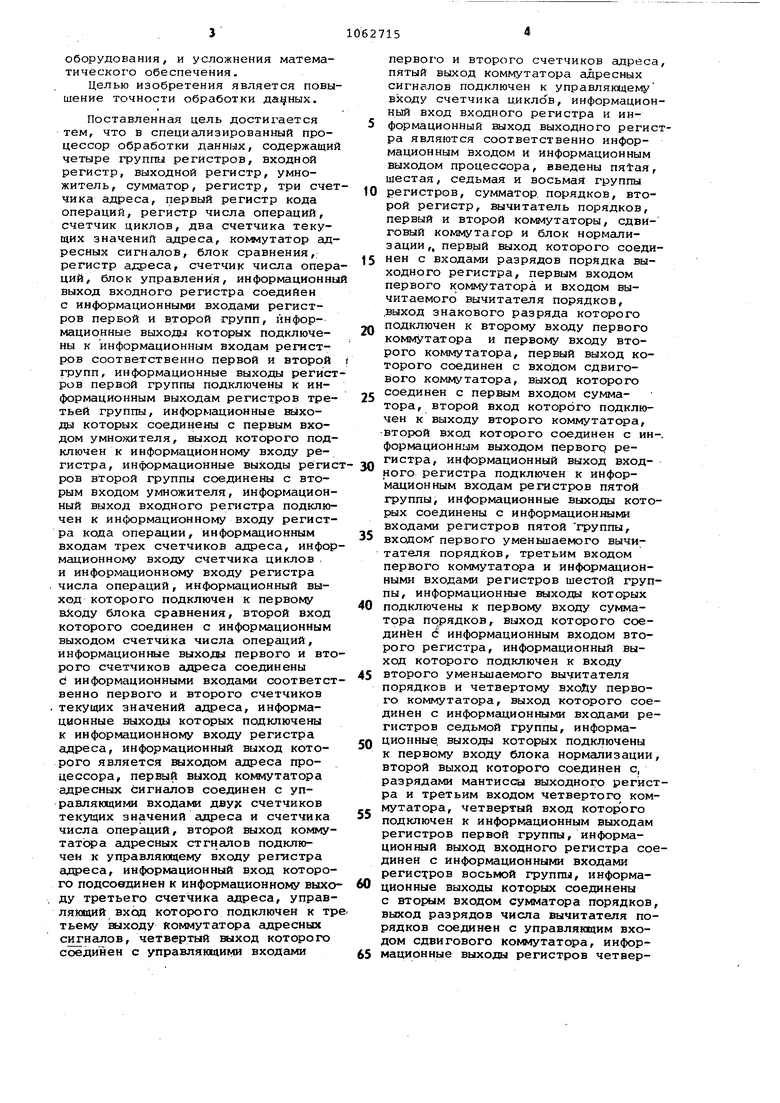

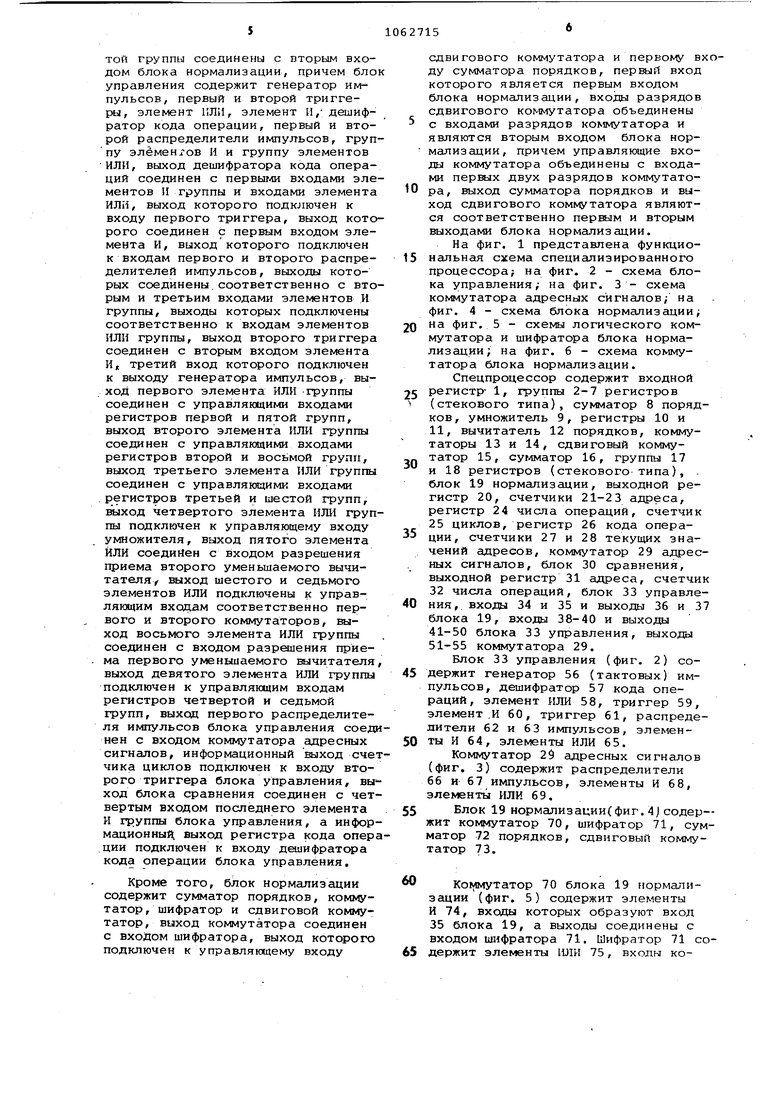

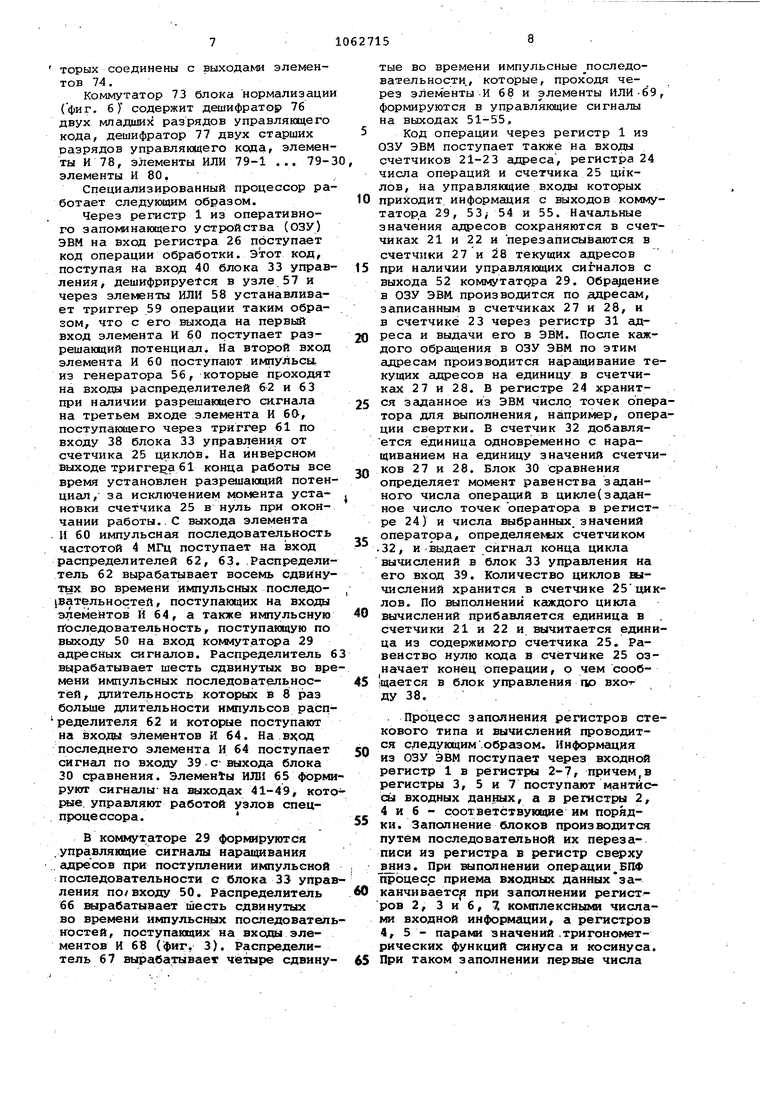

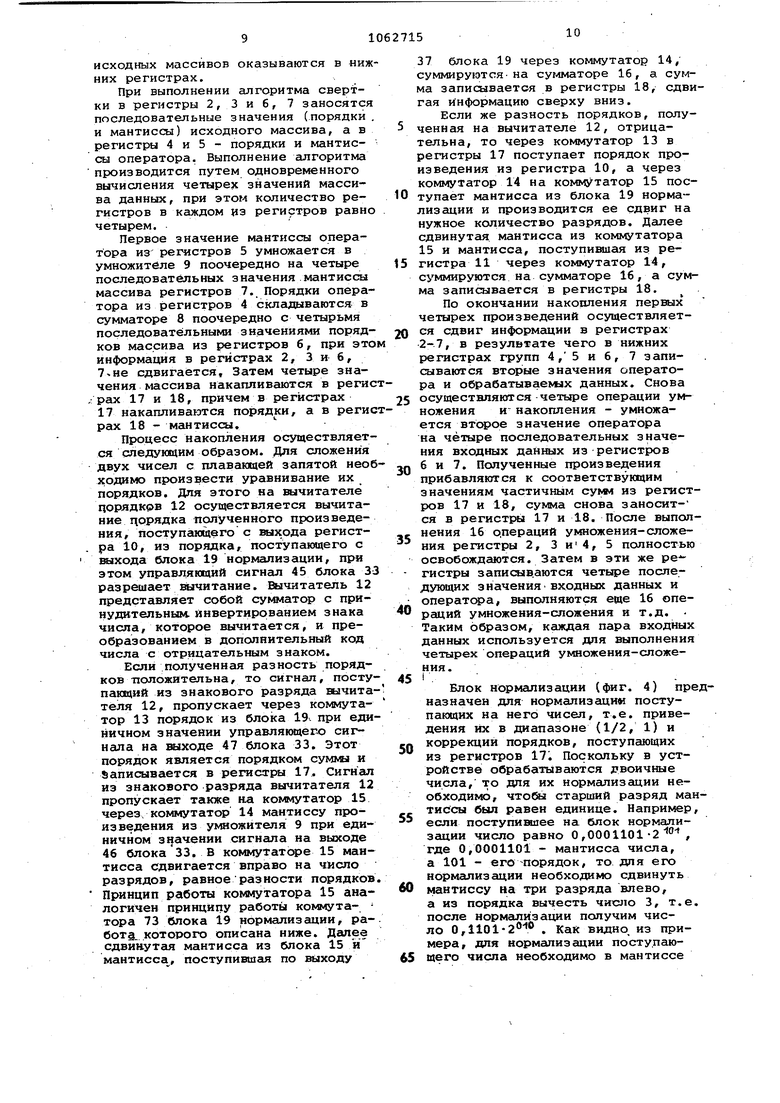

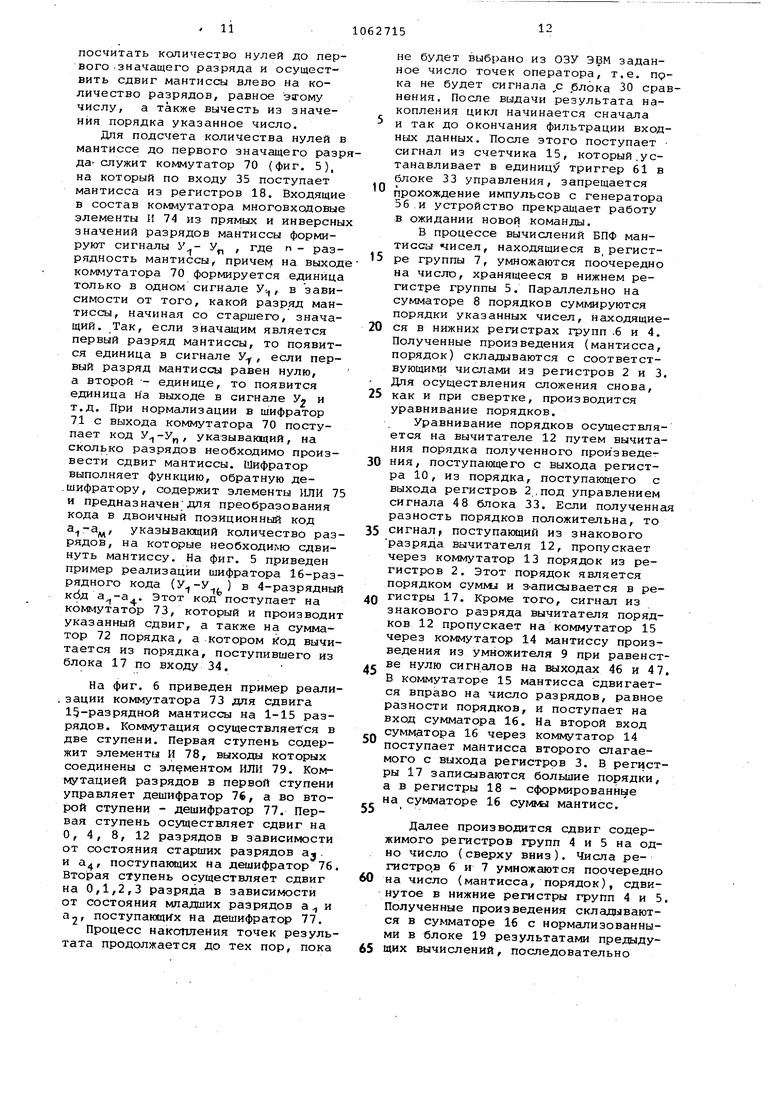

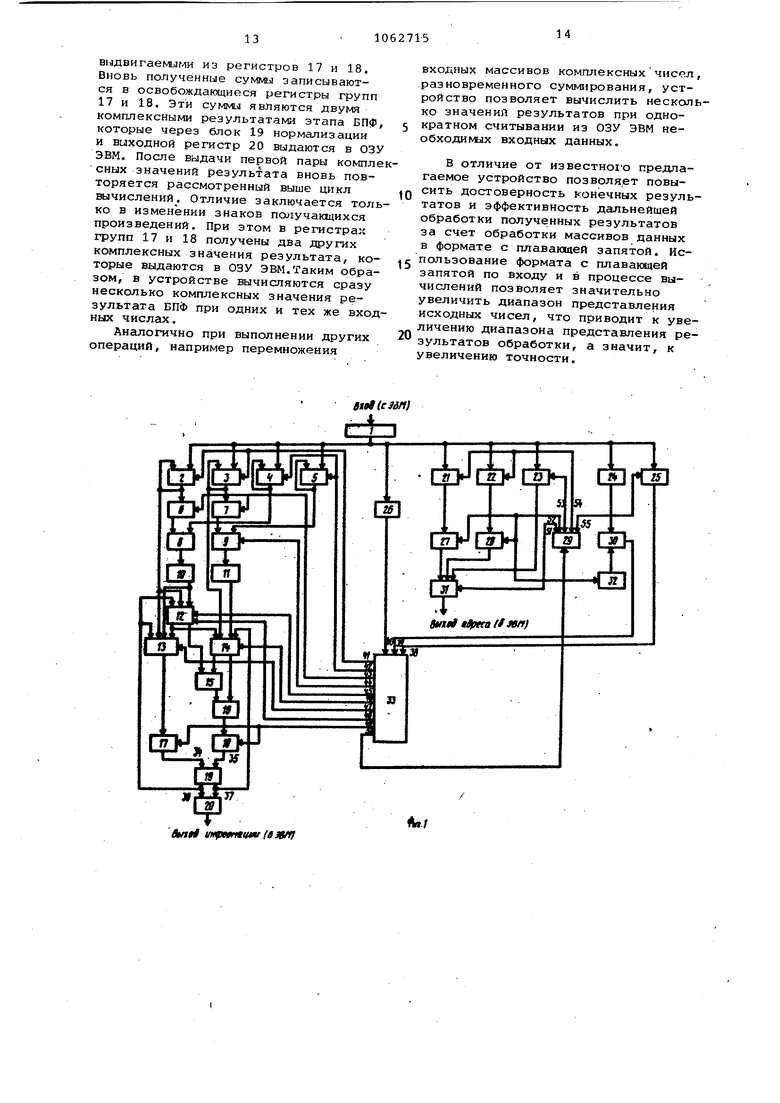

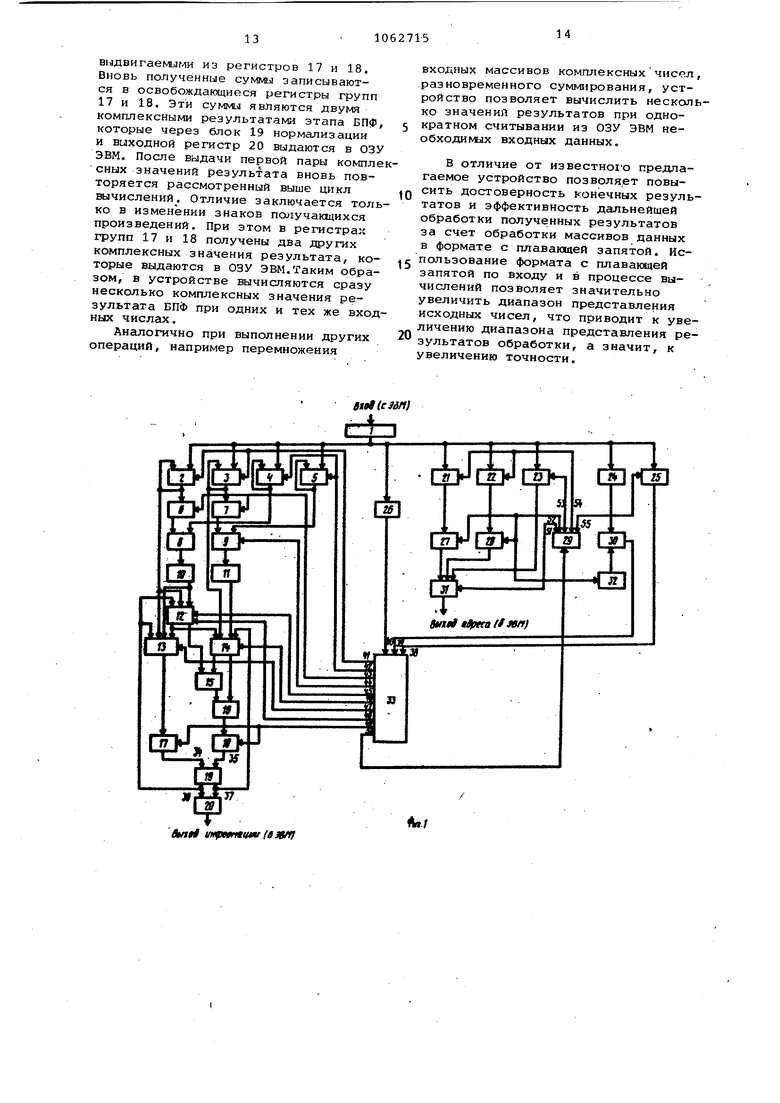

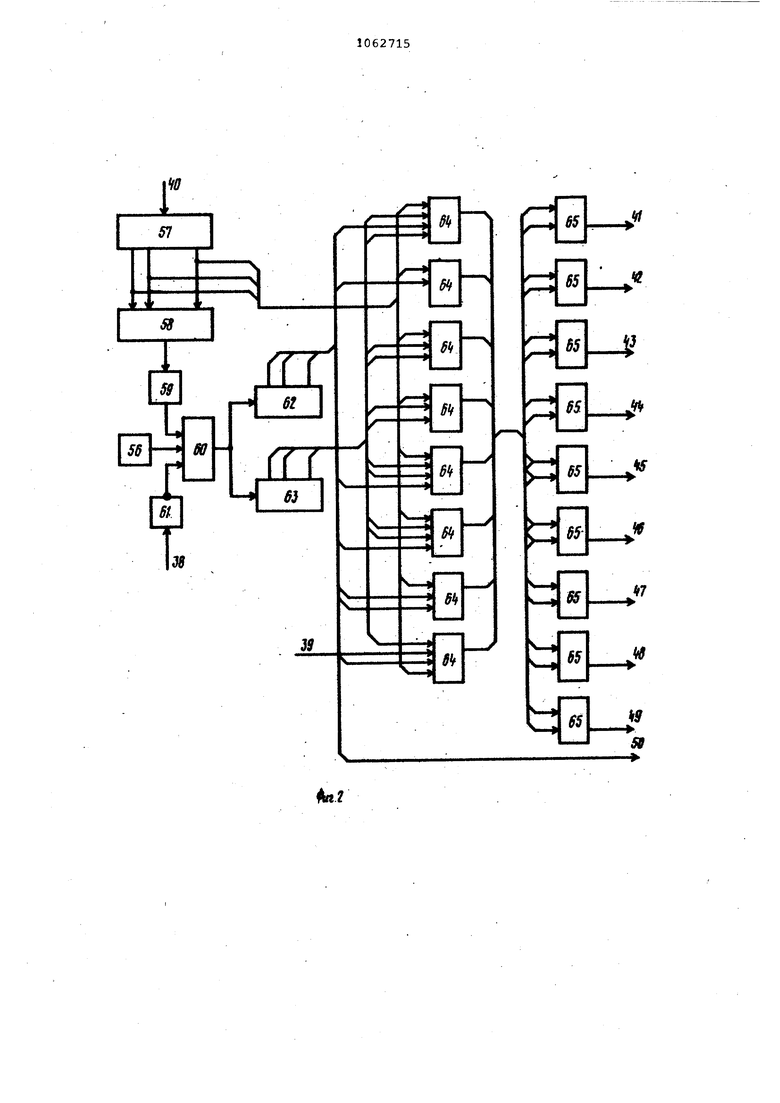

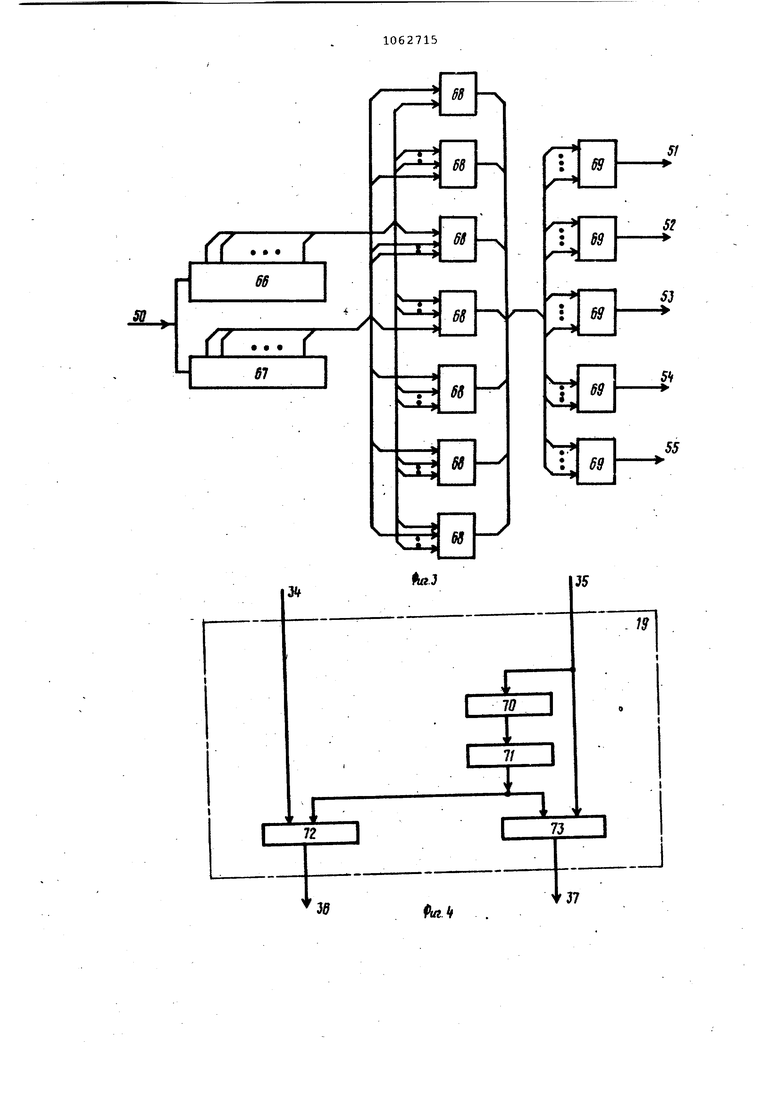

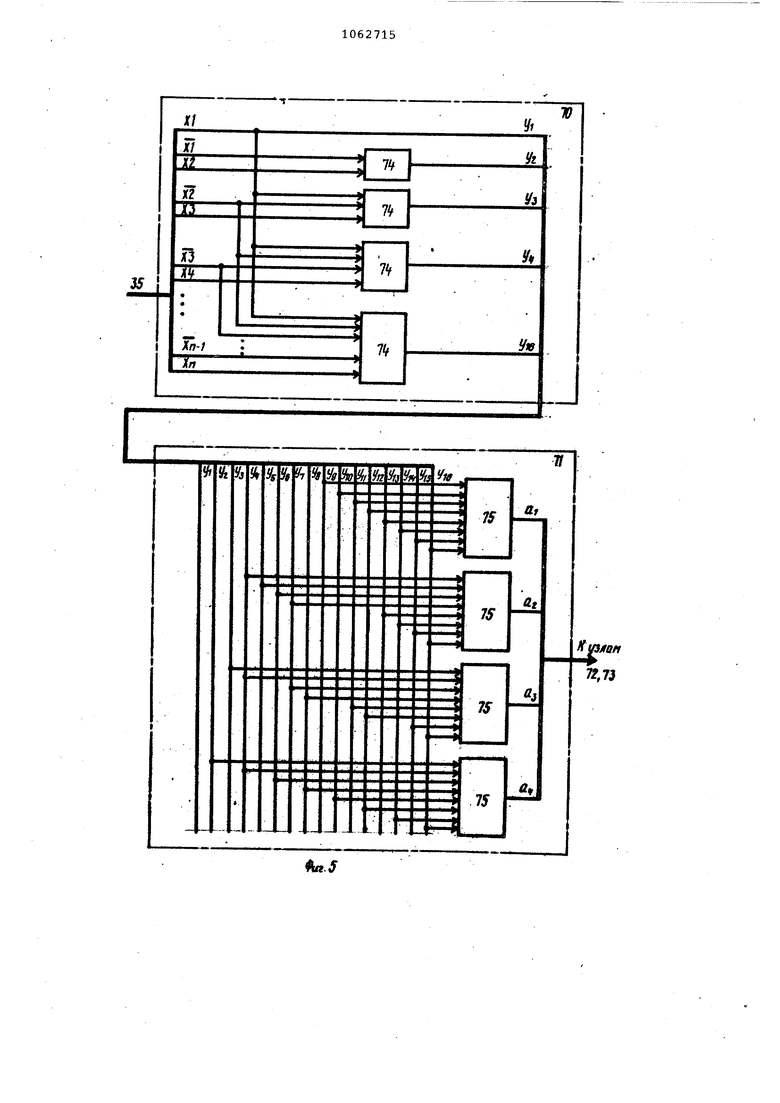

На фиг. 1 представлена функциональная схема специализированного процессора; на фиг, 2 - схема блока управления; на фиг. 3 - схема коммутатора адресных сигналов; на фиг. 4 - схема блока нормализации;

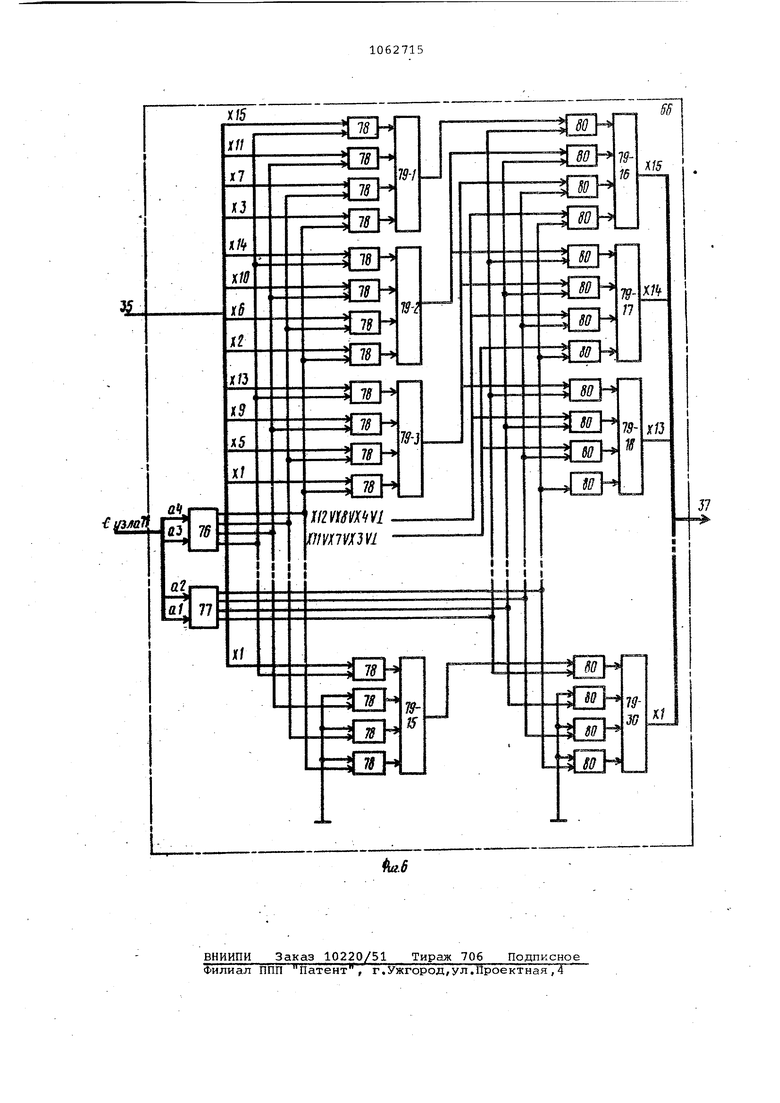

на фиг. 5 - схемы логического коммутатора и шифратора блока нормализации; на фиг. 6 - схема коммутатора блока нормализации.

Спецпроцессор содержит входной

регистр- 1, группы 2-7 регистров (стекового типа), сумматор 8 порядков, умножитель 9, регистры 10 и 11, вычитатель 12 порядков, коммутаторы 13 и 14, сдвиговый коммутатор 15, суглматор 16, группы 17 и 18 регистров (стекового типа), . блок 19 нормализации, выходной регистр 20, счетчики 21-23 адреса, регистр 24 числа операций, счетчик 25 циклов, регистр 26 кода операции, счетчики 27 и 28 текущих значений адресов, коммутатор 29 адресных сигналов, блок 30 сравнения, выходной регистр 31 адреса, счетчик 32 чи.сла операций, блок 33 управлеНИН,, входы 34 и 35 и выходы 36 и 37 блока 19, входы 38-40 и выходы 41-50 блока 33 управления, выходы 51-55 коммутатора 29.

Блок 33 управления (фиг. 2) содержит генератор 56 (тактовых) импульсов, дешифратор 57 кода операций, элемент ИЛИ 58, триггер 59, элемент,И 60, триггер 61, распределители 62 и 63 импульсов, элементы И 64, элементы ИЛИ 65.

Коммутатор 2 адресных сигналов (фиг, 3) содержит распределители 66 и 67 импульсов, элементы И 68, элементы ИЛИ 69.

Блок 19 нормапизации(фиг.4jсодер-жит коммутатор 70, шифратор 71, сумматор 72 порядков, сдвиговый коммутатор 73.

KoffiMyTaTop 70 блока 19 нормализадии (фиг, 5) содержит элементы И 74, входы которых образуют вход 35 блока 19, а выходы соединены с входом шифратора 71. Шифратор 71 содержит элементы Ш1И 75, входы ко торых соединены с выходами элементов 7-4. Коммутатор 73 блока нормализаци (фиг. 6) содержит дешифратор 76 двух младших разрядов управляющего кода, дешифратор 77 двух старших разрядов управляющего кода, элемен ты И 78, элементы ИЛИ 79-1 ... 79элементы И 80, Специализированный процессор ра ботает следующим образом. Через регистр 1 из оперативного запокмнающего устройства (ОЗУ) ЭВМ на вход регистра 26 поступает код операции обработки. Этот код, поступая на Bxofl 40 блока 33 управ ления, дешифрируется в узле 57 и через элементы ИЛИ 58 устанавливает триггер 59 операции таким образом, что с его выхода на первый вход элемента И 60 поступает разрешающий потенциал. На второй вход элемента И 60 поступают импульсы, из генератора 56, которые проходят на входы распределителей 62 и 63 при наличии разрешающего сигнала на третьем входе элемента И 60, поступакмаего через триггер 61 по входу 38 блока 33 управления от счетчика 25 циклив. На инверсном выходе триггера 61 конца работы все время установлен разрешающий потен циал, за исключением мокента установки счетчика 25 в нуль при окончании работы.. С выхода элемента . И 60 импульсная последовательность частотой 4 МГц поступает на вход распределителей 62, 63. Распредели тель 62 вырабатывает восемь сдвину тых во времени импульсных последо(Вательностей, поступающих на входы элементов И 64, а также импульсную последовательность, поступающую по выходу 50 на вход KOf iyTaTopa 29 адресных сигналов. Распределитель вырабатывает шесть сдвинутых во вр мени импульсных последовательноетёй, длительность которых в 8 раз больше длительности импульсов расп ределителя 62 и которые поступают на входы элементов И 64. На вход последнего элемента И 64 поступает сигнал по входу 39.с-выхода блока 30 сравнения. Элемен1гы ИЛИ 65 форм руют сигналы-на выходах 41-49, кот 1жге. управляют работой узлов спецпроцессора. В коммутаторе 29 формируются .управляющие сигналы наращивания адресов при поступлении импульсной последовательности с блока 33 упра ления по/входу 50. Распределитель 66 ш рабатывает шесть сдвинутых во времени импульсных последовател ностей, поступающих на входы элементов И 68 (фиг. 3), Распределитель 67 вырабатывает четыре сдвину тые во времени импульсные последовательности,, которые, проходя через элементы .И 68 и элементы ИЛИ-69, формируются в управлякнцие сигна.лы на выходах 51-55, Код операции через регистр 1 из ОЗУ ЭВМ поступает также на входы счетчиков 21-23 адреса, регистра 24 числа операций и счетчика 25 циклов, на управляющие входы которых приходит, информация с выходов коммутатора 29, 53; 54 и 55. Начальные значения адресов сохраняются в счетчиках 21 и 22 и перезаписываются в счетчики 27 и 28 текущих ащресов при наличии управляющих сигналов с выхода 52 коммутатрра 29. Обра}цение в ОЗУ ЭВМ. производится по адресам, записанным в счетчиках 27 и 28, и в счетчике 23 через регистр 31 адреса и выдачи его в ЭВМ. После каждого обращения в ОЗУ ЭВМ по этим адресам производится наращивание текущих адресов на единицу в счетчиках 27 и 28. В регистре 24 хранится заданное из ЭВМ число точек оператора для выполнения, например, операции свертки. В счетчик 32 добавляется единица одновременно с наращиванием на единицу значений счетчиков 27 и 28. Блок 30 сравнения определяет момент равенства заданного числа операций в цикле(заданное число точек оператора в регистре 24) и числа выбранных, значений оператора, определяемых счетчиком 32, и выдает сигнал конца цикла вычислений в блок 33 управления на его вход 39. Количество циклов вычислений хранится в счетчике 25циклов. По выполнении каждого цикла вычислений прибавляется единица в . счетчики 21 и 22 и вычитается единица из содержимого счетчика 25. Равенство нулю кода в счётчике 25 означает конец операции, о чем сообщается в блок управления по вхоДУ 38. Процесс заполнения регистров стекового типа и вычислений проводится следующим .образом. Информация из ОЗУ ЭВМ поступает через входной регистр 1 в регистры 2-7, причем,в регистры 3, 5 и 7 поступгиот мантиссы входных данных, а в регистры 2, 4 и 6 - соответствующие им порядки. Заполнение блоков производится путем последовательной их перезаписи из регистра в регистр сверху вниз. При выполнении операции БПФ процесс приема входных данныхзаканчиваете при заполнении регистров 2, 3 и 6, 1 комплексными числами входной информации, а регистров 4, 5 - парами значений.тригонометрических функций синуса и косинуса. При таком заполнении первые числа

исходных массивов оказываются в нижних регистрах.

При выполнении алгоритма свертки в регистры 2, 3 и б, 7 заносятся последовательные значения (порядки и мантиссы) исходного массива, а в регистры 4 и 5 - порядки и мантиссы оператора. Выполнение алгоритма производится путем одновременного вычисления четырех значений массива данных, при этом количество регистров в каждом из регистров равно четырем.

Первое значение мантиссы оператора из peiHJCTpoB 5 умножается в умножителе 9 поочередно на четыре последовательных значения мантиссы массива регистров 7. Порядки оператора из регистров 4 склсщываются в сумматоре 8 поочередно с четырьмя последовательными значениями порядков массива из регистров б, при это информация в регистрах 2, 3 и 6, 7-ие сдвигается. Затем четыре значения массива накапливаются в регисрах 17 и 18, причем в регистрах 17 накапливаются порядки, а в регисрах 18 - МёШТИССЫ.

Процесс накопления осуществляется следующим образом. Для сложения двух чисел с плавающей запятой необходимо произвести уравнивание их порялков. Для этого на вычитателе порядков 12 осуществляется вычитание цррядка полученного произведения, поступгиощвго с вакода регистра 10, из порядка, поступающего с шлхода блока 19 нормализации, при этом управляющий сигнгш 45 блока 33 разрешает ялчитание. Еычитатель 12 представляет собой сумматор с принудительным, инвертированием знака числа, которое вычитается, и преобразованием в дополнительный код числа с отрицательным знаком.

Если полученная разность порядков положительна, то сигнал, поступающий из знакового разряда вычитателя 12, пропускает через коммутатор 13 порядок из блока 19. при единичном значении управлякидего сигнала на выходе 47 блока 33. Этот порядок является порядком суммы и записывается в регистры 17. Сигнал из знакового разряда вычитателя 12 пропускает также на коммутатор 15 через, коммутатор 14 маитиссу произведения из умножителя 9 при единичном значении сигнала на выходе 46 блокаЗЗ. В коммутатсдае 15 маитисса сдвигается вправо на число разрядов, равное разиости порядков Принцип рг1боты коммутатора 15 аналогичен принципу работы коммутатора 73 блока 19 нормализации, работ§ КОТОРОГО описана ниже. Дгшее сдвинутая мантисса из блока 15 и мантисса, поступившгш по выходу

37 блока 19 через коммутатор 14/ суммируются-на cyfviMaTope 16, а сумма записывается в регистры 18, сдвигая информацию сверху вниз.

Если же разность порядков, полученная на вычитателе 12, отрицательна, то через коммутатор 13 в регистры 17 поступает порядок произведения из регистра 10, а через коммутатор 14 на коммутатор 15 пос0тупает мантисса из блока 19 нормализации и производится ее сдвиг на нужное количество разрядов. Далее сдвинутая мантисса из коммутатора 15 и мантисса, поступившая из регистра 11 через коммутатор 14,

5 суммируются на сумматоре 16, а сумма записывается в регистры 18.

По окончании накопления первых четырех произведений осуществляется сдвиг информации в регистрах

0 2-7, в результате чего в нижних регистрах групп 4, 5 и б, 7 записываются значения оператора и обрабатываемых данных. Снова осуществляются четыре операции ум5ножения И накопления - умножается втсфое значение оператора на четыре последовательных значения входных данных из регистров 6 и 7. Полученные произведения

0 прибавляются к соответствующим значениям частичным cyNw из регистров 17 и 18, сумма снова заносится в регистры 17 и 18. После выполнения 16 о.пераций умножения-сложе5ния регистры 2, 3 И4, 5 полностью освобождаются. Затем в эти же регистры записываются четыре последующих значения входных данных и оператора, выполняются еще 16 опе0раций умножения-сложения и т.д. Таким образом, каждая пара входных данных используется для выполнения четырех операций умножения-сложения. i

5

Блок нормализации (фиг. 4) предназначен для нормализации поступающих на него чисел, т.е. приведения Их в диапазоне (1/2, 1) и коррекции порядков, поступающих

0 из регистров 17. Поскольку в устройстве обрабатываются двоичные числа, то для их нормализации необходимсэ, чтобы старший разряд мантиссы был равен единице. Например,

5 если поступившее на блок нормализации число равно 0,0001101-2 , где 0,0001101 - мантисса числа, а 101 - его-порядок, то для его нормализации необходимо сдвинуть

0 мантиссу на три разряда влево, а из порядка вычесть число 3, т.е. после нормсшизации получим число 0,1101-2° . Как видно, из примера, для нормализации поступаю5щего числа необходимо в мантиссе

посчитать количество нулей до первого .значащего разряда и осуществить сдвиг мантиссы влево на количество разрядов, равное э-тому числу, а также вычесть из значения порядка указанное число.

Для подсчета количества нулей в мантиссе до первого значащего разрда- служит коммутатор 70 (фиг. 5), на который по входу 35 поступает мантисса из регистров 18. Входящие в состав коммутатора многовходовые элементы П 74 из прямых и инверсны значений разрядов мантиссы формируют сигналы У , где п- разрядность мантиссы причем на выход коммутатора 70 формируется единица только в одном сигнале Ус,, в зависимости от того, какой разряд мантиссы, начиная со старшего, значащий. Так, если значащим является первый разряд мантиссы, то появится единица в сигнале У, если первый разряд мантиссы равен нулю, а второй - единице, то появится единица на выходе в сигнале У и т.д. При нормализации в шифратор 71 с выхода коммутатора 70 поступает код , указывающий, на сколько разрядов необходимо произвести сдвиг мантиссы. Шифратор выполняет функцию, обратную де,шифратору, содержит элементы ИЛИ 7 и предназначендля преобразования кода в двоичный позиционный код , указывающий количество разрядов, на которые необходи,ю сдвинуть мантиссу. На фиг. 5 приведен пример реализации шифратора 16-разрядного кода () в 4-разрядный кс5д . Этот код поступает на коммутатор 73, который и производи указанный сдвиг, а также на сумматор 72 порядка, а котором од вычитается из порядка, поступившего из блока 17 по входу 34.

На фиг. 6 приведен пример рвали,зации коммутатора 73 для сдвига 15-разрядной мантиссы на 1-15 разрядов. Коммутация осуществляется в две ступени. Первая ступень содержит элементы И 78, выходы которых соединены с элементом ИЛИ 79. Коммутацией разрядов в первой ступени управляет дешифратор 76, а во второй ступени - дешифратор 77. Первая ступень осуществляет сдвиг на О, 4, 8, 12 разрядов в зависимости от состояния старших разрядов а. и а, поступающих на дешифратор 76 Вторая ступень осуществляет сдвиг на 0,1,2,3 разряда в зависимости от состояния младших разрядов а и а-г поступающих на дешифратор 77.

Процесс нако№гения точек результата продолжается до тех пор, пока

не будет выбрано из ОЗУ ЭВМ заданное число точек оператора, т.е. ngiка не будет сигнала с блока 30 сравнения. После выдачи результата накопления цикл начинается сначала и так до окончания фильтрации входных данных. После этого поступает сигнал из счетчика 15, который.устанавливает в единицу триггер 61 в блоке 33 управления, запрещается прохождение импульсов с генератора 56 и устройство прекращает работу в ожидании новой команды.

В процессе вычислений БПФ мантиссы чисел, находящиеся в регистре группы 7, умножаются поочередно на число, хранящееся в нижнем регистре группы 5. Параллельно на сумматоре 8 порядков суммируются порядки указанных чисел. Находящиеся в нижних регистрах групп .6 и 4. Полученные произведения (мантисса, порядок) складываются с соответствующими числами из регистров 2 и 3. Для осуществления сложения снова, как и при свертке, производится уравнивание порядков.

Уравнивание порядков осуществляется на вычитателе 12 путем вычитания порядка полученного произ ведения , поступающего с выхода регистра 10, из порядка, поступающего с выхода регистров. 2,.под управлением сигнала 48 блока 33. Если полученна разность порядков положительна, то сигнал, поступающий из знакового разряда вычитателя 12, пропускает через коммутатор 13 порядок из регистров 2. Этот порядок является порядком суммы и з-аписывается в регистры 17. Кроме того, сигнал из знакового разряда вычитателя порядков 12 пропускает на коммутатор 15 через коммутатор 14 мантиссу произ ведения из умножителя 9 при равенстве нулю сигналов на выходах 46 и 47 В коммутаторе 15 мантисса сдвигается вправо на число разрядов, равное разности порядков, и поступает на вход сумматора 16. На второй вход сумматора 16 через коммутатор 14 поступает мантисса второго слагаемого с выхода регистров 3. В регистры 17 записываются большие порядки, а в регистры 18 - сформированные на сумматоре 16 мантисс.

Далее производится сдвиг содержимого регистров групп 4 и 5 на одно число (сверху вниз). Числа регистро.в 6 и 7 умножаются поочередно на число (мантисса/ порядок), сдвинутое в нижние регистры групп 4 и Полученные произведения складываются в сумматоре 16 с нормализованными в блоке 19 результатами предыдущих вычислений, последовательно

BiJABHraeMJMH из регистров 17 и 18. Вновь полученные суммы записываются в освобождающиеся регистры групп 17 и 18. Эти суммы являются двумя комплексными результатами этапа БПф, которые через блок 19 нормализации и выходной регистр 20 выдаются в ОЗУ ЭВМ. После выдачи первой пары сных значений результата вновь повторяется рассмотренный выше цикл вычислений. Отличие заключается только в изменении знаков получакщихся произведений. При этом в регистрах групп 17 и 18 получены два других комплексных значения результата, которые выдаются в ОЗУ ЭВМ.Таким образом, в устройстве вычисляются сразу несколько комплексных значения результата при одних и тех же входных числах.

Аналогично при выполнении других операций, например перемножения

входных массивов комплексных чисел, разновременного суммирования, устройство позволяет вычислить несколько значений результатов при однократном считывании из ОЗУ ЭВМ необходимлх входных данных.

В отличие от известного предлагаемое устройство позволяет повысить достоверность конечных результатов и эффективность дальнейшей обработки полученных результатов за счет обработки массивов данных в формате с плавающей запятой. Использование формата с плавающей

15 запятой по Входу и в процессе вычислений позволяет значительно увеличить диапазон представления исходных чисел, что приводит к увеличению диапазона представления ре20зультатов обработки, а значит, к увеличению точности.

40

S7

I

±J

(TT

6

ffif

W

fftf

Sif

f

Sk

5

if

#5

-

39

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Устройство для выполнения быстрого преобразования фурье | 1976 |

|

SU598085A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Устройство для анализа сейсмических колебаний | 1974 |

|

SU558237A1 |

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

Авторы

Даты

1983-12-23—Публикация

1982-09-06—Подача