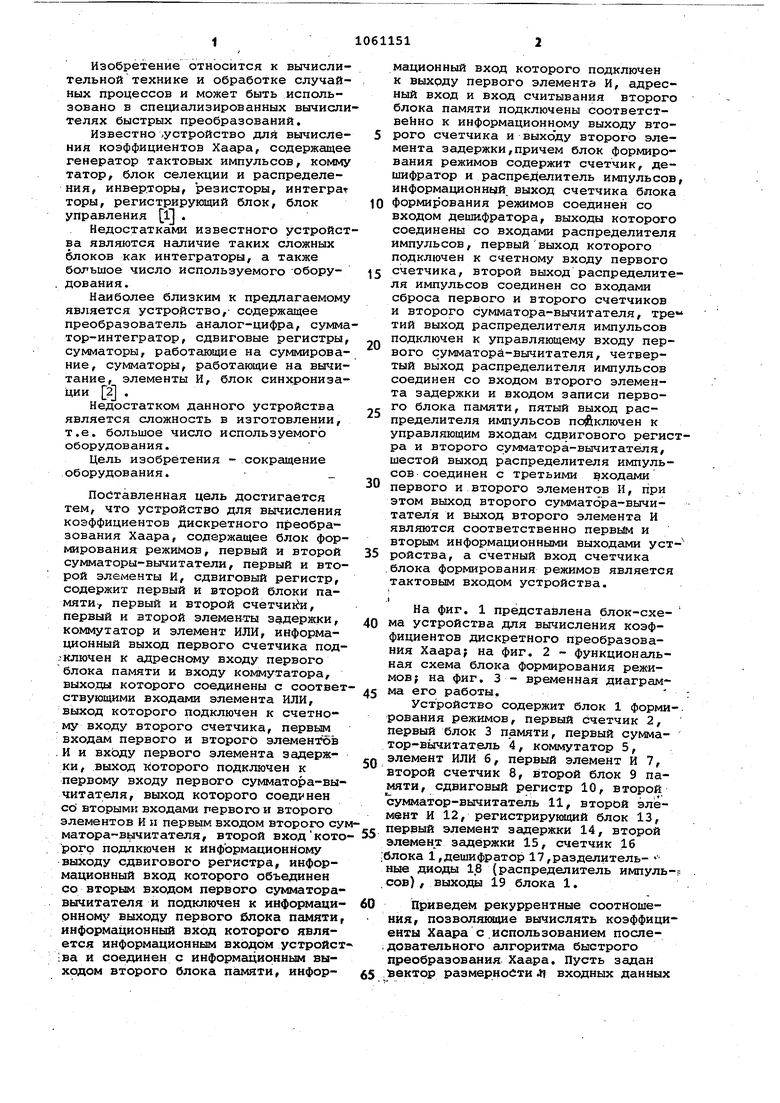

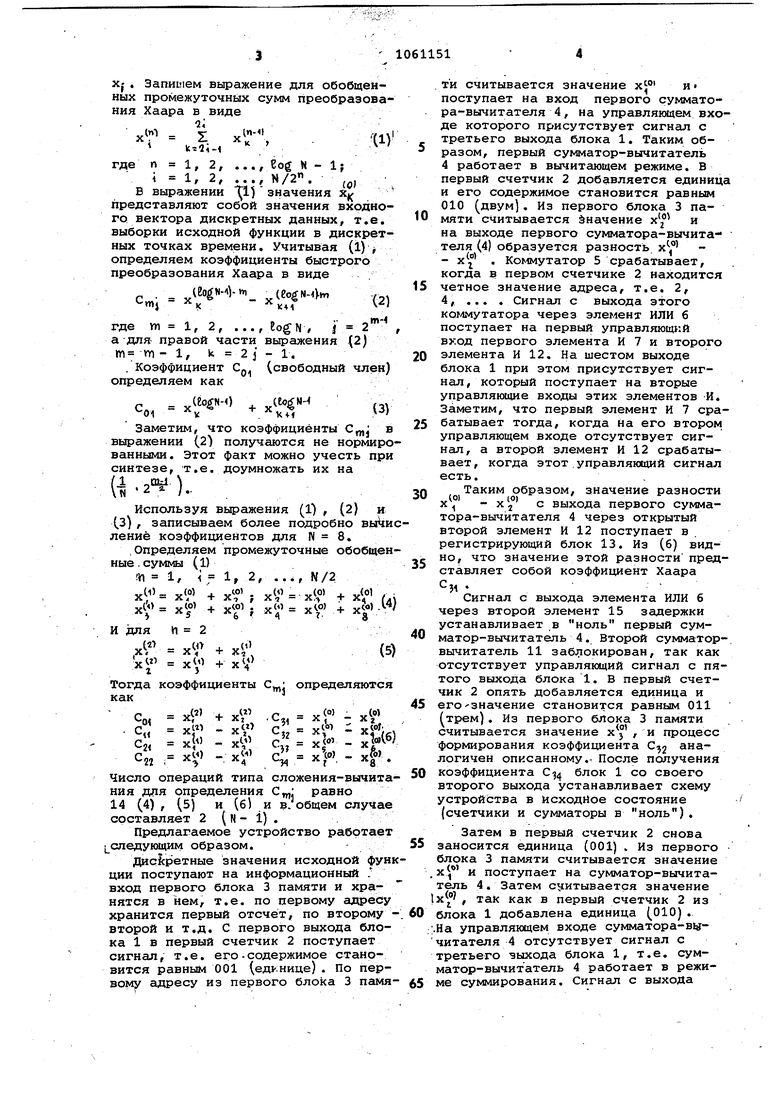

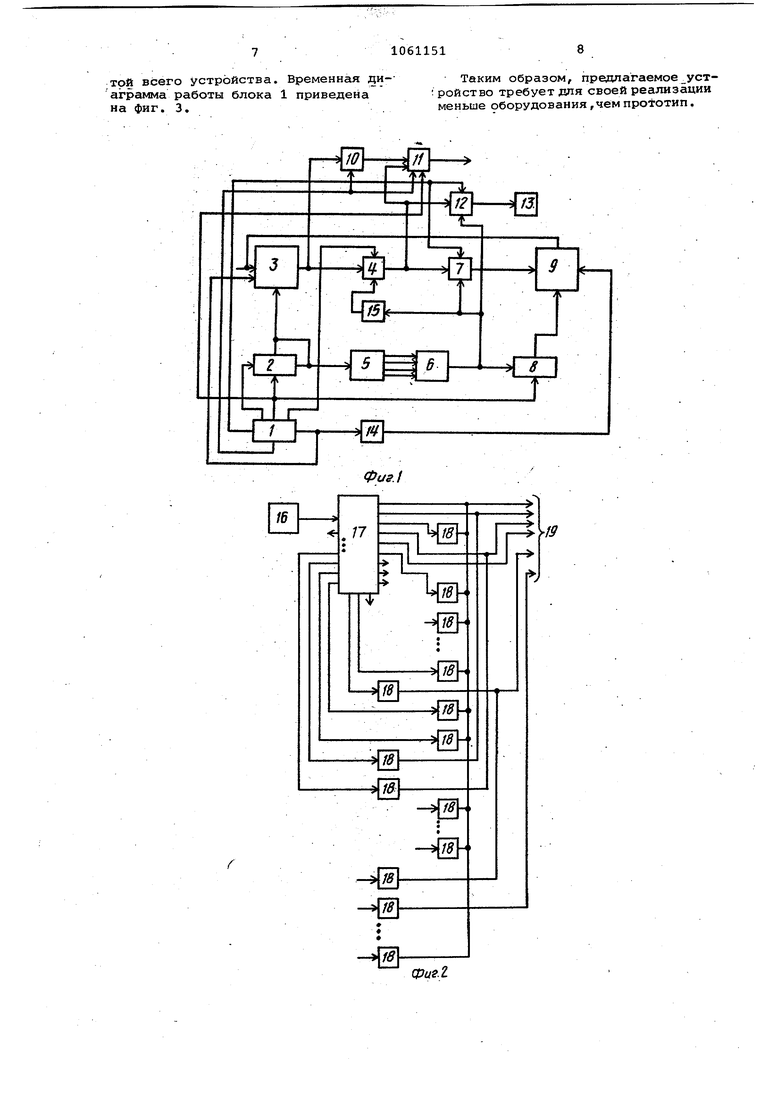

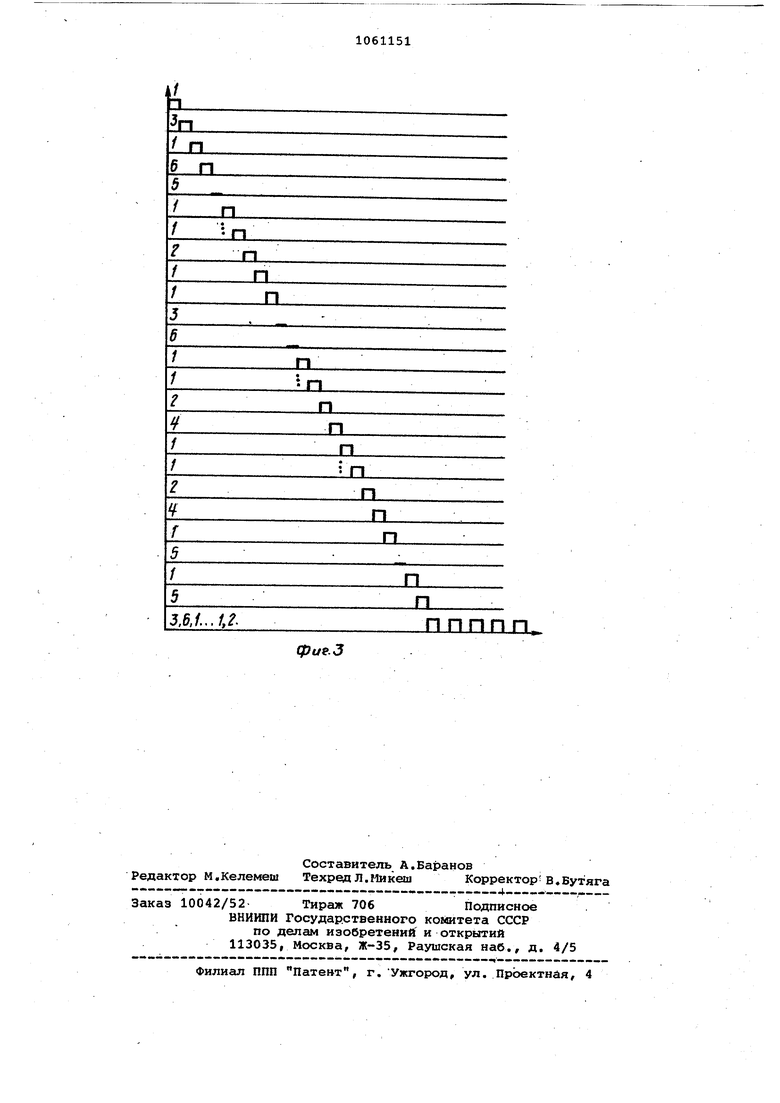

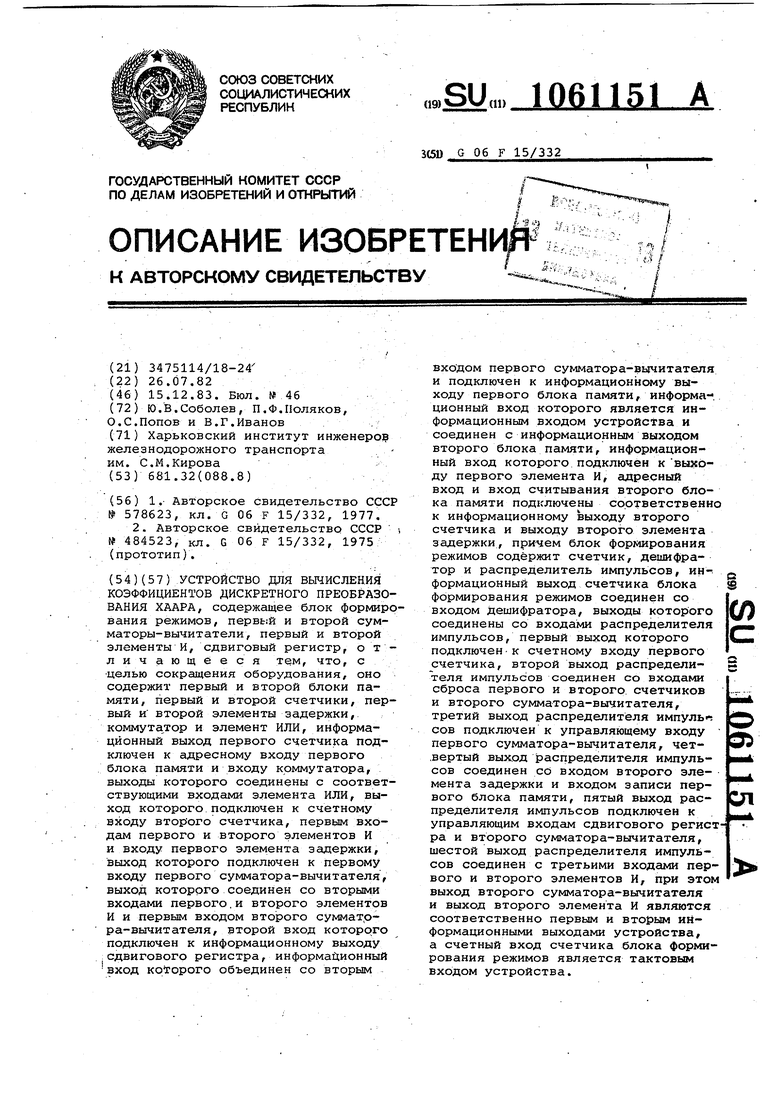

Изобретение относится к вычислительной технике и обработке случайных процессов и может быть использовано в специализированных вычисли телях быстрых преобразований. Известно .устройство для вычисления коэффициентов Хаара, содержащее генератор тактовых импульсов, комму татор, блок селекции и распределения, инверторы, резисторы, интеграт торы, регистрирующий блок, блок управления 1 . Недостатками известного устройст ва являются наличие таких сложных блоков как интеграторы, а также большое число используемого оборудования. Наиболее близким к предлагаемому является устройство, содержащее преобразователь аналог-цифра, сумма тор-интегратор, сдвиговые регистры сумматоры, работающие на суммирование, сумматоры, работающие на вычитание, элементы И, блок синхронизации 2 . Недостатком данного устройства является сложность в изготовлении, т.е. большое число используемого оборудования. Цель изобретения - сокращение оборудования. Поставленная цель достигается тем, что устройство для вычисления коэффициентов дискретного ntieo6paзования Хаара, содержащее блок формирования режимов, первый и второй сумматоры-вычитатели, первый и второй элементы И, сдвиговый регистр, содержит первый и второй блоки памяти-, первый и второй счетчи1 и, первый и второй элемен-ты задержки, коммутатор и элемент ИЛИ, информационный выход первого счетчика под.Ключен к адресному входу первого блока памяти и входу коммутатора, выхо.цы которого соединены с соответ ствующими входами элемента ИЛИ, выход которого подключен к счетному входу второго счетчика, первым входам первого и второго элементов .И и входу первого элемента задержки, выход lioToporo подключен к первому входу первого сумматора-вычитателя, выход которого соед1 нен со вторыми входами первого и второго элементов И и первым входом второго су матора-в итателя, второй входкото рого подлкючен к информационному выходу сдвигового регистра, информационный вход которого объединен со вторым входом первого сумматоравычитателя и подключен к информационному выходу первого блока памяти информационный вход которого является информационным входом устройст ва и соединен с информационным выходом второго блока памяти, информационный вход которого подключен к выходу первого элемента И, адресный вход и вход считывания второго блока памяти подключены соответственно к информационному выходу второго счетчика и выходу второго элемента задержки,причем блок формирования режимов содержит счетчик, дешифратор и распределитель импульсов, информационный, выход счетчика блока формирования режимов соединен со входом дешифратора, выходы которого соединены со входами распределителя импульсов, первыйвыход которого подключен к счетному входу первого счетчика, второй выход распределителя импульсов соединен со входами сброса первого и второго счетчиков и второго сумматрра-вычитателя, тре тий выход распределителя импульсов подключен к управляющему входу первого сумматора-вычитателя, четвертый выход распределителя импульсов соединен со входом второго элемента задержки и входом записи первого блока памяти, пятый выход распределителя импульсов подключен к управляющим входам сдвигового регистра и второго сумматора-вычитателя, шестой выход распределителя импульсов соединен с третьими входами первого и второго элементов И, при этом выход второго сумматора-вычитателя и выход второго элемента И являются соответственно первым и вторым информационными выходами уст- ройства, а счетный вход счетчика блока формирования режимов является тактовым входом устройства. На фиг. 1 представлена блок-схема устройства для вычисления коэффициентов дискретного преобразования Хаара; на фиг. 2 - функциональная схема блока формирования режимов; на фиг. 3 - временная диаграмма его работы. Устройство содержит блок 1 форми-. рования режимов, первый счетчик 2, первый блок 3 памяти, первый сумматор-вычитатель 4, коммутатор 5, элемент ИЛИ б, первый элемент И 7, второй счетчик 8, второй блок 9 памяти, сдвиговый регистр 10, второй сумматор-вычитатель 11, второй элемент И 12, регистрирующий блок 13, первый элемент задержки 14, второй элемент задержки 15, счетчик 16 лока 1,дешифратор 17, раз делительные диоды 18 (распределитель импуль- сов), выходы 19 блока 1. Приведем рекуррентные соотношения, позволяннцие вычислять коэффициенты Хаара с.использованием последовательного алгоритма быстрого преобразования Хаара. Пусть задан ректор размерности 41 входных данных Запиьчем выражение для обобщенных промежуточных сумм преобразова ния Хаара в виде ,м ... , Eog N - 1; п 1, 2, i 1/2, ... N/2. ,о В выражении ) значения xj/ представляют собой значения входно го вектора дискретных данных, т.е. выборки исходной функции в дискрет ных точках времени. Учитывая (1) определяем коэффициенты быстрого преобразования Хаара в виде {EogM-i (eogN-4w (у к к «V где m 1, 2, ...,ogN, | а для правой части выражения (2) w m - 1, k 2 j - 1. Коэффициент GO- (свободный член определяем как ..( „( v +. Заметим, что коэффициенты выражении (2) получаются не нормир ванными. Этот факт можно учесть пр синтезе, т.е. доумножать их на (i2°)Используя выражения (1) , (2) и (,3) , записываем более подробно вы лениё коэффициентов для N 8. ,Определяем промежуточные обобще ные , суммы (1) V 1, 1, 2, ..., IV/2 Тогда коэффициенты С.: определяютс Число операций типа сложения-вычит ния ддя определения С,„ равно ния ддя опр и (б) и в.общем случа 14 (4) , (5) составляет 2 ( N - 1) . Предлагаемое устройство работае следующим образом. Дискретные значения исходной фу ции поступают на информационный . вход первого блока 3 памяти и хранятся в нем, т.е. по первому адрес хранится первый отсчет, по второму второй и т.д. С первого выхода бло ка 1 в первый счетчик 2 поступает сигнал, т.е. егосодержимое становится равным 001 (единице). По пер вому адресу из первого блoka 3 пс1М ти считывается значение и поступает на вход первого сумматора-вычитателя 4, на управляющем входе которого присутствует сигнал с третьего выхода блока 1. Таким образом, первый сумматор-вычитатель 4 работает в вычитающем режиме. В первый счетчик 2 добавляется единица и его содержимое становится равным 010 (двум). Из первого блока 3 памяти считывается Значение Xj и на выходе первого сумматора-вычитателя (4) образуется разность - . Коммутатор 5 срабатывает, когда в первом счетчике 2 находится четное значение адреса, т.е. 2, 4, ... . Сигнал с выхода этого коммутатора через элемент ИЛИ б поступает на первый управляющий вход первого элемента И 7 и второго элемента И 12. На шестом выходе блока 1 при этом присутствует сигнал, который поступает на вторые управляющие входы этих элементов И. Заметим, что первый элемент И 7 срабатывает тогда, когда на его втором управляющем входе отсутствует сигнал, а второй элемент И 12 срабатывает, когда этот , управляющий сигнал есть., Таким образом, значение разности - с выхода первого сумматора-вычйтателя 4 через открытый второй элемент И 12 поступает в регистрирующий блок 13. Из (б) видно, что значение этой разности представляет собой коэффициент Хаара Сигнал с выхода элемента ИЛИ 6 через второй элемент 15 задержки устанавливает в ноль первый сумматор-вычитатель 4. Второй сумматорвычитатель 11 заблокирован, так как отсутствует управляющий сигнал с пятого выхода блока 1. В первый счетчик 2 опять добавляется единица и егоЗначение становится равным 011 трем). Из первого блока 3 памяти считывается значение , и процесс формирования коэффициента аналогичен описанному.. После получения коэффициента С ц блок 1 со своего второго выхода устанавливает схему устройства в исходное состояние (счетчики и сумматоры в ноль). Затем в первый счетчик 2 снова заносится единица (001) . Из первого блока 3 памяти считывается значение х, и поступает на сумматор-вычитатель 4. Затем считывается значение , так как в первый счетчик 2 из блока 1 добавлена единица (010). На управляющем входе сумматора-вичитателя 4 отсутствует сигнал с третьего зьрсода блока 1, т.е. сумматор-вычитатель 4 работает в режиме суммирования. Сигнал с выхода

коммутатора 5 (так как в счетчике 2 четный адрес) через элемент ИЛИ 6 поступает на первый вход первого элемента И 7, на втором входе которого отсутствует сигнал с шестого выхода блока 1, Таким образом, переый элемент И 7 открыт и значение промежуточной суммы поступает по первому адресу во второй блок 9 памяти, так как во втором счетчике 8 записана единица с выхода элемента ИЙИ 6. Этот же сигнал через второй элемент 15 задержки устанавливает в ноль первый сумматор-вычитатель 4. В первом счетчике 2 находится в это время значение третьего адреса (011) , и считанное значение поступает на сумматор-вычитатель. Процесс обработки повторяется до тех пор,- пока в первом счетчике

2не будет двоичное значение, равное восьми (ЮОО) , т.е. адрес последнего . Таким образом, во втором блоке 9 памяти по первому адресу находится значение промежуточной суммы X, , по второму - и т.д. (4

Далее со второго выхода блока 1 схема устанавливается в исходное состояние, а управляющий сигнал с четвертого выхода блока ,1 переписывает содержимое второго .блока 9 памяти в первый блок 3 памяти. Причем содержимое четвертого адреса xj записывается по первому адресу первого блока 3 памяти, затем содержимое третьего адреса х, записывается снова по первому адресу пер вого блока 3 памяти, а значения первого адреса этого блока 3 памяти предварительно переписываются по второму адресу и т.д. Таким образом в первом блоке 3 памяти по первому адресу находится значение х;, , по второму - Xj и т.д.

Блок 1 сз нов а засылает в первый счетчик значение (001) и из первого блока поочередно считываются значения , и т,д., т.е. формируются промежуточные суммы ху и (5) . Как только значение первого счетчика 2 стает равным четырем 4,100) , т.е. образуются две последние промежуточные суммы и блок 1 устанавливает схему в исходное состояние, а управляющий сигнал с его четвертого выхода переписывает содержимое второго блока 9 памяти первый блок 3 памяти аналогично описанному. Так как по второму адресу второго блока 9 памяти находится значение , то оно поступает по первому адресу первого блока

3памяти. Предварительно в этом блоке происходит последовательный

сдвиг на один адрес в сторону увеличения его содержимого, т.е. в пер вом блоке 3 памяти, начиная с первого адреса, находятся значения промежуточных сумм в следующем порядке: xf . х( , xW , , , xia . в первый счетчик 2 заносится единица (001) и из первого блока 3 памяти считывается значение х,, которое поступает на вход первого сумматоравычитателя 4. В сдвиговый регистр 10 это значение на.заносится, так как отсутствует управляющий сигнал с пятого выхода блока 1. Затем в первом счетчике находится значение. два (010) , и из первого блока 3 памяти считывается значение ,которое поступает на первый сумматорвычитатель 4. На пятом и третьем выходах блока 1 появляются управляющие сигналы, которые позволяют занести значение x.j в сдвиговый регистр 10, а в первом сумматоре-вычитателе 4 получить разность - ,. т.е. коэффициент С (б). Управляющий сигнал с шестого выхода блока 1 открывает второй элемент И 12, так как на его первом управляющем входе присутствует разрешаю-; щий сигнал с выходи элемента ИЛИ б, а в .счетчике находится значение два (010) , и коммутатор 5 срабатывает. С выхода второго элемента И 12 значение коэффициента С|( поступает в регистрирующий блок.13. В сдвиговом регистре 10 происходит сдвиг, влево информации на один разряд, т.е. умножение на два, и эта информация (2хт) поступает на первый вход второго сумматора-вычитателя 11, на второй вход которого с выхода первого сумматора-вычитателя поступает значение разности (xj - х) , Таким образом, с выхода второго сумматора-вычитателя 11 снимается значение коэффициента GOI {Со vl 4- 9vU

XS -ь 2х

+ xj) . в первый счетчик 2.

X. Г 5 J ll lj /J3EUia X ил лзаносится двоичное значение три{110 и.из первого блока 3 Памяти считывается значение х, , потом при значении в первом счетчике, равном четырем (100) , считывается и на выходе первого суг/1матора-вычитателя ,4 формируется коэффициент Cjj (б).

По аналогичной схеме формируются остальные коэффициенты. После считывания последнего адреса, т.е. значения , блок 1 устанавливает схему в исходное состояние.

Режим работы устройства задает блок 1 (фиг. 2). Счетчик 16 работает в обычном счетном режиме. По мере изменения его содержимого на выходах дешифратора 17 последовательно появляются управляющие сигналы (сначала на первом, потом на втором и т.д.). Эти сигналы .через разделительные диоды 18 (распределитель, импульсов) поступают на соотв.етствующие выходы блока 1 и управляют рабо-р

той всего устройства. Временная диаграмма работы блока 1 приведена на фиг. 3.

Таким образом, предлагаемое уст: роист во требует для своей реализации меньие оборудования,чем прототип.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для вычисления функций | 1987 |

|

SU1411775A1 |

| Устройство для решения системы линейных уравнений | 1987 |

|

SU1411776A1 |

| Устройство для контроля параметров | 1989 |

|

SU1667009A1 |

| Устройство для выполнения быстрого преобразования Фурье | 1988 |

|

SU1640709A1 |

| Устройство для преобразования по функциям Хаара | 1986 |

|

SU1327119A1 |

| Спектральный анализатор случайных сигналов | 1984 |

|

SU1269048A1 |

| Устройство для передачи телеметрической информации | 1983 |

|

SU1096682A1 |

| Устройство для вычисления коэффициентов обобщенных функций Хаара | 1979 |

|

SU942036A1 |

| Устройство для вычисления скользящего спектра | 1987 |

|

SU1427386A1 |

| Устройство для вычисления скользящего спектра | 1988 |

|

SU1527642A1 |

УСТРОЙСТВО ДЛЯ ВЫЧИСЛЕНИЯ КОЭФФИЦИЕНТОВ ДИСКРЕТНОГО ПРЕОБРАЗОВАНИЯ ХААРА, содержащее блок формирования режимов, первый и второй сумматоры-вычитатели, первый и второй элементы И, сдвиговый регистр, отличающееся тем, что, с целью сокращения оборудования, оно содержит первый и второй блоки памяти, первый и второй счетчики, первый и второй элементы задержки, коммута,тор и элемент ИЛИ, информационный выход первого сч;етчика подключен к адресному входу первого блока памяти и входу коммутатора, выходы которого соединены с соответствующими входами элемента ИЛИ, выход которого подключен к счетному входу второго счетчика, первым входам первого и второго элементов И и входу первого элемента задержки, выход которого подключен к первому входу первого сумматора-вычитателя, выход которого соединен со вторыми входами первого.и второго элементов И и первым входом второго суммат.ора-вычитателя, второй вход которого подключен к информационному выходу .сдвигового регистра, информационный вход которого объединен со вторым входом первого сумматора-вычитателя и подключен к информационному выходу первого блока памяти, информационный вход которого является информационным входом устройства и соединен с информационным выходом второго блока памяти, информационный вход которого подключен к выходу первого элемента И, адресный вход и вход считывания второго блока памяти подключены соответственно к информационному выходу второго счетчика и выходу второго элемента задержки, при-чем блок формирования режимов содержит счетчик, дешифратор и распределитель импульсов, информационный выход счетчика блока формирования режимов соединен со (Л входом дешифратора, выходы которого соединены со входами распределителя импульсов, первый выход которого подключен-к счетному входу первого счетчика, второй выход распределителя импульсов соединен со входами сброса первого и второго счетчиков и второго сумматора-вычитателя, третий выход распределителя импульсов подключен к управляющему входу Ot) первого сумматора-вычитателя, чет.вертый выход распределителя импульсов соединен со входом второго эле- мента задержки и входом записи перСП вого блока памяти, пятый выход распределителя импульсов подключен к управляющим входам сдвигового регистра и второго сумматора-вычитателя, шестой выход распределителя импульсов соединен с третьими входами первого и второго элементов И, при этом выход второго сумматора-вычитателя и выход второго элемента И являются соответственно первым и вто&ым информационными выходами устройства, а счетный вход счетчика блока формирования режимов является тактовым входом устройства.

17

фие.З

ппппп,

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Устройство для формирования коэффициентов разложения хаара | 1974 |

|

SU484523A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1983-12-15—Публикация

1982-07-26—Подача