1

Изобретение относится к электросвязи и может использоваться в цифровых системах передачи, использующих кабельные линии или линии других тинов, оборудованные регенераторами квазитроичных сигналов кодов с самохронированием.

Известно устройство для преобразования двоичного кода в квазитроичный, содержащее два элемента задержки, формирователь квазитроичного кода и счетчик 1.

Однако известное устройство является чувствительным к нереплюсовке (перемене полярности квазитроичного сигнала), что снижает точность преобразования.

Цель изобретения - повышение точности преобразования.

Для этого в устройство для преобразования двоичного кода в квазитроичный, содержащее два элемента задержки, формирователь квазитроичного кода и счетчик, введен синхронный коммутатор, входы которого соединены с выходами элементов задержки, а выход синхронного коммутатора подключен к первым входам формирователя квазитроичного кода и счетчика, второй вход которого соединен с входом первого элемента задержки, при этом выход счетчика нодключен к второму входу формирователя квазитроичного кода и входу второго элемента задержки.

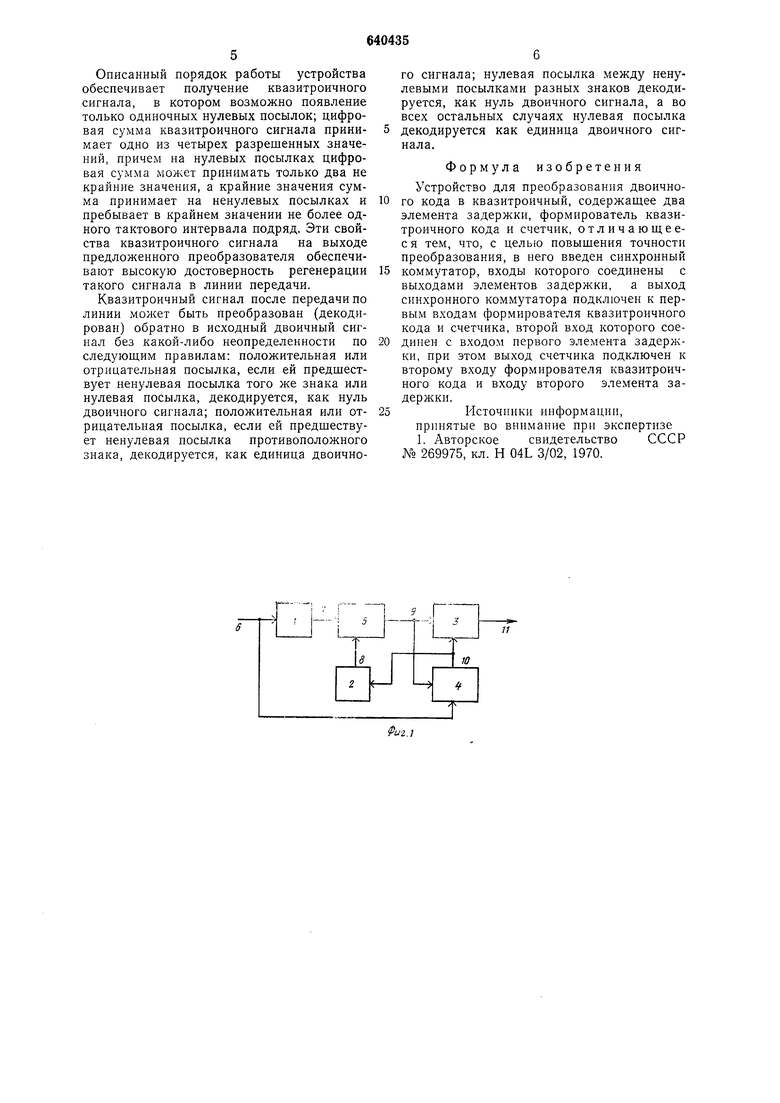

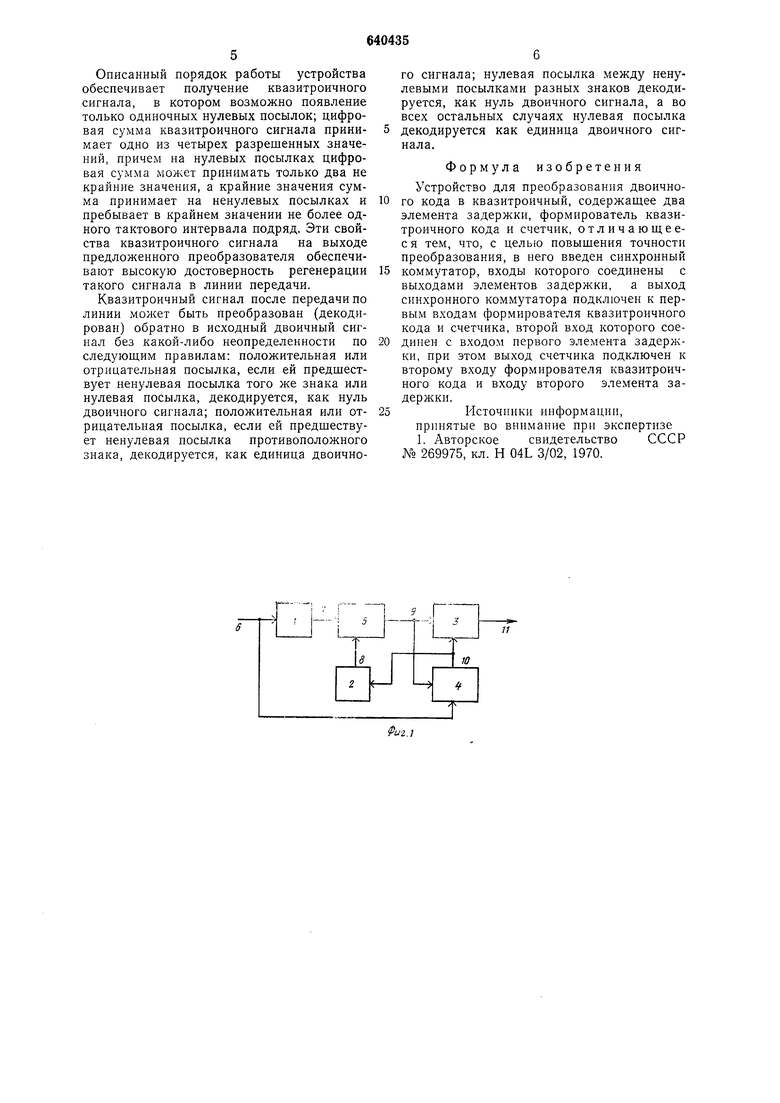

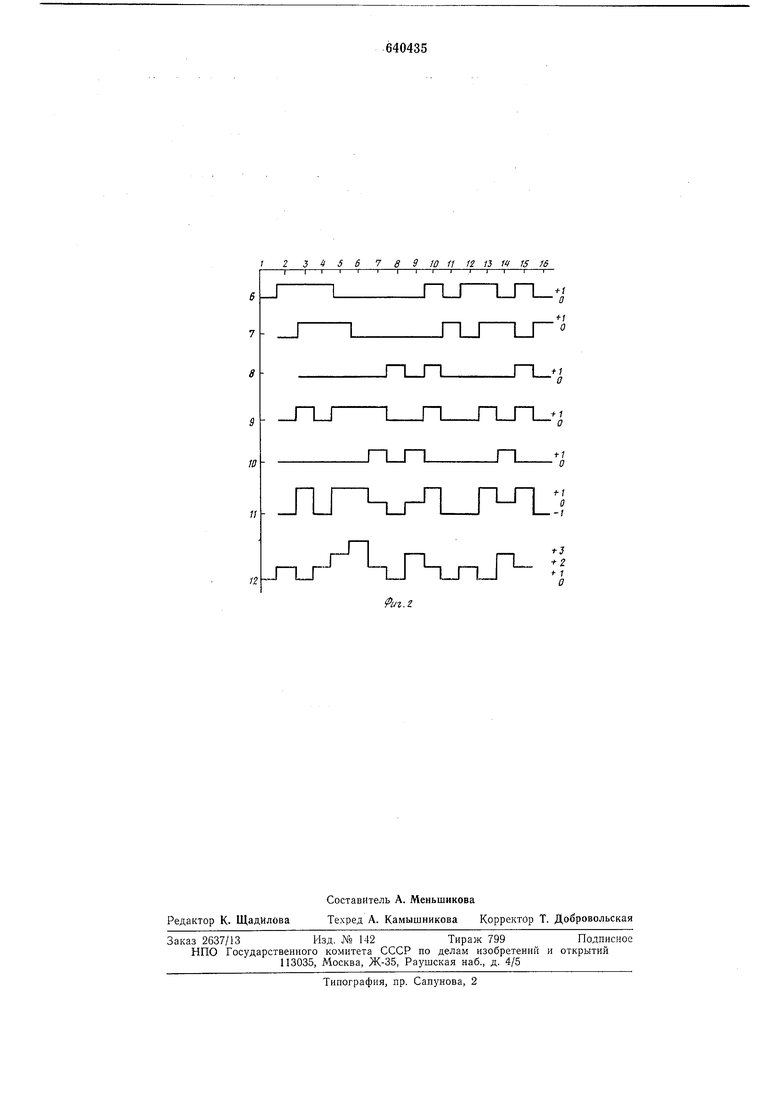

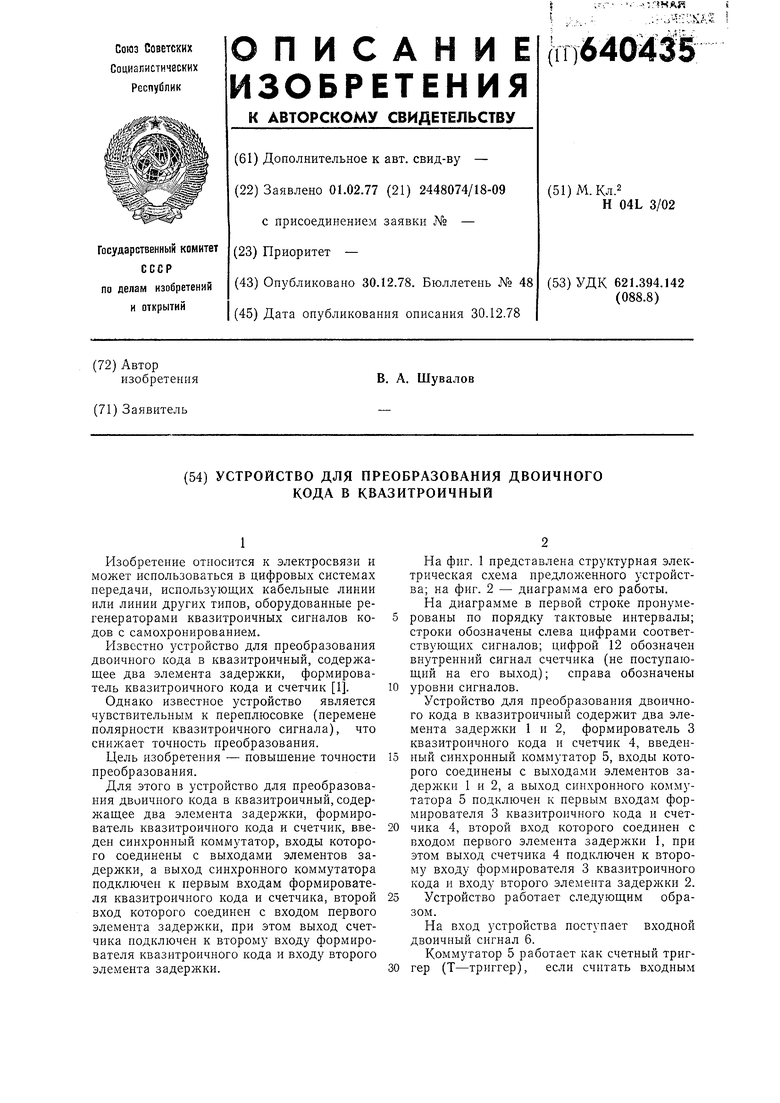

На фиг. 1 представлена структурная электрическая схема предложенного устройства; на фиг. 2 - диаграмма его работы.

На диаграмме в первой строке пронумерованы по порядку тактовые интервалы; строки обозначены слева цифрами соответствующих сигналов; цифрой 12 обозначен внутренний сигнал счетчика (не поступающий на его выход); справа обозначены

уровни сигналов.

Устройство для преобразования двоичного кода в квазитроичный содержит два элемента задержки 1 н 2, формирователь 3 квазитроичного кода и счетчик 4, введенный синхронный коммутатор 5, входы которого соединены с выходами элементов задержки 1 и 2, а выход синхронного коммутатора 5 подключен к первым входам формирователя 3 квазитроичного кода н счетчика 4, второй вход которого соединен с входом первого элемента задержки 1, при этом выход счетчика 4 подключен к второму входу формирователя 3 квазитроичного кода и входу второго элемента задержки 2.

Устройство работает следующим образом.

На вход устройства ноступает входной двоичный сигнал 6.

Коммутатор 5 работает как счетный триггер (Т-триггер), если считать входным

сигналом такого триггера объединенные по схеме ИЛИ двоичный сигнал 7 (фиг. 2) и двоичный сигнал 8 (фиг. 2), причем переключение коммутатора 5 происходит в начале тактового интервала, на котором имеется импульс.

Таким образом, коммутатор 5 формирует двоичный сигнал 9 (при возможных сочетаниях значений сигналов 7 и 8) по правилам табл. 1.

Логика работы коммутатора 5. Т а б .л II ц а I

| название | год | авторы | номер документа |

|---|---|---|---|

| Преобразователь двоичного сигнала в квазитроичный сигнал | 1983 |

|

SU1109926A1 |

| Преобразователь двоичного сигнала в квазитроичный | 1982 |

|

SU1095430A1 |

| Регенератор двоичного линейного сигнала | 1982 |

|

SU1075435A1 |

| Регенератор необслуживаемого пункта | 1978 |

|

SU758541A1 |

| Устройство для передачи и приема основного и дополнительного сигналов | 1986 |

|

SU1390809A1 |

| СИСТЕМА РАДИОСВЯЗИ | 1999 |

|

RU2168864C2 |

| Преобразователь двоичного сигнала в балансный пятиуровневый сигнал | 1977 |

|

SU651491A1 |

| Устройство для передачи и приема дискретных сообщений | 1983 |

|

SU1095220A1 |

| Преобразователь двоичного сигнала в балансный пятиуровневый сигнал | 1981 |

|

SU987832A1 |

| Декодирующее устройство кода Рида-Соломона | 1988 |

|

SU1640830A1 |

Формирователь 3 формирует квазитроичный сигнал по правилам табл. 2.

Счетчик 4 является реверсивным счетчиком, который подсчитывает текущую цифровую сумму квазитроичного сигнала И (т. е. текущую сумму амплитуд посылок этого сигнала).

Благодаря использованию кроме сигнала 9 незадержанного входного сигнала 6 счетчик экстраполирует цифровую сумму сигнала 11 па 1 таковый интервал вперед, причем уровень внутреннего сигнала 12 на каждом интервале, за которым в следующем тактовом интервале следует ненулевая посылка сигнала 11, соответствует значению цифровой суммы сигнала 11 на этом следующем тактовом интервале. Уровень сигнала 12 на том тактовом интервале, за которым должна следовать нулевая посылка сигнала И, не соответствует значению

Логика работы формирователя 3. Таблица 2

цифровой суммы на этой нулевой посылке (вместо уровня +2 принимает уровень +3, вместо уровня +1 принимает уровень 0) и тогда в следующем тактовом интервале счетчик 4 формирует посылку (двоичную единицу) сигнала 10. Эта посылка сигнала 10 далее-формирует нулевую посылку сигнала И в формирователе 3 и после задержки элементом задержки 2 переключает коммутатор 5 (на фиг. 2 формирование нулевой посылки квазитроичного сигнала 11 происходит в 7-, 9- и 14-м тактовых интервалах).

Счетчик 4 формирует свой внутренний сигнал 12 и двоичный сигнал 10 по правилам табл. 3.

Логики работы счетчика 4.

Т а б л и ца 3

Описанный порядок работы устройства обеспечивает получение квазитроичного сигнала, в котором возможно появление только одиночных нулевых посылок; цифровая сумма квазитроичного сигнала принимает одно из четырех разрешенных значений, причем на нулевых посылках цифровая сумма может принимать только два не крайние значения, а крайние значения сумма принимает на ненулевых посылках и пребывает в крайнем значении не более одного тактового интервала подряд. Эти свойства квазитроичного сигнала на выходе предложенного преобразователя обеспечивают высокую достоверность регенерации такого сигнала в линии передачи.

Квазитроичный сигнал после передачи по линии может быть преобразован (декодирован) обратно в исходный двоичный сигнал без какой-либо неопределенности по следующим правилам: положительная или отрицательная посылка, если ей предшествует ненулевая посылка того же знака или нулевая посылка, декодируется, как нуль двоичного сигнала; положительная или отрицательная посылка, если ей предшествует ненулевая посылка противоположного знака, декодируется, как единица двоичного сигнала; нулевая посылка между ненулевыми посылками разных знаков декодируется, как нуль двоичного сигнала, а во всех остальных случаях нулевая посылка декодируется как единица двоичного сигнала.

Формула изобретения

Устройство для преобразования двоичного кода в квазитроичный, содержащее два элемента задержки, формирователь квазитроичного кода и счетчик, отличающеес я тем, что, с целью повышения точности преобразования, в него введен синхронный

коммутатор, входы которого соединены с выходами элементов задержки, а выход синхронного коммутатора подключен к первым в.ходам формирователя квазитроичного кода и счетчика, второй вход которого соединен с входом первого элемента задержки, при этом выход счетчика подключен к второму входу формирователя квазитроичного кода и входу второго элемента задержки.

Источники информации,

принятые во внимание при экспертизе 1. Авторское свидетельство СССР № 269975, кл. Н 04L 3/02, 1970.

-TLJ10

Jir L rLj j-L:i

12

Авторы

Даты

1978-12-30—Публикация

1977-02-01—Подача