Изобретение относится к вычислительной технике и может быть использовано в системах передачи и переработки цифровой информации.

11ель изобретения - повышение достоверности декодирования и увеличение информативности устройства.

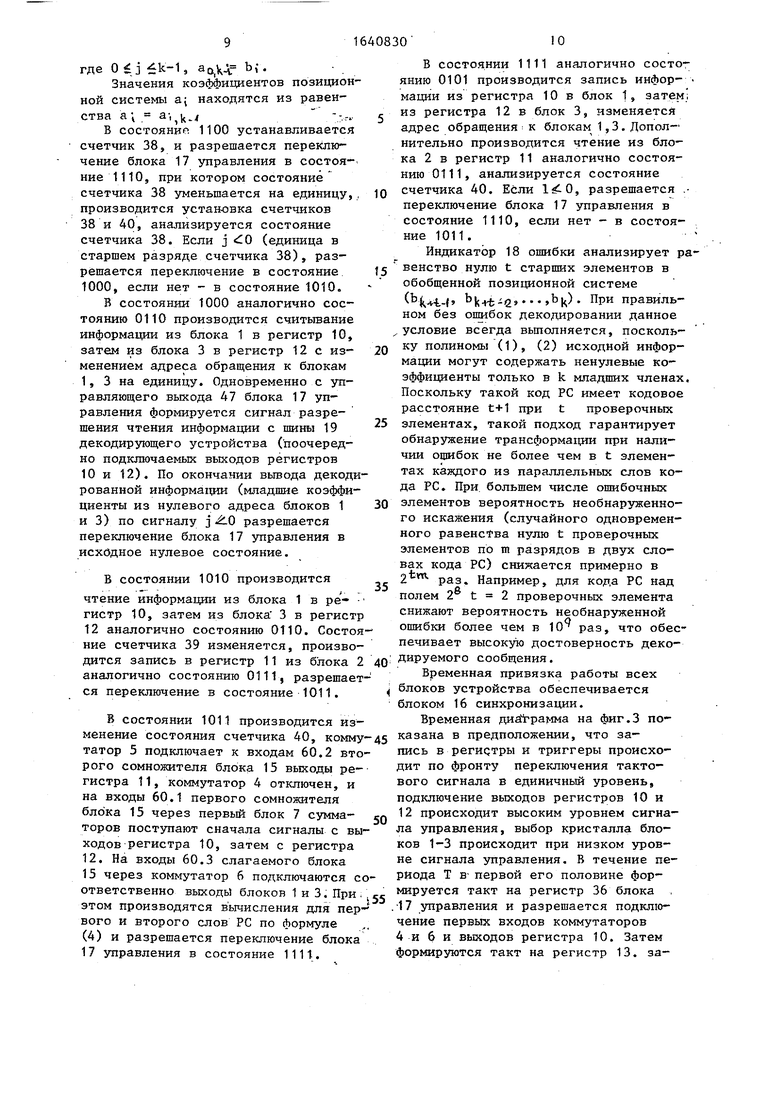

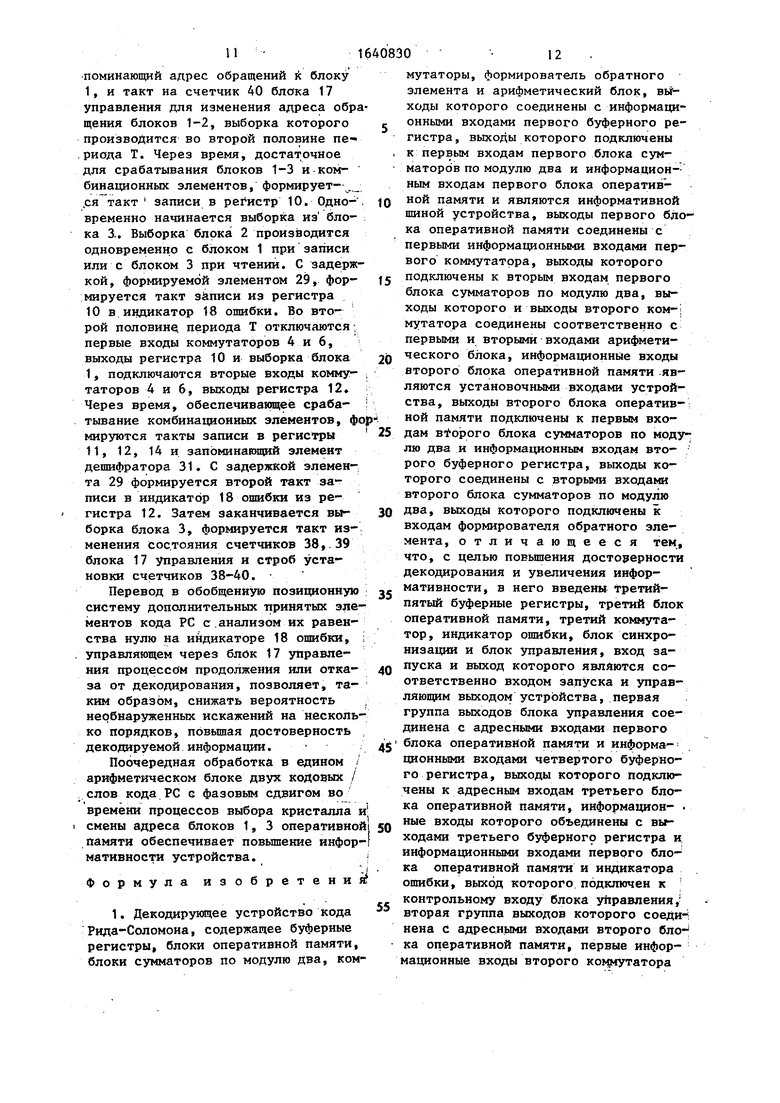

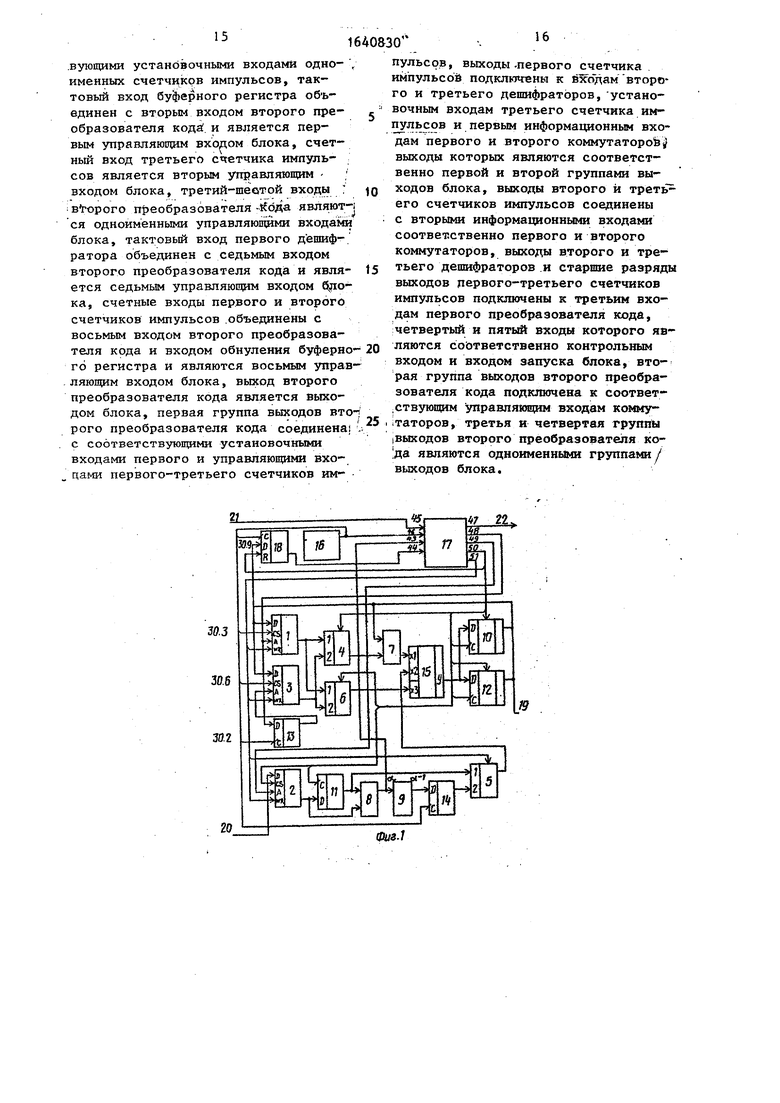

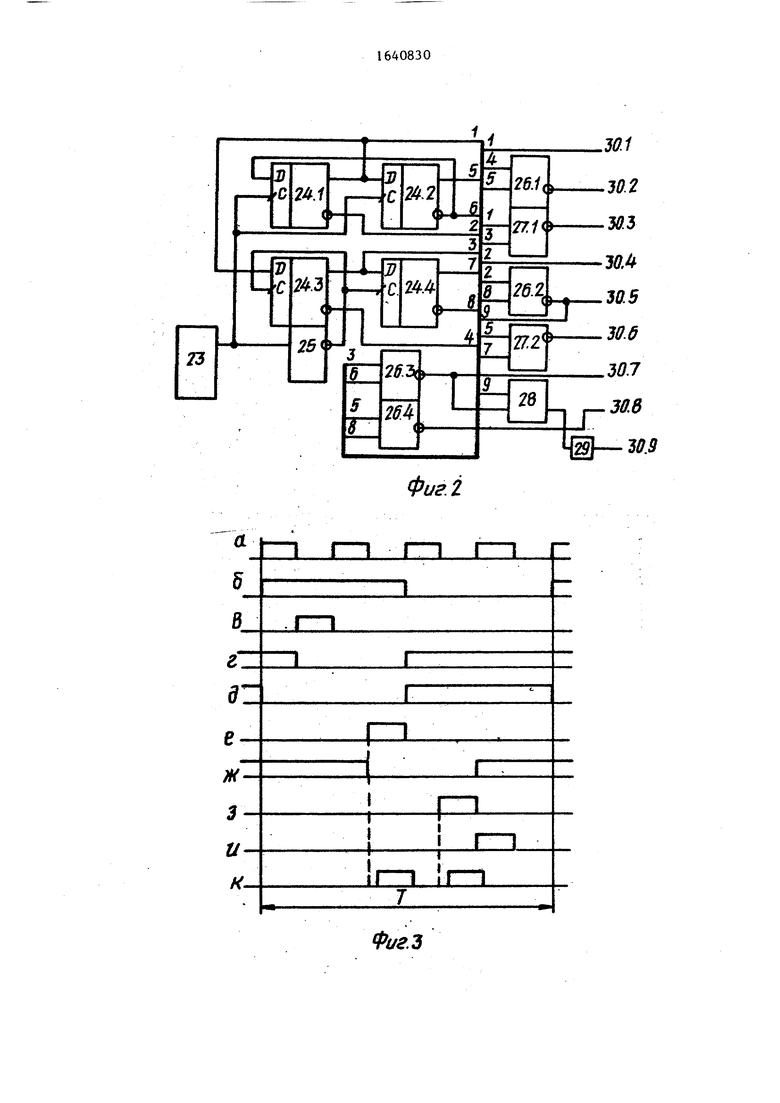

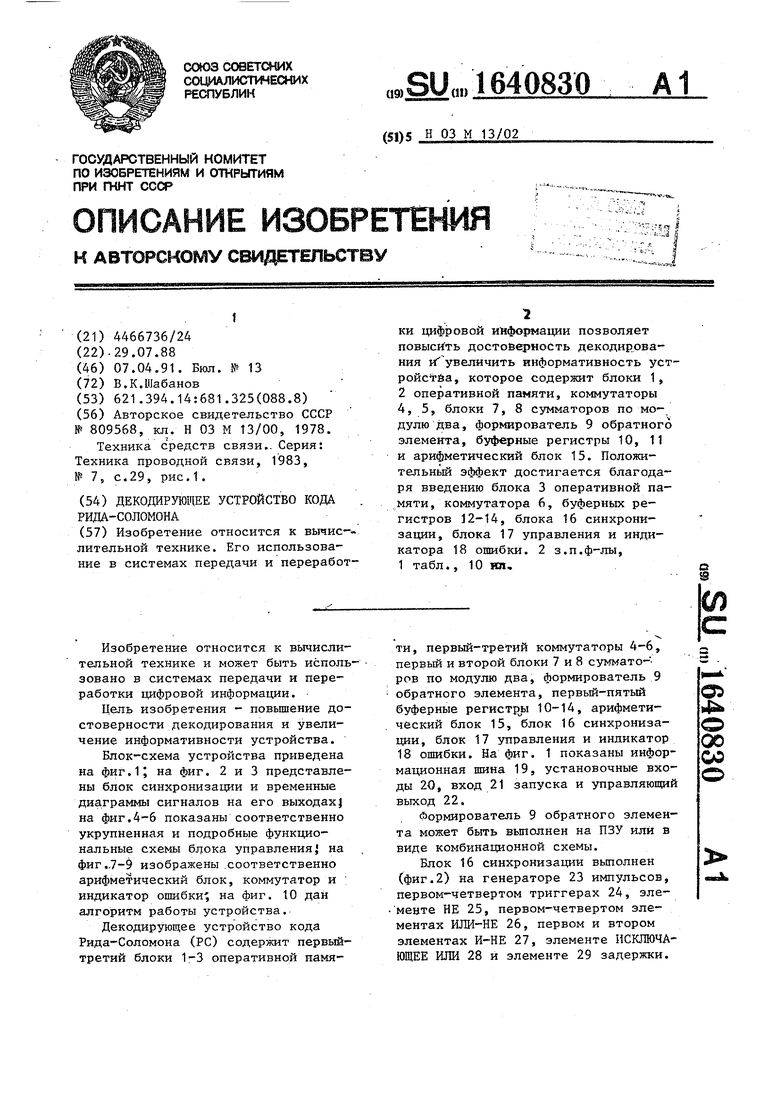

Блок-схема устройства приведена на фиг.1; на фиг. 2 и 3 представлены блок синхронизации и временные диаграммы сигналов на его выходахJ на фиг.4-6 показаны соответственно укрупненная и подробные функциональные схемы блока управления на фиг.7-9 изображены соответственно арифметический блок, коммутатор и индикатор ошибки-; на фиг. 10 дан алгоритм работы устройства.

Декодирующее устройство кода Рида-Соломона (PC) содержит первый- третий блоки 1-3 оперативной памяти, первый-третий коммутаторы 4-6, первый и второй блоки 7 и 8 суммато- ров по модулю два, формирователь 9 обратного элемента, первый-пятый буферные регистру 10-14, арифметический блок 15, блок 16 синхронизации, блок 17 управления и индикатор 18 ошибки. На фиг. 1 показаны информационная шина 19, установочные входы 20, вход 21 запуска и управляющий выход 22.

Формирователь 9 обратного элемента может быть выполнен на ПЗУ или в виде комбинационной схемы.

Блок 16 синхронизации выполнен (фиг.2) на генераторе 23 импульсов, первом-четвертом триггерах 24, элементе НЕ 25, первом-четвертом элементах ИЛИ-НЕ 26, первом и втором элементах И-НЕ 27, элементе ИСКЛЮЧАЮЩЕЕ ИЛИ 28 и элементе 29 задержки.

&

Јъ

О 00

00

10

На фиг. 2 показаны также выходы 30 блока 16.

На фиг. 3 обозначены следующие сигналы: а - импульсы с выхода генератора 23J б - к - сигналы на выходах 30.1-30.9 блока 16.

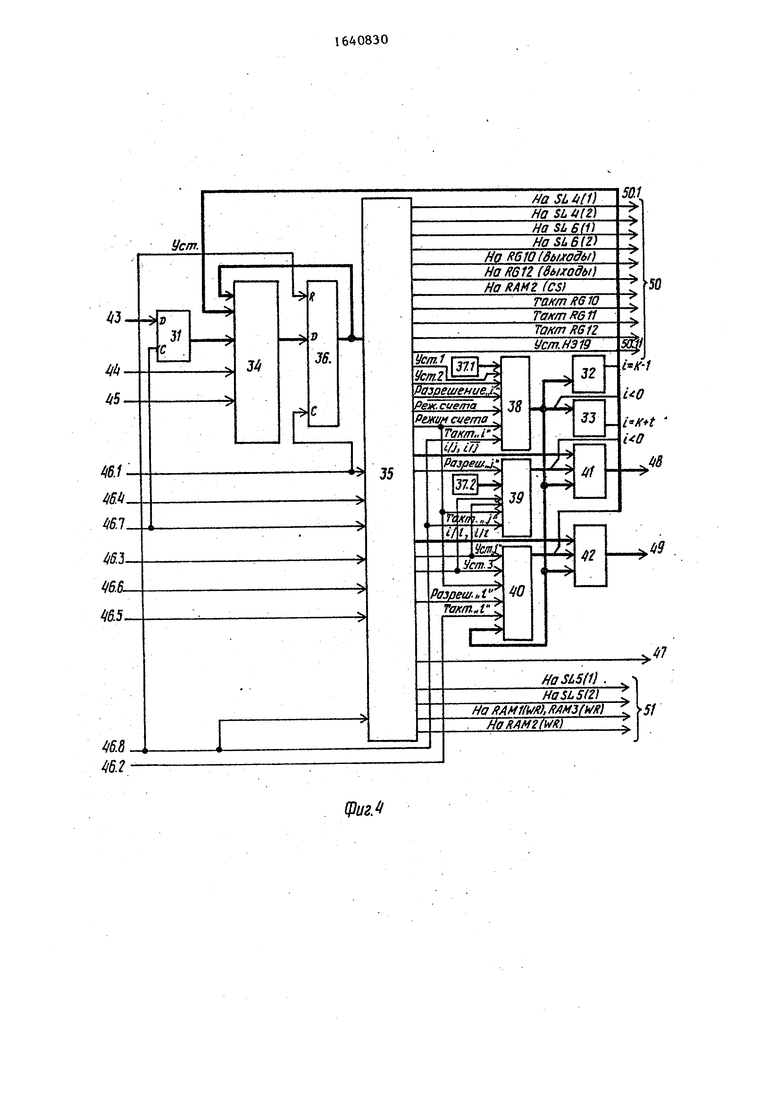

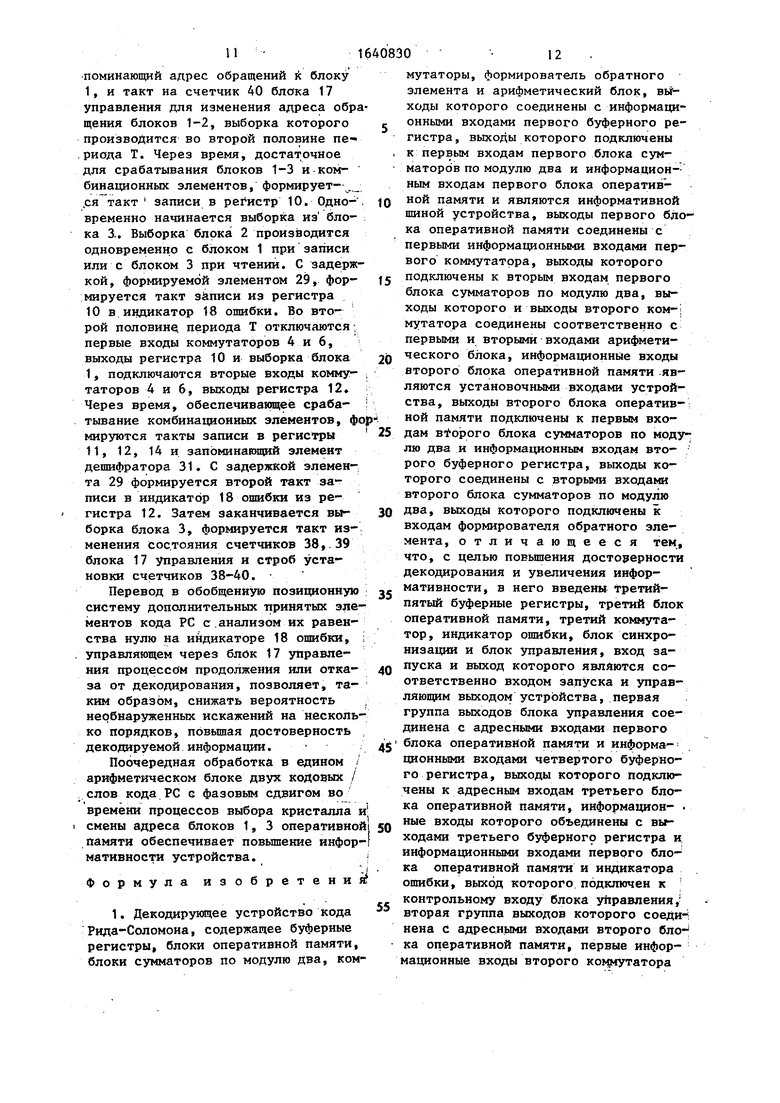

Блок 17 управления содержит (фиг.4) первый-третий дешифраторы 31-33, первый и второй преобразова- тели 34 и 35 кода, буферный регистр 36, первый и второй источники 37 постоянного кода, первый-третий счетчики 38-40 импульсов и первый и второй коммутаторы 41 и 42. На фиг. 4 15 показаны информационные входы 43, контрольный вход 44, вход 45 запуска, управляющие входы 46, выход 47 и первая-четвертая группы 48-51 выходов блока 17.

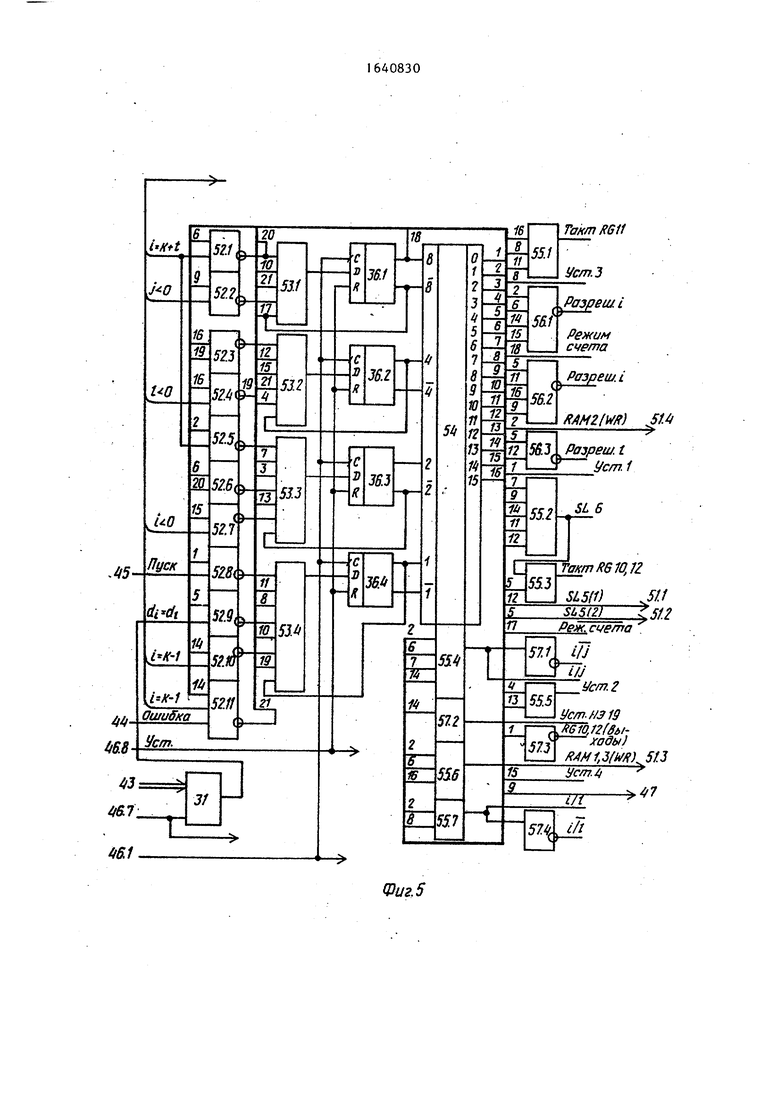

Более подробно выполнение блока 17 управления раскрыто на фиг.5 и 6. В частности, первый преобразователь

34кода может быть выполнен на элементах И-НЕ 52 и сумматорах 53 по модулю два, второй преобразователь

35кода реализуется на дешифраторе 54, сумматорах 55 по модулю два, элементах ИЛИ-НЕ 56 и элементах НЕ 57. На фиг. 5 не показаны элементы И, служащие для формирования сигналов на третьей и четвертой группах 50 и 51 выходов блока 17 по следующим правилам (в таблице слева указан номер выхода третьей группы 50, а справа - логическое выражение, где вместо переменных в круглых скобках стоят номера элементов, сигналы с выходов которых и формируют данное выражение) :

20

25

30

35

40

50.1(30.1)И(51.2)

50.2(30. 4)И(51.2)

50.3(30.1)И(55.2)

50.4(30.4)И(55.2)

50.5(30.1)И(57.3)

50.6(30.4)И(57.3)

50.7(27.1)И(51.4) (27.2)И(51.4)

(26.2)И(55.3)

(26.3)И(55.1)

(26.3)И(55.3)

(26.4)И(57.2)

ИЛИ

50.8 50.9 SO.IOf

0.1 Г

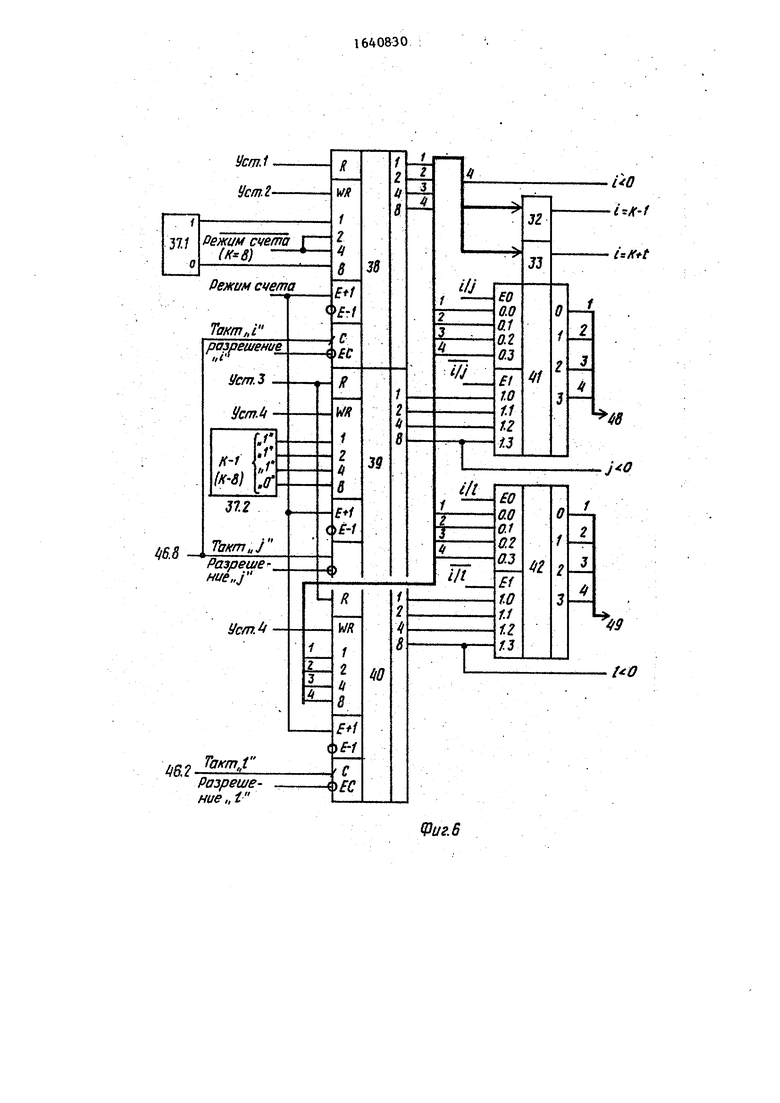

На фиг. 6 показано более подр соединение источников 37 постоян кода, счетчиков 38-40 импульсов коммутаторов 41, 42.

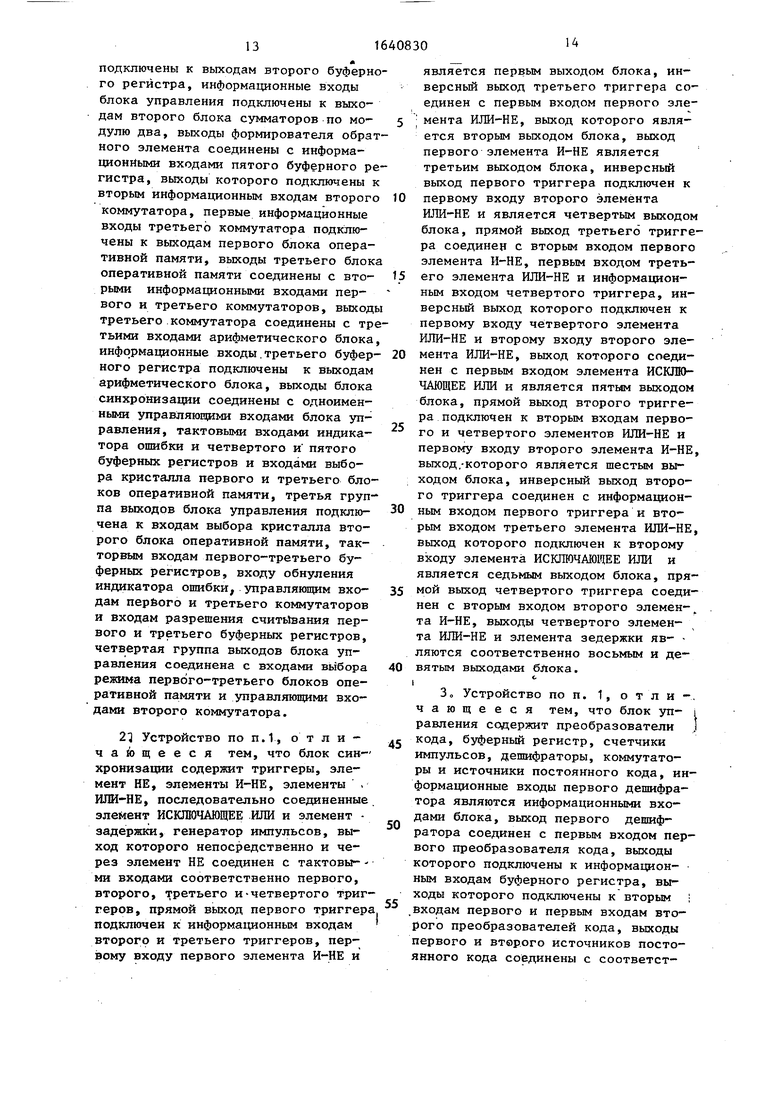

Арифметический блок 15 служит выполнения вычислений в соответсвии с выражением

10

г15,

.

408304

у (х1-х2) ф хЗ/modp

где х1-хЗ - элементы поля GF();

р - модуль образующего полицома для этого поля. На фиг.7 дан пример для случая m 3, р х + х + 1 .

Арифметический блок может быть выполнен (фиг.7) на элементах Й-НЕ 58 и сумматорах 58 по модулю два. На фиг. 7 показаны входы 60 и выходы 61. Возможное выполнение коммутаторов 4-6 на переключающих элементах 62 показано на фиг.8.

Индикатор 18 ошибки может быть выполнен на элементе ИЛИ 63, дешифраторе 64 и регистре 65 сдвига (фиг.9а) либо на элементе ИЛИ 63, дешифраторе 64 и счетчике 66 импульсов (фиг.96), либо на элементе ИЛИ 63 и 1К-тригге- ре 67 (фиг.9в). Во всех трех случаях элемент.ИЛИ 63 индицирует наличие хотя бы одного единичного сигнала на входах.

Блоки 1-3 оперативной памяти для элементов над полем GF(2W)имеют разрядность т.

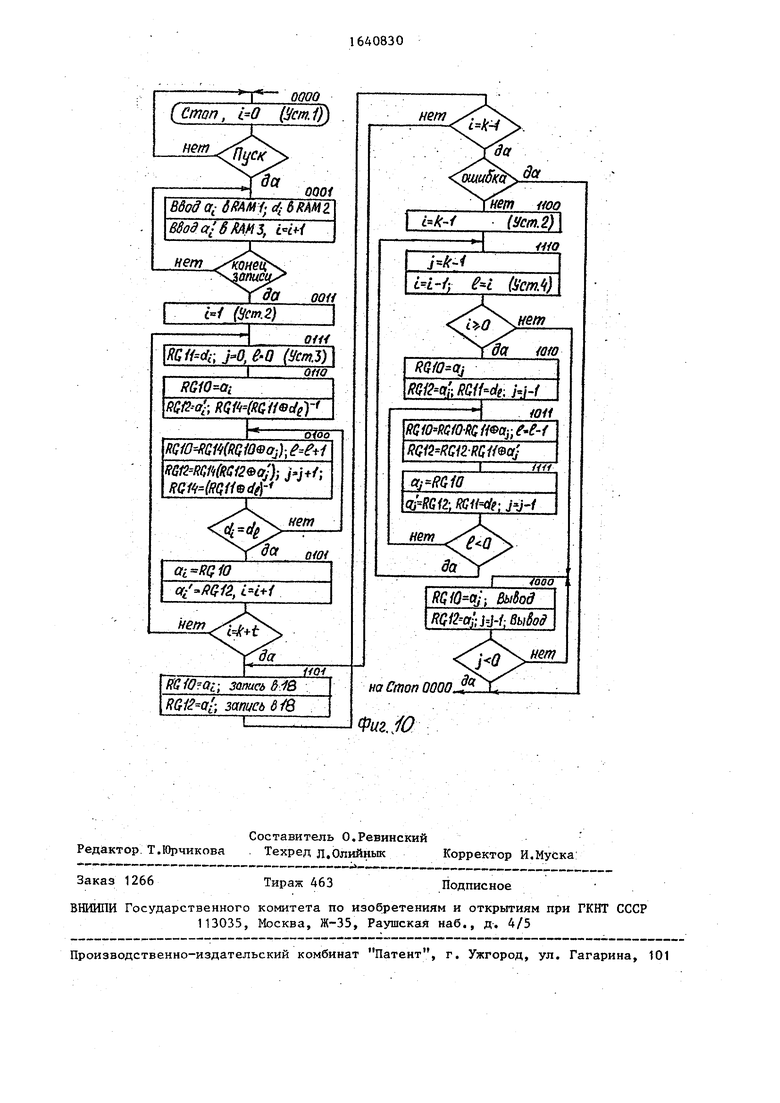

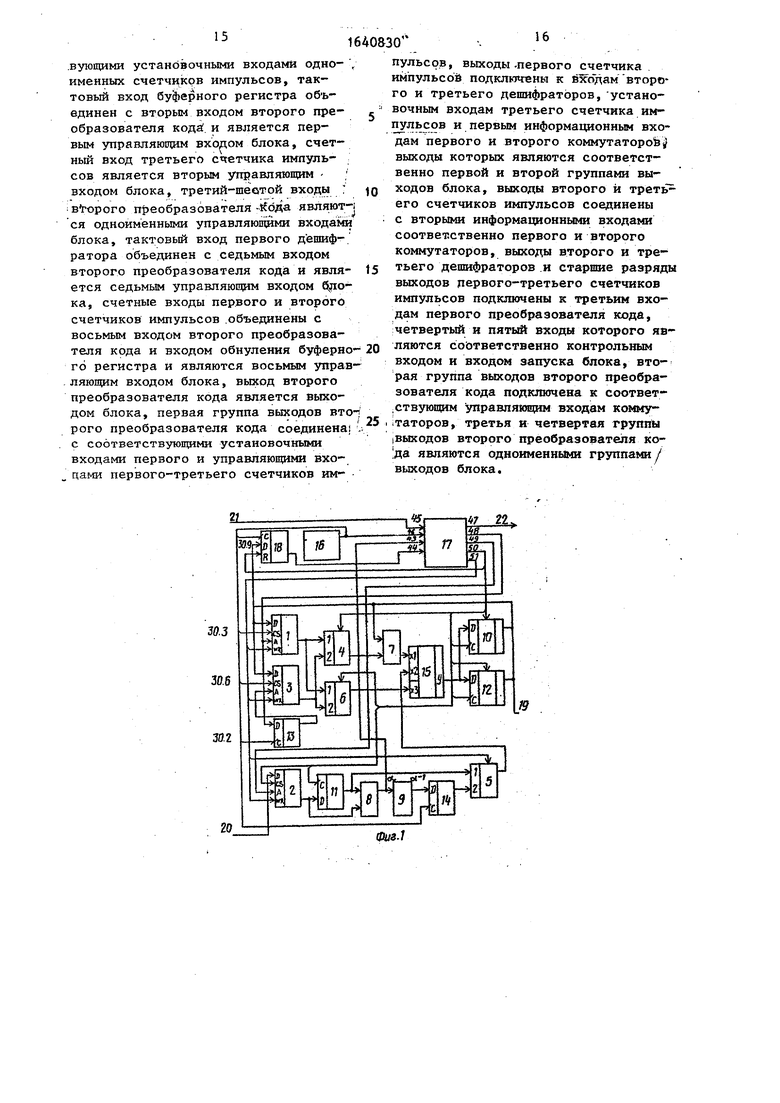

Устройство работает в соответствии с алгоритмом, блок-схема которого приведена на фиг.10. Здесь использованы следующие условие обозначения: j,j,l - состояние соответствующих

счетчиков 39-40 блока 17 уп-. равления, адресных для блоков 1-3;

, - установка счетчика 38 в соответствующее состояние;

- установка счетчика 40 в состояние, аналогичное счетчику 38;

, - увеличение или уменьшение состояния соответствующего счетчика 38, 39 на

20

25

30

35

40

45

.

50

55

Ч

единицу;

(а :) - содержимое ячейки блока 1 с адресом, равным состоянию счетчика 38(39), элемент поля, над которым задан код , РС{

(а:) - содержимое ячейки блока 3 с адресом, равным состоянию счетчика 38(39) для второго из двух одновременно обрабатываемых слов кода PCJ

(dj) - содержимое ячейки блока 2 с адресом iyU) , элемент поля, содержащий вспомогательную информацию о принятых элементах кода,

UG10-RG12, RG14 - содержимое соответствующего регистра (нумерация согласно фиг.1), запись в регистр 13 адреса обращения к первому блку 1 условно не показана, происходит постоянно при выполнении всех операций алгоритма,

, , - пересы - ка информации из ячеек i

блоков 1,3 и 2 соответственно в регистры 10,12 и 11,

aL RplPs a RG12 - запись в ячеку блоков 1 и 3 с адресом i информации из регистров 10 и 12 соответственно1, k - числб восстанавливаемых в каждо слове кода PC компонентов информации;

t - число анализируемых в каждом слове кода PC дополнительно принимаемых элементов для повшения достоверности. На фиг. 10 справа сверху каждой операции показан условный двоичный номер выполняемой в блоке 17 управления операции. Действия, выполняемые в течение первой и второй половины операции (одного периода тактовых последовательностей, вырабатываемых блоком 16 синхронизации), для удобства разделены горизонтальной чертой.

В исходном состоянии 0000 счетчик 36 в блоке 17 управления установлен в нулевое состояние, ожидается появление сигнала на входе 21 запуска устройства, с приходом которого разрешается переключение блока 17 управления в состояние 0001. При этом производится запись входной информации с шины 19 в блок 1 и 3-й вспомогательной информации с входов 20, соответствующей записываемым элементам кода, в блок 2 со сменой адреса после каждого цикла записи, В первой половине операции в блок 1 записываются элементы кода PC, являющиеся остатками от деления первого полинома переданной информации

к-,1 +

+ ...+ 34(D

А(х)

на двучлены вида р(х) x+dj, i 1,2,..., где а-, , А -т-разрядные двоичные коэффициенты, элементы поля, над которым задан код PC. Для расширенного кода PC включается

d; 0.

Одновременно в блок 2 записыва-ются элементы dC, адрес обращения к блокам 1 и 2 записывается в регистр 13. Во второй половине операции в блок 3 записываются элементы а- кода PC, являющиеся остатками от деления второго полинома переданной информации 1,

А Ы

ч- а

a

d . л 1

на тот же двучлен, и

(2) одновременно

0

5

0

5

0

5

0

изменяется адрес обращения к блоку 1. Для укороченных кодов PC часть разрядов элементов d; может быть выбрана нулевой. При этом разрядность блока 2 и регистра 11 может быть сокращена.

Запись информации продолжается до поступления сигнала конца записи, переводящего блок 17 управления в следующее состояние 0011 с очередным тактом блока 16 синхронизации (формирование данного сигнала не показано, он может, например, формироваться дополнительным дешифратором состояния счетчика 38 или поступать в устройство извне по концу приема

кодового слова кода PC). i

По данному сигналу начинается процедура декодирования. На первом этапе исправления стираний производится перевод из системы остаточных классов в обобщенную позиционную систему с вычислением k информационных и проверочных элементов для каждого из слов rfol и ( г ,01 принятой информации одновременно. Для первого слова кода PC вычисления производятся по рекуррентной формуле

rij (r ,i

/(d; © dp, где 1Ј i.k+t-1, 1ЈjЈj-1,

(3)

используя информацию блоков 1 и 2. Коэффициенты bj обобщенной позиционной системы находятся из равенства bj rj -,. для i 0,1,... ,k+t-1.

Для второго слова кода PC вычис-, ления аналогичны, используется ин- I формация блока 3 и та же информация блока 2.

В состоянии 0011 производится установка счетчика 38 и разрешается дальнейшее переключение в состояние . 0111. В данном состоянии (начало вьН, числения очередного коэффициента Ь:) производится чтение из блока 2 в регистр 11, установка счетчиков 39 и 40 в нулевое состояние к разрешается переключение блока 17 управления в состояние 0110.

В состоянии 0110 коммутатор 5 от- ключей и на входы 60.2 второго сомножителя блока 15 поступает нулевой элемент. Сначала выбирается кристалл в блоке 1 и элемент первого слова через первые входы коммутатора 6 и входы 60.3 слагаемого блока 15 записывается в регистр 10, адрес обращения к блоку 1 записывается в регистр 13. Затем выбирается кристалл в блоке 3 и через вторые входы коммутатора 6 и входы 60.3 слагаемого блока 15 элемент второго слова записывается в регистр 12. Одновременно выбирается кристалл в блоке 2, элемент с его выхода суммируется по модулю два с записанным ранее в регистр 11 на блоке 8 сумматоров. Полученная сумма сравнивается с нулем на дешифраторе 31 в блоке 17, причем результат сравнения запоминается для сохранения по окончании выборки кристалла блока 2 (для этого дешифратор 31 может содержать, например, элемент ИЛИ, выход которого подключен к D-входу D-триггера). На формирователе 9 вычисляется обратный сумме элемент, который записывается в регистр 14.

В следующем состоянии 0100 коммутатор 5 подключает к выходам информацию с вторых входов от регистра 14,1 коммутатор 4 подключает выходы блока 1, затем блока 3 к первым входам пер-( вого блока- 7 сумматоров, где она суммируется по модулю два с содержимым регистра 10 или 12 соответственно, результат умножается на содержимое - регистра 11 и вновь записывается в г регистр 10 или 12. Коммутатор 6 от{ ai-«,H® 4i

Lo

ключен, и на входы 60.3. слагаемого ч блока 15 поступает ноль. В первой0 ( половине цикла изменяется состояние

с счетчика 40, подключаются выхо- ды р егистра 10 и блока 1 по адресу j , во второй половине цикла изменя- ется состояние счетчика 39 и подклю- чаются выходы регистра 12 и блока 2

0 ;По адресу 1. Адрес на выходах регистра 13 (входах блока 3) сохраняется, и выбирается кристалл в блоке 3 по старому адресу j. Вычисления продолжаются до срабатывания дешифра5 тора 31 (dj dg), разрешающего переключение блока 17 в состояние 0101, в котором сначала подключаются выходы регистра 10, разрешается выборка в блока 1 в режиме записи, и инфор0 мация из регистра 10 записывается в блок 1, затем аналогично информация в блок 3 записывается из регистра 12 и адрес i блока 3 изменяется на единицу. Анализируется состояние счет5 чика 38. Если i«ЈLk+t, происходит воз- врат блока 17 управления в состоя- ние 0111, если i k+t, блок 17 управления переключается в состояние 1101.

0 В состоянии 1101 аналогично состоянию 0110 информация из блоков 1 и 3 записывается в регистры 10 и 12. Быт- ходы регистров 10 и 12 поочередно подключаются, и информация с них

,5 вводится в индикатор Т8 ошибки, анализирующий равенство ее нулю. Состояние счетчика 38 в конце каждого цикла уменьшается на единицу. Бели состояние счетчика 38 i k-1, разQ решается дальнейшее переключение блока 17 управления. При наличии хотя бы одного ненулевого проверочного элемента (ошибка) блок 17 управления переключается в исходное состояние

5 0000. При получении всех нулевых проверочных элементов блок 17 управления переключается в состояние 1100, соответствующее переходу к второму этапу декодирования - переводу инфорQ мации из обобщенной позиционной системы в исходную форму (1), (2) .При этом, счетчики 38-40 работают в режиме вычитания, k младших информационных элемента вычисляются по рекуррентной формуле

5

4 d|t j при при + l

(4)

где 0Јj Јk-1, aQ)XJf b,.

Значения коэффициентов позиционной системы а; находятся из равенства д. a t, состояние 1100 устанавливается счетчик 38, и разрешается переключение блока 17 управления в состоя- ние 1110, при котором состояние счетчика 38 уменьшается на единицу,, производится установка счетчиков 38 и 40, анализируется состояние счетчика 38. Если j 0 (единица в старшем разряде счетчика 38), разрешается переключение в состояние 1000, если нет - в состояние 1010.

В состоянии 1000 аналогично состоянию 0110 производится считывание информации из блока 1 в регистр 10, затем из блока 3 в регистр 12 с изменением адреса обращения к блокам 1, 3 на единицу. Одновременно с управляющего выхода 47 блока 17 управления формируется сигнал разрешения чтения информации с шины 19 декодирующего устройства (поочередно подключаемых выходов регистров 10 и 12). По окончании вывода декодированной информации (младшие коэффициенты из нулевого адреса блоков 1 и 3) по сигналу j .0 разрешается переключение блока 17 управления в исходное нулевое состояние.

В состоянии 1010 производится

чтение информации из блока 1 в ре- гистр 10, затем из блока 3 в регистр 12 аналогично состоянию 0110. Состоя ние счетчика 39 изменяется, производится запись в регистр 11 из блока 2 аналогично состоянию 0111, разрешается переключение в состояние 1011.

В состоянии 1011 производится из

5

0

0

5

0

5

В состоянии 1111 аналогично состоянию 0101 производится запись инфор- мации из регистра 10 в блок 1, затем, из регистра 12 в блок 3, изменяется адрес обращения к блокам 1,3. Дополнительно производится чтение из блока 2 в регистр 11 аналогично состоянию 0111, анализируется состояние счетчика 40. Если , разрешается переключение блока 17 управления в состояние 1110, если нет - в состояние 1011.

Индикатор 18 ошибки анализирует равенство нулю t старших элементов в обобщенной позиционной системе

( bfc-rt-e Ь|) При правильном без ошибок декодировании данное условие всегда выполняется, поскольку полиномы (1), (2) исходной информации могут содержать ненулевые коэффициенты только в k младших членах. Поскольку такой код PC имеет кодовое расстояние t+1 при t проверочных элементах, такой подход гарантирует обнаружение трансформации при наличии ошибок не более чем в t элементах каждого из параллельных слов кода PC. При большем числе ошибочных элементов вероятность необнаруженного искажения (случайного одновременного равенства нулю t проверочных элементов по m разрядов в двух словах кода PC) снижается примерно в 2tm раз. Например, для кода PC над полем 2е t 2 проверочных элемента снижают вероятность необнаруженной ошибки более чем в 10 раз, что обеспечивает высокую достоверность декодируемого сообщения.

Временная привязка работы всех 4 блоков устройства обеспечивается блоком 16 синхронизации.

Временная диаграмма на фиг.З по-

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для отображения информации на экране телевизионного индикатора | 1986 |

|

SU1695372A1 |

| Устройство для управления оперативной памятью | 1985 |

|

SU1291992A1 |

| Устройство для ввода информации | 1983 |

|

SU1145336A1 |

| ВЫЧИСЛИТЕЛЬНАЯ СИСТЕМА НА БАЗЕ МАТРИЦЫ ПРОЦЕССОРНЫХ ЭЛЕМЕНТОВ | 1998 |

|

RU2117326C1 |

| Процессор параллельной обработки | 1990 |

|

SU1797126A1 |

| Селекторный канал | 1983 |

|

SU1103218A1 |

| Устройство для формирования команд с аппаратной организацией циклических программ | 1979 |

|

SU942018A1 |

| УСТРОЙСТВО КОДИРОВАНИЯ-ДЕКОДИРОВАНИЯ ИНФОРМАЦИИ | 1994 |

|

RU2115231C1 |

| Устройство для управления вводом-выводом | 1989 |

|

SU1735859A1 |

| Мажоритарно-резервированный интерфейс памяти | 1990 |

|

SU1751766A1 |

Изобретение относится к вычис-- лительной технике. Его использование в системах передачи и переработки цифровой информации позволяет повысить достоверность декодирования иГ увеличить информативность устройства, которое содержит блоки 1, 2 оперативной памяти, коммутаторы 4, 5, блоки 7, 8 сумматоров по модулю два, формирователь 9 обратного элемента, буферные регистры 10, 11 и арифметический блок 15. Положительный эффект достигается благодаря введению блока 3 оперативной памяти, коммутатора 6, буферных регистров 12-14, блока 16 синхронизации, блока 17 управления и индикатора 18 ошибки. 2 з.п.ф-лы, 1 табл., 10 ии

менение состояния счетчика 40, комму-д5 казана в предположении,

татор 5 подключает к входам 60.2 второго сомножителя блока 15 выходы регистра 11, коммутатор 4 отключен, и на входы 60.1 первого сомножителя блока 15 через первый блок 7 сумма- CQ торов поступают сначала сигналы с выходов регистра 10, затем с регистра 12. На входы 60.3 слагаемого блока 15 через коммутатор 6 подключаются соответственно выходы блоков 1 и 3. При . l55 этом производятся вычисления для пер- вого и второго слов PC по формуле (4) и разрешается переключение блока 17 управления в состояние 1111.

пись в региртры и тригге дит по фронту переключе вого сигнала в единичный подключение выходов реги 12 происходит высоким ур ла управления, выбор кри ков 1-3 происходит при н не сигнала управления. В риода Т в- первой его пол мируется такт на регистр 17 управления и разрешае чение первых входов комм 4 и 6 и выходов регистра формируются такт на реги

что за-

пись в региртры и триггеры происходит по фронту переключения тактового сигнала в единичный уровень, подключение выходов регистров 10 и 12 происходит высоким уровнем сигнала управления, выбор кристалла блоков 1-3 происходит при низком уровне сигнала управления. В течение периода Т в- первой его половине формируется такт на регистр 36 блока 17 управления и разрешается подключение первых входов коммутаторов 4 и 6 и выходов регистра 10. Затем формируются такт на регистр 13. за11

поминающий адрес обращений k блоку 1, и такт на счетчик 40 блока 17 управления для изменения адреса обращения блоков 1-2, выборка которого производится во второй половине периода Т. Через время, достаточное для срабатывания блоков 1-3 и комбинационных элементов, формирует- , , записи в регистр 10. Одновременно начинается выборка из блока 3.. Выборка блока 2 производится одновременно с блоком 1 при записи или с блоком 3 при чтении. С задержкой, формируемой элементом 29, формируется такт записи из регистра 10 в индикатор 18 ошибки. Во второй половине, периода Т отключаются первые входы коммутаторов 4 и 6, выходы регистра 10 и выборка блока

I,подключаются вторые входы коммутаторов 4 и 6, выходы регистра 12. Через время, обеспечивающее срабатывание комбинационных элементов, формируются такты записи в регистры

II,12, 14 и запоминающий элемент дешифратора 31. С задержкой элемента 29 формируется второй такт записи в индикатор 18 ошибки из регистра 12. Затем заканчивается выборка блока 3, формируется такт изменения состояния счетчиков 38, 39 блока 17 управления и строб установки счетчиков 38-40.

Перевод в обобщенную позиционную систему дополнительных принятых элементов кода PC с анализом их равенства нулю на индикаторе 18 ошибки, управляющем через блок 17 управления процессом продолжения или отказа от декодировании, позволяет, таким образом, снижать вероятность необнаруженных искажений на несколько порядков, повышая достоверность декодируемой информации.

Поочередная обработка в едином арифметическом блоке двух кодовых / слов кода PC с фазовым сдвигом во времени процессов выбора кристалла и смены адреса блоков 1,3 оперативной памяти обеспечивает повышение информативности устройства.

e Формула изобретений

р e i

10

15

25

640830 12

мутаторы, формирователь обратного элемента и арифметический блок, выходы которого соединены с информационными входами первого буферного регистра , выходы которого подключены к первым входам первого блока сумматоров по модулю два и информационным входам первого блока оперативной памяти и являются информативной шиной устройства, выходы первого блока оперативной памяти соединены с первыми информационными входами первого коммутатора, выходы которого подключены к вторым входам первого блока сумматоров по модулю два, выходы которого и выходы второго коммутатора соединены соответственно с первыми и вторыми входами арифмети2Q ческого блока, информационные входы второго блока оперативной памяти являются установочными входами устройства, выходы второго блока оперативной памяти подключены к первым входам второго блока сумматоров по модулю два и информационным входам второго буферного регистра, выходы которого соединены с вторыми входами второго блока сумматоров по модулю два, выходы которого подключены к входам формирователя обратного элемента, отличающееся тем, что, с целью повышения достоверности декодирования и увеличения информативности, в него введены третий- пятый буферные регистры, третий блок оперативной памяти, третий коммутатор, индикатор ошибки, блок синхронизации и блок управления, вход запуска и выход которого являются соответственно входом запуска и управляющим выходом устройства, первая группа выходов блока управления соединена с адресными входами первого

45 блока оперативной памяти и информационными входами четвертого буферного регистра, выходы которого подключены к адресным входам третьего блока оперативной памяти, информацион- ные входы которого объединены с выходами третьего буферногр регистра и информационными входами первого блока оперативной памяти и индикатора ошибки, выход которого подключен к контрольному входу блока управления, вторая группа выходов которого сведи- йена с адресными входами второго блока оперативной памяти, первые информационные входы второго коммутатора

30

35

40

50

55

подключены к выходам второго буферного регистра, информационные входы блока управления подключены к выходам второго блока сумматоров по мо- дулю два, выходы формирователя обратного элемента соединены с информационными входами пятого буферного регистра, выходы которого подключены к вторым информационным входам второго коммутатора, первые информационные входы третьего коммутатора подключены к выходам первого блока оперативной памяти, выходы третьего блока оперативной памяти соединены с вто- рыми информационными входами первого и третьего коммутаторов, выходы третьего коммутатора соединены с третьими входами арифметического блока, информационные входы третьего буфер- ного регистра подключены к выходам арифметического блока, выходы блока синхронизации соединены с одноименными управляющими входами блока управления, тактовыми входами индикатора ошибки и четвертого и пятого буферных регистров и входами выбора кристалла первого и третьего блоков оперативной памяти, третья группа выходов блока управления подклю- чена к входам выбора кристалла второго блока оперативной памяти, так- торвым входам первого-третьего буферных регистров, входу обнуления индикатора ошибки, управляющим вхо- дам первого и третьего коммутаторов и входам разрешения считывания первого и третьего буферных регистров, четвертая группа выходов блока управления соединена с входами выбора режима первого-третьего блоков оперативной памяти и управляющими входами второго коммутатора.

2 Устройство поп.1, отли- чающееся тем, что блок сив- хронизации содержит триггеры, элемент НЕ, элементы И-НЕ, элементы . ИЛИ-НЕ, последовательно соединенные элемент ИСКЛЮЧАЮЩЕЕ ИЛИ и элемент - задержки, генератор импульсов, выход которого непосредственно и через элемент НЕ соединен с тактовы- - ми входами соответственно первого, второго, третьего и-четвертого триггеров, прямой выход первого триггера подключен к информационным входам второго и третьего триггеров, первому входу первого элемента И-НЕ и

5

0 5 0 0 5 0

0

5

является первым выходом блока, инверсный выход третьего триггера соединен с первым входом первого элемента ИЛИ-НЕ, выход которого является вторым выходом блока, выход первого элемента И-НЕ является третьим выходом блока, инверсный выход первого триггера подключен к первому входу второго элемента ИЛИ-НЕ и является четвертым выходом блока, прямой выход третьего триггера соединен с вторым входом первого элемента И-НЕ, первым входом третьего элемента ИЛИ-НЕ и информационным входом четвертого триггера, инверсный выход которого подключен к первому входу четвертого элемента ИЛИ-НЕ и второму входу второго элемента ИЛИ-НЕ, выход которого соединен с первым входом элемента ИСКЛЮЧАЮЩЕЕ ИЛИ и является пятым выходом блока, прямой выход второго триггера подключен к вторым входам первого и четвертого элементов ИЛИ-НЕ и первому входу второго элемента И-НЕ, выход .-которого является шестым выходом блока, инверсный выход второго триггера соединен с информационным входом первого триггера и вторым входом третьего элемента ИЛИ-НЕ, выход которого подключен к второму входу элемента ИСКЛЮЧАЮЩЕЕ ИЛИ и является седьмым выходом блока, прямой выход четвертого триггера соединен с вторым входом второго элемен-. та И-НЕ, выходы четвертого элемента ИЛИ-НЕ и элемента зедержки яв- - ляются соответственно восьмым и девятым выходами блока.

, i

3 Устройство по п. 1, отличающееся тем, что блок уп- i равления содержит преобразователи j кода, буферный регистр, счетчики импульсов, дешифраторы, коммутаторы и источники постоянного кода, информационные входы первого дешифратора являются информационными входами блока, выход первого дешифратора соединен с первым входом первого преобразователя кода, выходы которого подключены к информационным входам буферного регистра, выходы которого подключены к вторым входам первого и первым входам второго преобразователей кода, выходы первого и второго источников постоянного кода соединены с соответствующими установочными входами одно- , именных счетчиков импульсов, тактовый вход буферного регистра объединен с вторым входом второго пре- - образователя кода и является первым управляющим входом блока, счетный вход третьего счетчика импульсов является вторым управляющим входом блока, третий-шеотой входы JQ второго преобразователя являют-j ся одноименными управляющими входами блока, тактовый вход первого дешифратора объединен с седьмым входом второго преобразователя кода и явля- 15 ется седьмым управляющим входом блока, счетные входы первого и второго счетчиков импульсов объединены с восьмым входом второго преобразователя кода и входом обнуления буферно- 20 го регистра и являются восьмым управляющим входом блока, выход второго преобразователя кода является выходом блока, первая группа выходов второго преобразователя кода соединена) , с соответствующими установочными входами первого и управляющими вхо- цами первого-третьего счетчиков импульсов, выходы-первого счетчика импульсов подключены к входам второго и третьего дешифраторов, установочным входам третьего счетчика импульсов и первым информационным входам первого и второго коммутаторов выходы которых являются соответственно первой и второй группами выходов блока, выходы второго и треть - его счетчиков импульсов соединены с вторыми информационными входами соответственно первого и второго коммутаторов, выходы второго и третьего дешифраторов и старшие разряды выходов первого-третьего счетчиков импульсов подключены к третьим входам первого преобразователя кода, четвертый и пятый входы которого являются соответственно контрольным входом и входом запуска блока, вторая группа выходов второго преобразователя кода подключена к соответствующим управляющим входам коммутаторов, третья и четвертая группы выходов второго преобразователя ко- да являются одноименными группами/ выходов блока.

Фиг. 2

43

50

47

HaSLSW

Ha RAM11M), MM3(UR}

HaSLSM .

51

HO RAM 2 (WR)

Фиг. 5

(Риг. 6

i

Гг-I п-о г-тТш- -... wj -К

из - г 39н - W

U/J

7ш

8/

Г

f/f

U

Id

L.

-О

Ј9

UJ3fi

Гш

шщ

ш-

1

U/Jfi

7ш

O/VD/

№$

°3

Ш СУ

У

IW

IV

да

/аг

Г 0000

(Стоп, (Уст.1)}

Ввод QitWAM{-fc/i&R№2.

В8одаг{вММЗ,

OOff

tW (frm.2)

J

Q1H

RGfacTi; e-0 (УстЗ) - I57P0-

BG&ffb WM5//«(/Ј)

-f

OjOO

RGf№Gft(RGfQ®0j);

ffSfcRMfMaeaj), RGK(RG1lQ ifr1

нет

otot

cfi -WW,

jfO-f

запись &1в

запись в SB

L

Составитель О.Ревинский Редактор Т.Юрчикова Техред Л.Олийнык Корректор И.Муска

Заказ 1266

Тираж 463

ВНИИПИ Государственного комитета по изобретениям и открытиям при ГКНТ СССР 113035, Москва, Ж-35, Раушская наб., д. 4/5

нет «оо

±

(Уст.2) I

wo

(Уст4)

да wo

RGfaQj

Mfrvjift&fitK Ы-t

юн

RGfO PGfO-RC№ar,

/ g/gg/ gyg-/ g/ g;

(Ј№&, RGWf;

Выбод

К№а ;М-1;вы6о0

на Стоп 0000 Ji Фиг,{0

Подписное

| Устройство декодирования линейногоциКличЕСКОгО КОдА | 1979 |

|

SU809568A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

| Техника средств связи | |||

| Серия: Техника проводной связи, 1983, № 7, с.29, рис.1. | |||

Авторы

Даты

1991-04-07—Публикация

1988-07-29—Подача