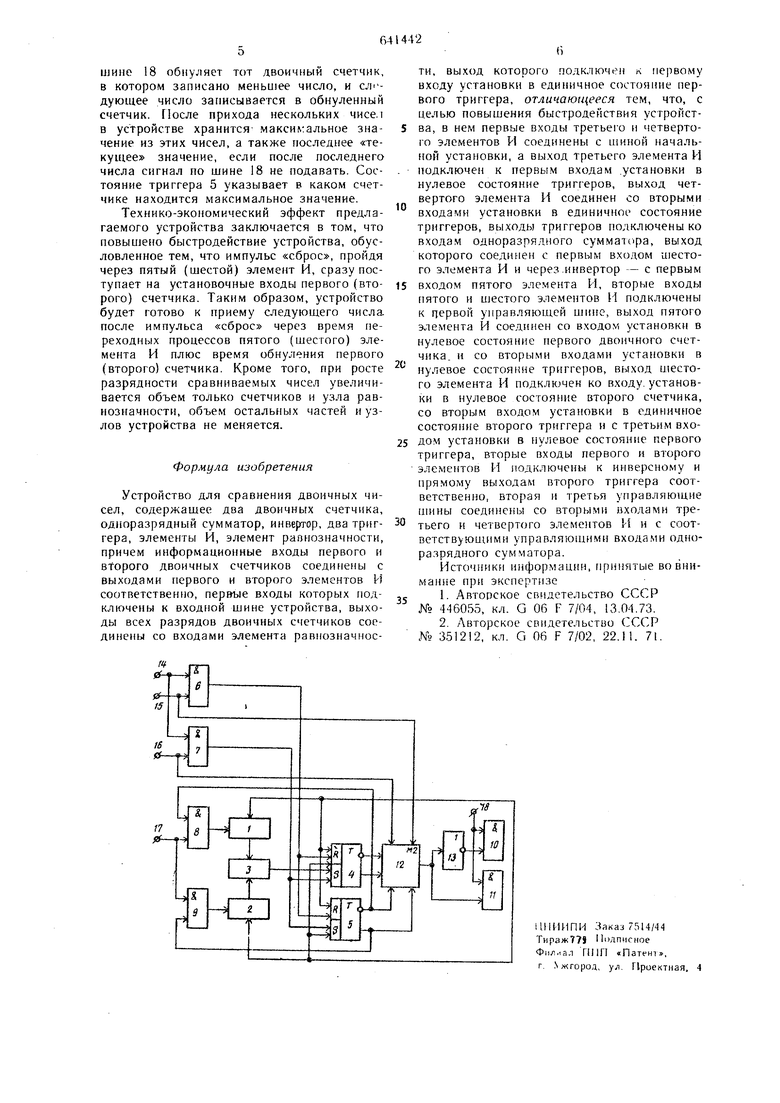

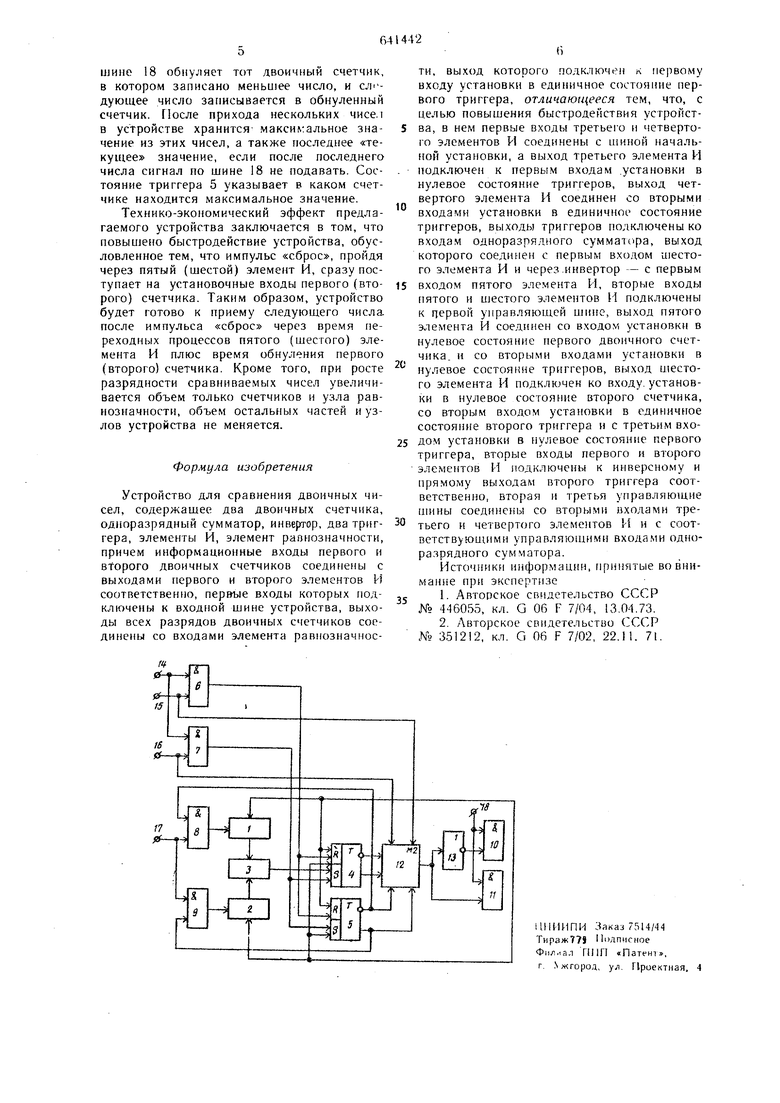

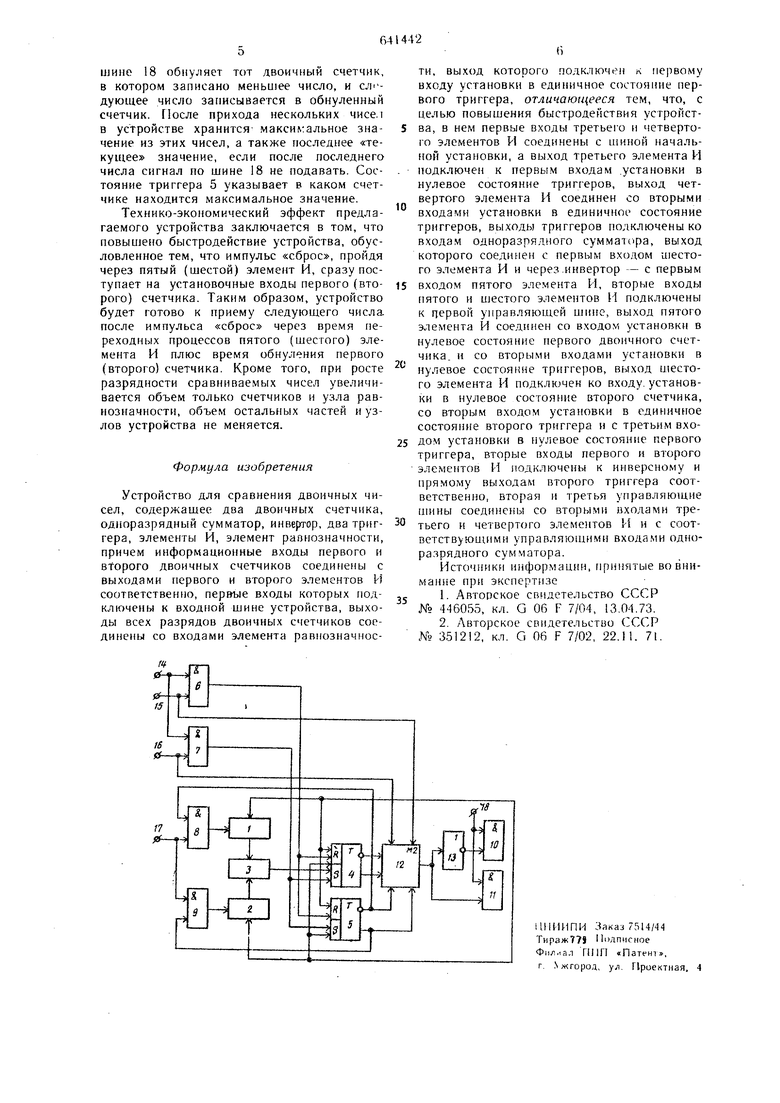

гается тем, что в устройстве первые входы третьего и четвертого элементов И соединены с тиной начальной установки, а выход третьего элемента И подключен к первым входам установки в нулевое состояние триггеров, выход четвертого элемента И соединен со вторыми входами установки в единичное состояние триггеров, выходы триггеров подключены ко входам одноразрядного сумматора, выход которого соединен с первым входом шестого элемента И и чере инвертор - с первым входом пятого элемента И, вторые входы пятого и шестого элементов И подключены к первой управляющей шине, выход пятого элемента И соединен со входом установки в н аевое состояние первого двоичного счетчика и со вторыми входами установки в нулевое состояние триггеров, выход шестого элемента И подключен ко входу установки в нулевое состояние второго счетчика, со вторым входом установки в единичное состояние второго триггера и с третьим входом установки в нулевое состояние первого триггера, вторые входы первого и второго элементов И подключены к инверсному и прямому зыходам второго триггера соответственно, вторая и третья управляюшие шины соединены со вторыми входами третьего и четвертого элементов И и с соответствующими управляюш,ими входами одноразрядного сумматора. Блок-схема устройства представлена на чертеже. Устройство содержит двоичные счетчики 1, 2, элемент равнозначности 3, триггеры 4, 5, элементы И 6, 7, 8, 9, 10, 11, одноразрядный сумматор 12, инвертор 13, входные шины 14, 15, 16, 17, 18. Устройство работает следующим образом. Если из входных последовательностей, представленных числоимпульсным кодом, необходимо выбрать минимальное значение, по шине 15 подается разрешающий потенциал. Сигнал, поступающий по шине 14, перед приходом первого .числа устанавливает триггеры 4, 5, счетчики 1, 2 в состояние «О (цепи обнуления счетчиков на чертеже не показаны). Триггер 5 подает разрешение на элемент И 8, и первое число запишется в счетчик 1. Одноразрядный сумматор 12 вырабатывает логичес кую функцию Fi2 abc + abc-f аЬс + аЪс где 3 а выходы триггера 4; biЪ - выходы триггера 5; с - сигнал по шине 15; с - сигнал по шине 16. После записи первого числа поступает сигнал по шине 18; который пройдет через элемент И 11(|2 аЬс 1), и установит в состояние «О счетчик 2, триггер 4 и в состояние «1 триггер 5, подавая разреп1ение на элемент И 9. Второе число запишется в счетчик 2. Элемент равнозначности 3 сравнивает число, записанное в двоичном счетчике 1, с числом, записываемым в двоичном счетчике 2, и в момент их равенства вырабатывает импульс, устанавливающий триггер 4 в состояние «Ь. Пусть, например, второе число больше первого (или равно ему). Триггер 4 устанавливается в состояние «I. Импульс «сброс пройдет через элемент И II (Fi2 ) и установит в состояние «О двоичный счетчик 2, в котором записано большее значение, и триггер 4, а в состояние «1 триггер 5, подавая разрешение на элемент И 9. Если же второе число меньше первого, состояние триггера 4 не изменится. Сигнал поД1ине 18 пройдет через элемент И 10 ( l) и установит в состояние «О двоичный счетчик 1, в котором записано большее значение, и триггеры 4, 5, подавая разрешение на двоичный счетчик I и т.д. Каждое последующее число в момент записи сравнивается с записанным (минимальным из всех предыдущих), факт сравнения фиксируется. Сигнал по шине 18 обнуляет тот двоичный счетчик, в котором записано большее число, и следующее число записывается в обнуленный счетчик. После прихода нескольких чисел в устройстве хранится минимальное значение из этих чисел, а также последнее значение числа, если после его записи управляющий сигнал по шине 18 не подавать. Состояние триггера 5 указывает, в каком счетчике находится минимальное значение. Если из входных последовате45ьностей, представленных числоимпульсным кодом, необходимо выбрать максимальное число, по шине 16 поступает разрешающий потенциал.- Сигнал, поступающий на шину 14, перед приходом первого числа, устанавливает триггеры 4, 5 в состояние «1, двоичные счетчики 1,2 - в состояние «О. Триггер 5 подает разрешение на элемент И 9, и первое число запишется в двоичный счетчик 2. Сигнал по imiHe 18 пройдет через элемент И 10( l) и установит в состояние «О двоичный счетчик I и триггеры 4, 5, подавая разрешение на элемент И 8. Второе число запишется в двоичный счетчик 1. Если второе число больше первого (или равно ему), триггер 4 установится в состояние I. Сигнал по шине 18 пройдет через элемент И 11 (Ffj аЪс I) и установит в состояние «О двоичный счетчик 2, в котором записано меньшее значение, и триггер 4, а в состояние «I триггер 5, подавая разрешение на двоичный счетчик 2. Если же второе число меньше первого, состояние триггера 4 не изменится. Импульс «сброс пройдет через элемент И 10 l и установит в состояние «О счетчик 1, в котором записано меньшее число, и триггеры 4, 5, подавая разрешение на счетчик 1 и т. д. Каждое последуюш.ее число в момент записи сравнивается с записанным (максимальным из всех предыдущих), момент сравнения фиксируется, импульс по

шине 18 обнуляет тот двоичный счетчик, в котором записано меньшее число, и CJ} дующее число записывается в обнуленный счетчик. После прихода нескольких чисе.1 в устройстве хранится- максимальное значение из этих чисел, а также последнее «текущее значение, если после последнего числа сигнал по шине 18 не подавать. Состояние триггера 5 указывает в каком счетчике находится максимальное значение.

Технико-экономический эффект предлагаемого устройства заключается в том, что повышено быстродействие устройства, обусловленное тем, что импульс «сброс, пройдя через пятый (шестой) элемент И, сразу поступает на установочные входы первого (второго) счетчика. Таким образом, устройство будет готово к приему следующего числа после импульса «сброс через время переходных процессов пятого (шестого) элемента И плюс время обнуления первого (второго) счетчика. Кроме того, при росте разрядности сравниваемых чисел увеличивается объем только счетчиков и узла равнозначности, объем остальных частей и узлов устройства не меняется.

Формула изобретения

Устройство для сравнения двоичных чисел, содержащее два двоичных счетчика, одноразрядный сумматор, инвертор, два триггера, элементы И, элемент равнозначности, причем информационные входы первого и второго двоичных счетчиков соединены с выходами первого и второго элементов И соответственно, первые входы которых подключены к входной шине устройства, выходы всех разрядов двоичных счетчиков соединены со входами элемента равиозначности, вы.ход которого подключен к первому входу установки в единичное состояние первого триггера, отличающееся тем, что, с целью повышения быстродействия устройства, в нем первые входы третьего и четвертого элементов И соединены с шиной начальной установки, а выход третьего элемента И подключен к первым входам .установки в нулевое состояние триггеров, выход четвертого элемента И соединен со вторыми входами установки в единичное состояние триггеров, выходы триггеров подключены ко входам одноразрядного сумматора, выход которого соединен с первым входом шестого элемента И и через .инвертор - с первым 5 входом пятого элемента И, вторые входы пятого и шестого элементов i подключены к первой управляющей шинч, выход пятого элемента И соединен со входом установки в нулевое состояние первого двоичного счетчика, н со вторыми входами установки в нулевое состояние триггеров, выход шестого элемента И подключен ко входу, установки в нулевое состояние второго счетчика, со вторым входом установки в единичное состояние второго триггера и с третьим вхо5 дом установки в нулевое состояние первого триггера, вторые входы первого и второго - элементов Н подключены к инверсному и прямому выходам второго триггера соответственно, вторая и третья управляющие шины соединены со вторыми входами третьего и четвертого элементов М и с соот0ветствующими управляющими входами одноразрядного сумматора.

Источиики информации, во внимание при экспертизе

1Авторское свидетельство СССР

5 № 446055, кл. G 06 F 7/04, 13.04.73.

2Авторское свидетельство СССР № 351212, кл. G 06 F 7/02, 22.11. 71.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для определения минимального числа | 1974 |

|

SU531150A1 |

| Устройство для определения свойств полноты логических функций | 1984 |

|

SU1170446A1 |

| Устройство для суммирования последовательных кодов | 1984 |

|

SU1254472A1 |

| Модуль интегрирующей вычислительной структуры | 1982 |

|

SU1101821A1 |

| Устройство для сравнения двоичных чисел | 1975 |

|

SU563674A1 |

| Аналого-цифровой преобразователь с цифровой коррекцией погрешностей | 1978 |

|

SU788374A1 |

| Устройство для сравнения и преобразования двоичных чисел | 1977 |

|

SU696441A1 |

| Устройство для построения программируемых логических автоматов | 2023 |

|

RU2814507C1 |

| Комбинаторное устройство | 1981 |

|

SU991432A1 |

| МОДУЛЬ ВВОДА-ВЫВОДА СИСТЕМЫ ЦИФРОВОГО УПРАВЛЕНИЯ | 1991 |

|

RU2032201C1 |

Авторы

Даты

1979-01-05—Публикация

1977-01-25—Подача