Изобретение относится к вычислительной технике и- предназначено для использования в решающих блоках цифровых интегрирующих структур, а также может быть использовано в процессорах цифровых вычислительных машин.

Целью изобретения является повьше- ние быстродействия.

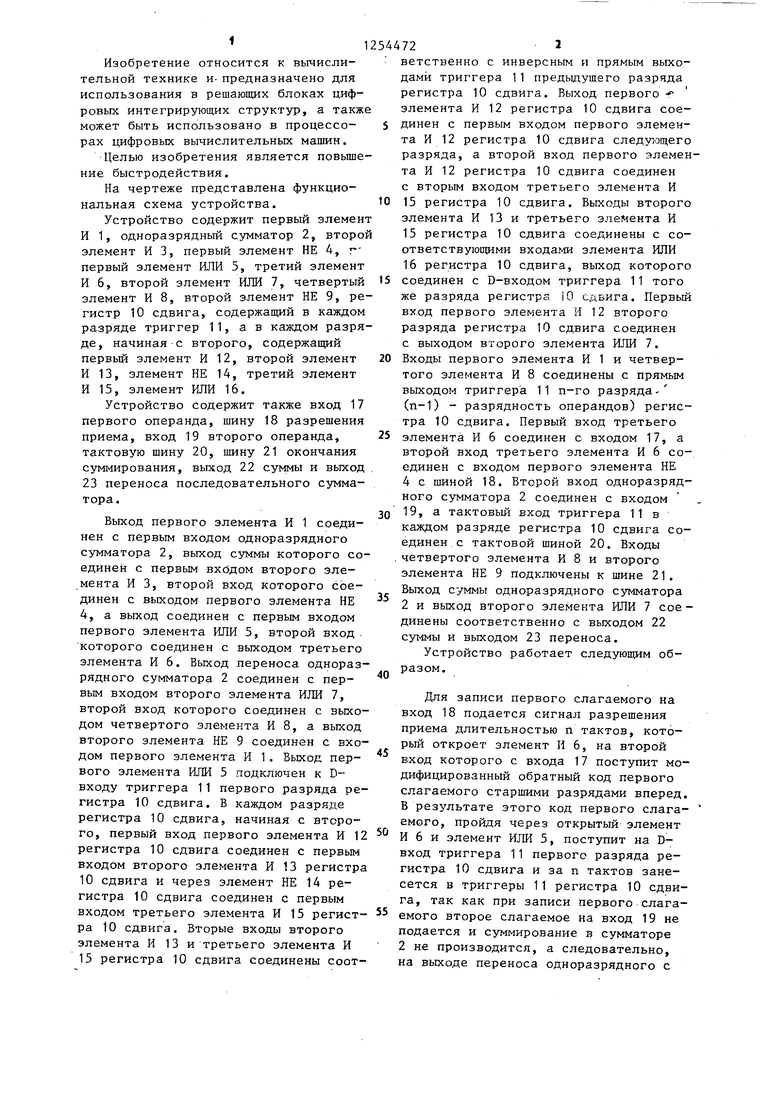

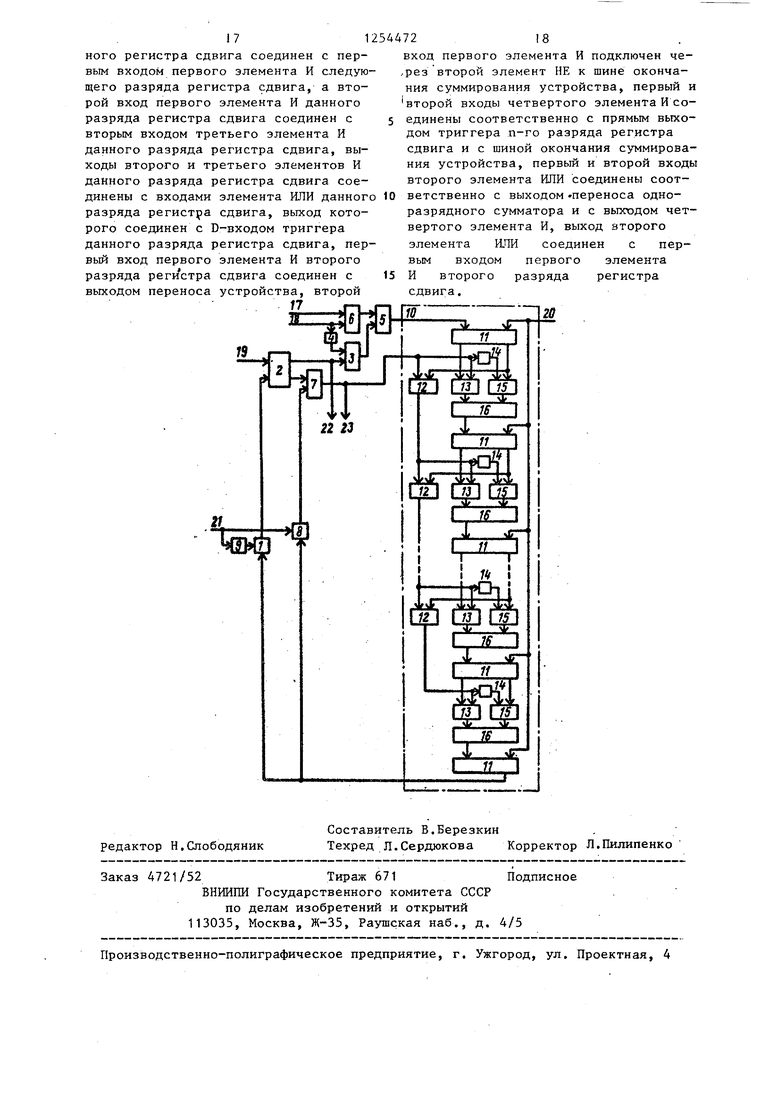

На чертеже представлена функциональная схема устройства.

Устройство содержит первый элемент И 1, одноразрядный сумматор 2, второй элемент И 3, первый элемент НЕ 4, г первый элемент ИЛИ 5, третий элемент И 6, второй элемент ИЛИ 7, четвертый элемент И 8, второй элемент НЕ 9, регистр 10 сдвига, содержащий в каждом разряде триггер 11, а в каждом разряде, начиная с второго, содержащий первый элемент И 12, второй элемент И 13, элемент НЕ 14, третий элемент И 15, элемент ИЛИ 16.

Устройство содержит также вход 17 первого операнда, шину 18 разрешения приема, вход 19 второго операнда, тактовую шину 20, шину 21 окончания сз мирования, выход 22 суммы и выход 23 переноса последовательного сумматора.

Выход первого элемента И 1 соединен с первым входом одноразрядного сумматора 2, выход суммы которого соединен с первым вхбдом второго элемента ИЗ, второй вход которого соединен с выходом первого элемента НЕ 4, а выход соединен с первым входом первого элемента ИЛИ 5, второй вход которого соединен с выходом третьего элемента И 6. Выход переноса одноразрядного сумматора 2 соединен с первым входом второго элемента ИЖ 7, второй вход которого соединен с выходом четвертого элемента И 8, а выход второго элемента НЕ 9 соединен с входом первого элемента И 1. Выход первого элемента ИЛИ 5 подключен к D- входу триггера 11 первого разряда регистра 10 сдвига. В каждом разряде регистра 10 сдвига, начиная с второго, первый вход первого элемента И 12

регистра 10 сдвига соединен с первым входом второго элемента И 13 регистра 10 сдвига и через элемент НЕ 14 регистра 10 сдвига соединен с первым входом третьего элемента И 15 регист- ра 10 сдвига. Вторые входы второго элемента И 13 и третьего элемента И 15 регистра 10 сдвига соединены сооте

1254472 2

ветственно с инверсным и прямым выходами триггера 11 предыдущего разряда регистра 10 сдвига. Выход первого - элемента И 12 регистра 10 сдвига соединен с первым входом первого элемента И 12 регистра 10 сдвига следут-эщего

разряда, а второй вход первого элемента И 12 регистра 10 сдвига соединен с вторым входом третьего элемента И 15 регистра 10 сдвига. Выходы второго элемента И 13 и третьего элемента И

15регистра 10 сдвига соединены с соответствующими входами элемента ИЛИ

16регистра 10 сдвига, выход которого соединен с D-входом триггера 11 того же разряда регистра 10 сдвига. Первый вход первого элемента И 12 второго разряда регистра 10 сдвига соединен

с выходом второго элемента ИЛИ 7. Входы первого элемента И 1 и четвертого элемента И 8 соединены с прямым выходом триггера 11 п-го разряда- (п-1) - разрядность операндов) регистра 10 сдвига. Первый вход третьего элемента И 6 соединен с входом 17, а второй вход третьего элемента И 6 соединен с входом первого элемента НЕ 4 с шиной 18. Второй вход одноразрядного сумматора 2 соединен с входом 19, а тактовый вход триггера 11 в каждом разряде регистра 10 сдвига соединен с тактовой шиной 20. Входы .четвертого элемента И 8 и второго элемента НЕ 9 подключены к шине 21. Выход суммы одноразрядного сумматора 2 и выход второго элемента ИЛИ 7 сое - динены соответственно с выходом 22 суммы и выходом 23 переноса.

Устройство работает следующим образом.

Для записи первого слагаемого на вход 18 подается сигнал разрешения приема длительностью п тактов, который откроет элемент И 6, на второй вход которого с входа 17 поступит модифицированный обратный код первого слагаемого старшими разрядами вперед. В результате этого код первого слага- емого, пройдя через открытый элемент И 6 и элемент ИЛИ 5, поступит на D- вход триггера 11 первого разряда регистра 10 сдвига и за п тактов занесется в триггеры 11 регистра 10 сдвига, так как при записи первого слагаемого второе слагаемое на вход 19 не подается и суммирование в сумматоре 2 не производится, а следовательно, на выходе переноса одноразрядного с

сумматора 2 сигнал переноса будет отсутствовать и на выходе элемента И 8, который выделяет при суммировании переполнение за знаковые разряды для коррекции результата суммирования, тоже будет нулевой сигнал, то на выходе элемента ИЛИ 7 будет нулевой сигнал и все элементы И 12 и элемен- ты И 13 в каждом разряде регистра 10 сдвига будут закрыты, а на выходах элементов НЕ 14 регистра 10 сдвига будут единичные сигналы, которые откроют все элементы И 15 в каждом разряде регистра 10 сдвига, объединив тем самьм триггеры 11 регистра 10 сдвига через открытые элементы И 15 и элементы ИЛИ 16 регистра 10 сдвига в последовательный регистр сдвига и обеспечив тем самым занесение,кода первого слагаемого. При этом стирание ранее имевшейся информации в этих г триггерах 11 регистра 10 сдвига обеспечивается подачей сигнала инверсного сигналу разрешения записи с выхода элемента НЕ 4 на вход элемента ИЗ.

.Коды слагаемых имеют (п-1)-й разряд, причем в первых двух разрядах распо- ла гаются знаковые разряды модифицированного обратного кода, а с третьего по (п-1)-й разряд разрешаются число- вые разряды со старшего по младший. Последний п-й разряд является служебным и служит для временного хранения возникающего при суммировании переполнения за знаковые разряды, которое используется для соответствуищей алгоритму суммирования в обратных кодах коррекции результата. После записи первого слагаемого сигнал разрешения

записи на пшне 18 исчезает и элемент И 6 закрывается, а на выходе элемента НЕ .4 появляется единичный сигнал, который открывает элемент И 3. Одновременно тактирующие импульсы с шины 20 начинают сдвигать с прямого выхода последнего п-го триггера 11 регистра 10 сдвига через открытый элемент И 1 (на выходе, элемента НЕ 9 запирающий сигнал появляется лишь в конце суммирования в п-м такте) на вход одноразрядного сумматора 2 последовательный модифицированный обратный код первого слагаемого старшими разрядами вперед, а на второй вход этого сумматора 2 одновременно начинает поступать с. входа 19 последовательный модифицированный обратный код второго слагаемого старшими разрядами вперед. Одно-г разрядный сумматор 2 начинает в каждом такте суммировать одноименные разряды слагаемых, начиная со старших разрядов, и вьщавать соответствукмдие сигналы на выходы суммы и переноса сумматора 2. При этом, если g суммируемых разрядах хотя бы у одного из слагаемых будет .О, то в соответствующем такте сигнал на выходе переноса сумматора 2 будет отсутствовать, а значение суммы с выхода суммы сумматора 2 пройдет через открытый элемент И 3 и через элемент ИПИ 5 и будет записываться в триггер 11 первого разряда регистра 10 сдвига, и с помощью тактирующих импульсов, поступающих на шину 20, будет сдвигаться в соответствующий рдзряд.

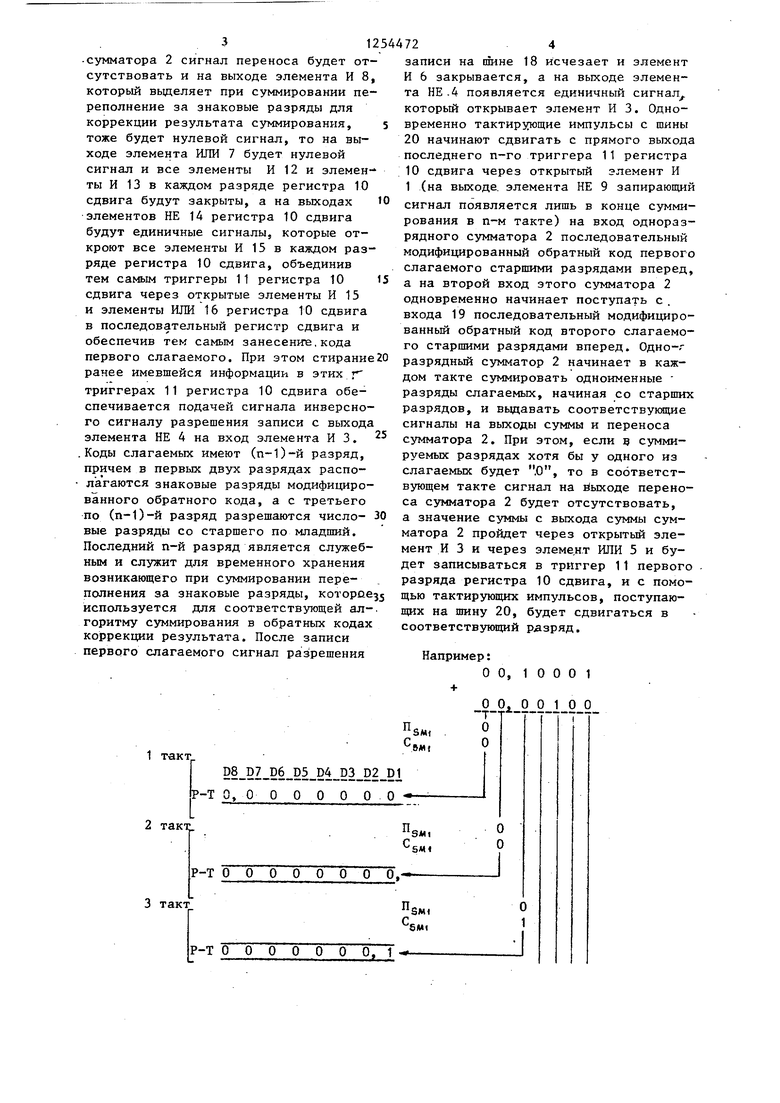

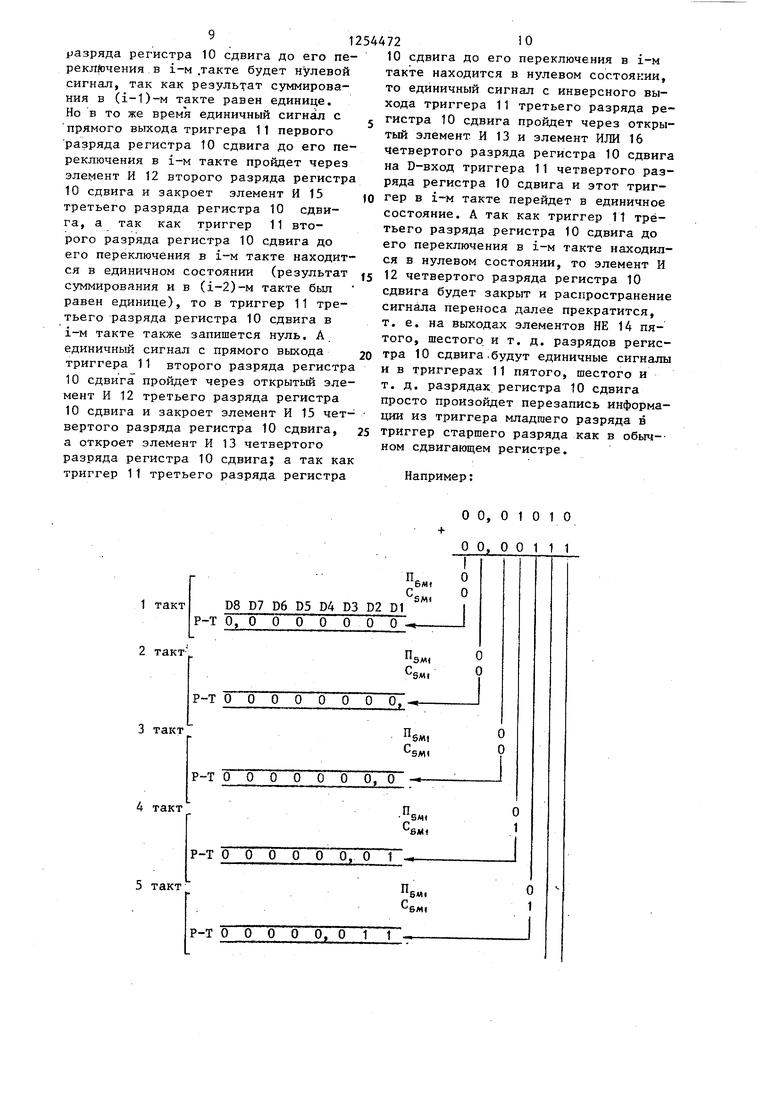

Например:

00, 10001 +

О 0. О О 1 О О

в приведенном примере использованы следующие обозначения:

П,

- значение переноса однораз-

iJ-TIlп

рядного сумматора I в 1-м такте;

SMi значение суммы одноразрядного сумматора 2 в i-ом такте;.

Р-Т - результат суммирования в i-M такте;

D1-D8 - прямые входы триггеров 11 с первого по восьмой регистра 10 сдвига{

Р1-Р8 - разряды с первого по восьмой результата.

Последний, п-й такт (в приведенном примере 8-й такт) используется для устранения возникающего в некоторых случаях переноса за знаковые разряды в получаемом результате суммирования и соответствующий алгоритму суммиро- рания в обратных кодах Koppeifuroi этого результата (в приведённом примере такой перенос отсутствует).

Если же S i-x разрядах обоих слагаемых находятся 1, то на выходе переноса сумматора 2 в i-м такте по- 55 явится единичный сигнал, который про- идет через элемент ИЛИ 7 и поступит на входы элемента И 12, элемента И 13

0

5

0

5

0

5

и элемента НЕ 14 второго разряда.регистра 10 сдвига, закрыв тем самым элемент И 15 второго разряда регистра 10 сдвига и открыв элемент И 12 и элемент И 13 второго разряда регистра 10 сдвига, а результат суммы с выхода суммы сумматора 2 поступит на D- вход триггера 11 первого разряда регистра 10 сдвига. При этом, если результат суммирования в (1-1)-м такте равен нулю, то в i-м такте на прямом выходе триггера 11 первого разряда регистра 10 сдвига будет нулевой сигнал и элемент И 12 второго, разряда регистра 10 сдвига будет закрыт, а на инверсном выходе триггера 11 будет единичный сигнал, который пройдет te- рез открытый элемент И 13 и через элемент ИЛИ 16 второго разряда регистра 10 сдвига и поступит на D-вход триггера 11 второго разряда регистра 10 сдвига. В результате в i-м такте при суммировании двух единиц в триггер 11 первого разряда регистра 10 сдвига запишется результат суммы в i-M такте, т. е, О, а в триггер 11 второго разряда регистра 10 сдвига запишется измененный с учетом возникшего в i-M такте переноса результат суммирования (i-l)-ro такта, т. е. ;сто О з; Например:

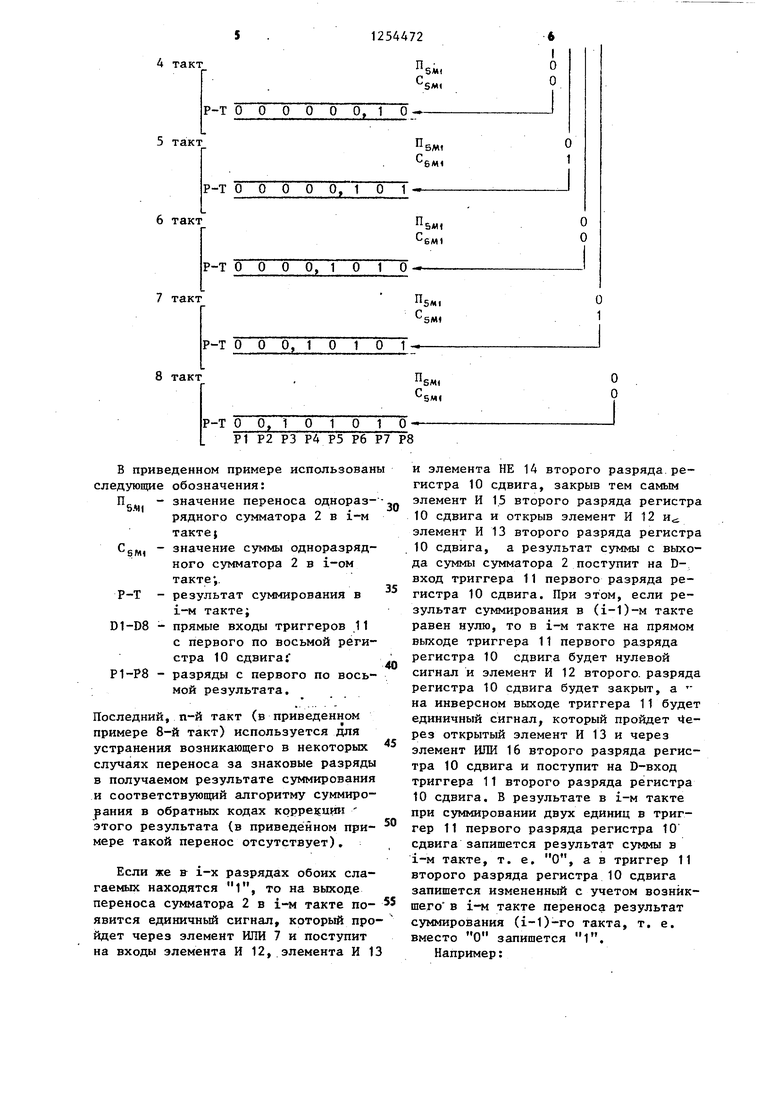

8 такт

Р-Т О О, 1 101 10 Р1 Р2 РЗ Р4 Р5 Р6 Р7 Р8

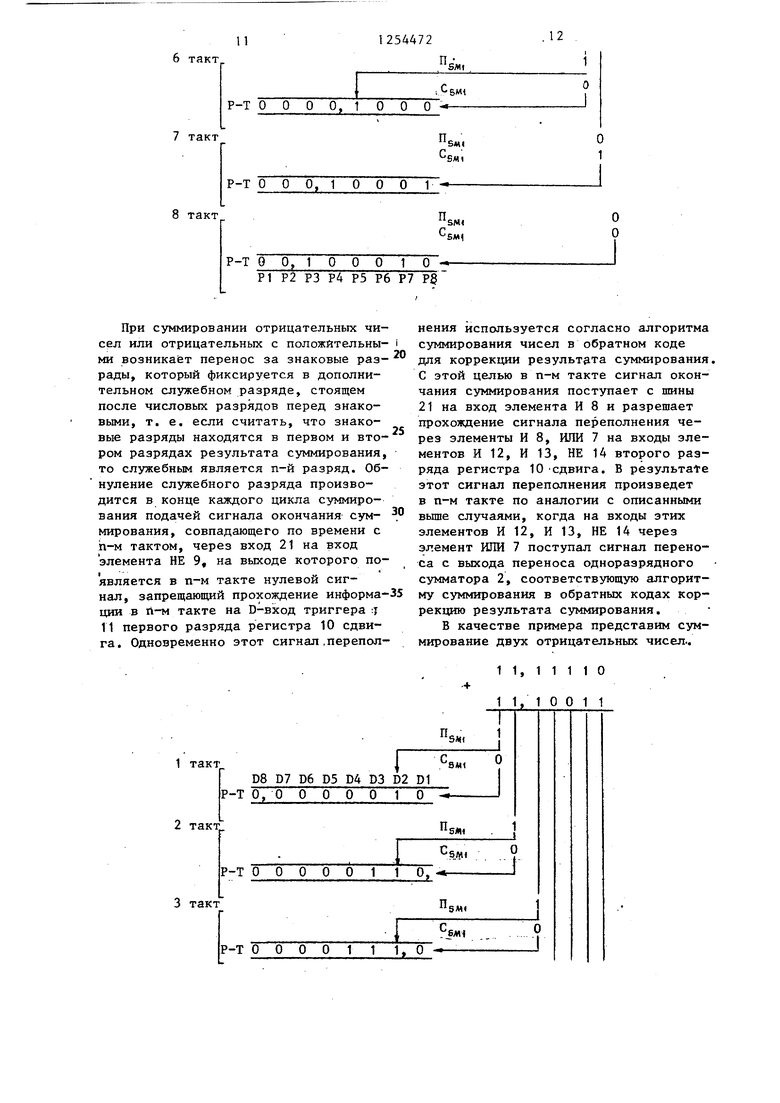

Если же при суммировании в i-м такте в i-x разрядах обоих слагаемых окажутся единиць, и в то же время ре-50 зультат суммирования в (i-l)-M такте равен единице, в (1-2)-м такте равен единице, в (i-3)-M такте равен нулю, т. е. триггеры 11 первого и второго разрядов регистра 10 сдвига будут в 55 единичном состоянии, а триггер 11 третьего регистра 10 сдвига - в нулевом состоянии, то в результате сумми12544728

О О,10101 +

00,00110

О О

рования в i-M такте в триггер 11 первого разряда регистра 10 сдвига запи- ,шется результат суммирования в i-м такте, т. е. О, в триггер 11 второго разряда регистра 10 сдвига также запишется О, так как на выходе переноса сумматора 2 будет единичный сигнал, который пройдет через элемент ИЛИ 7 и закроет элемент И 15 второго разряда регистра 10 сдвига, а на инверсном выходе триггера 11 первого

разряда регистра 10 сдвига до его пе- реклйчения в i-м .такте будет нулевой сигнал, так как результат суммирования в (i-1)-M такте равен единице. Но в то же время единичный сигнал с прямого выхода триггера 11 первого разряда регистра 10 сдвига до его переключения в i-M такте пройдет через элемент И 12 второго разряда регистра 10 сдвига и закроет элемент И 15 третьего разряда регистра 10 сдвига, а так как триггер 11 второго разряда регистра 10 сдвига до его переключения в i-м такте находит(0 гер в i-M такте перейдет в единичное состояние. А так как триггер 11 третьего разряда регистра 10 сдвига до его переключения в i-м такте находился в нулевом состоянии, то элемент И

ся в единичном состоянии (результат 15 12 четвертого разряда регистра 10 суммирования и в (i-2)-M такте был сдвига будет закрыт и распространение равен единице), то в триггер 11 тресигнала переноса далее прекратится, т. е. на выходах элементов НЕ 14 пятого, шестого и т. д. разрядов регистра 10 сдвига.будут единичные сигналы и в триггерах 11 пятого, шестого и т. д. разрядах регистра 10 сдвига просто произойдет перезапись информации из триггера младгаего разряда в триггер старшего разряда как в обыч-- ном сдвигающем регистре.

20

тьего разряда регистра 10 сдвига в i-M такте также запишется нуль. А. единичный сигнал с прямого выхода триггера 11 второго разряда регистра 10 сдвига пройдет через открытый элемент И 12 третьего разряда регистра 10 сдвига и закроет элемент И 15 чет- вертого разряда регистра 10 сдвига, 25 а откроет элемент И 13 четвертого разряда регистра 10 сдвига; а так как триггер 11 третьего разряда регистра

10 сдвига до его переключения в i-м такте находится в нулевом состоянии, то единичный сигнал с инверсного выхода триггера 11 третьего разряда регистра 10 сдвига пройдет через открытый элемент И 13 и элемент ИЛИ 16 четвертого разряда регистра 10 сдвига на D-вход триггера 11 четвертого разряда регистра 10 сдвига и этот триггер в i-M такте перейдет в единичное состояние. А так как триггер 11 третьего разряда регистра 10 сдвига до его переключения в i-м такте находился в нулевом состоянии, то элемент И

12 четвертого разряда регистра 10 сдвига будет закрыт и распространение

12 четвертого разряда регистра 10 сдвига будет закрыт и распространение

сигнала переноса далее прекратится, т. е. на выходах элементов НЕ 14 пятого, шестого и т. д. разрядов регистра 10 сдвига.будут единичные сигналы и в триггерах 11 пятого, шестого и т. д. разрядах регистра 10 сдвига просто произойдет перезапись информации из триггера младгаего разряда в триггер старшего разряда как в обыч-- ном сдвигающем регистре.

Например:

О О, О 1 О 1 О О О, О О 1 1 1

6 такт

Р-Т 0000, 1000

7 такт

Р-Т О О О, 1 О О О 1

8 такт

Р-Т Q О, 1 000 1 О Р1 Р2 РЗ Р4 Р5 Р6 Р7 PS

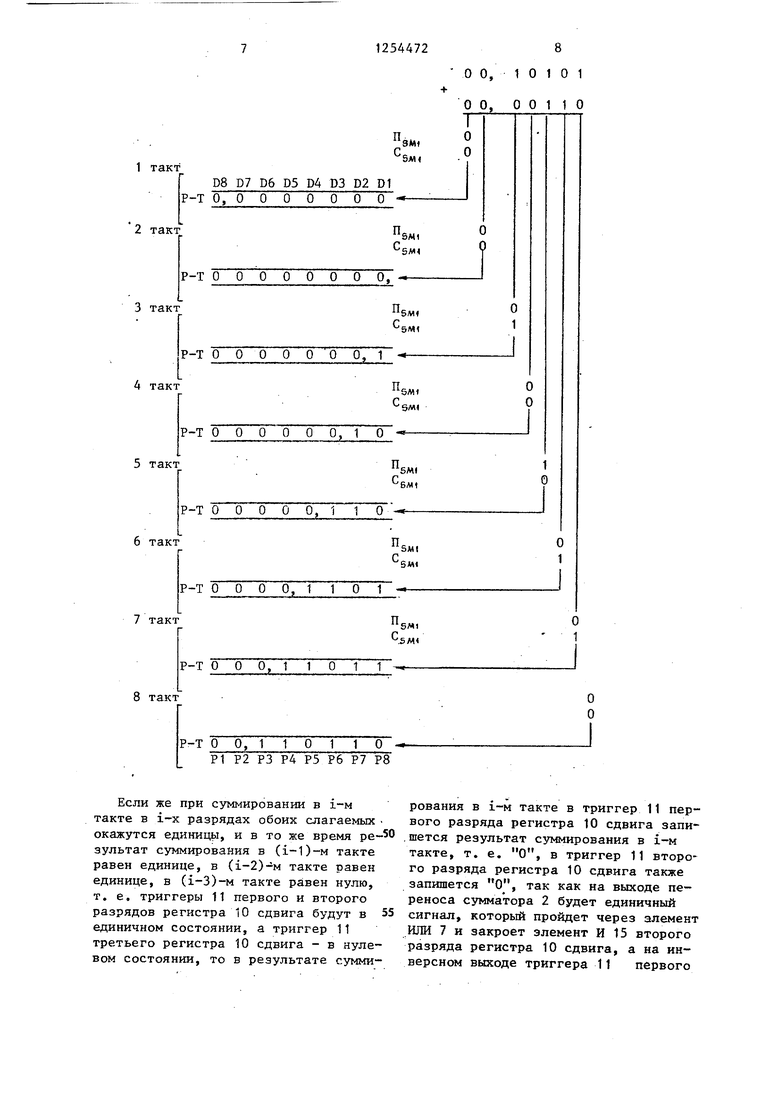

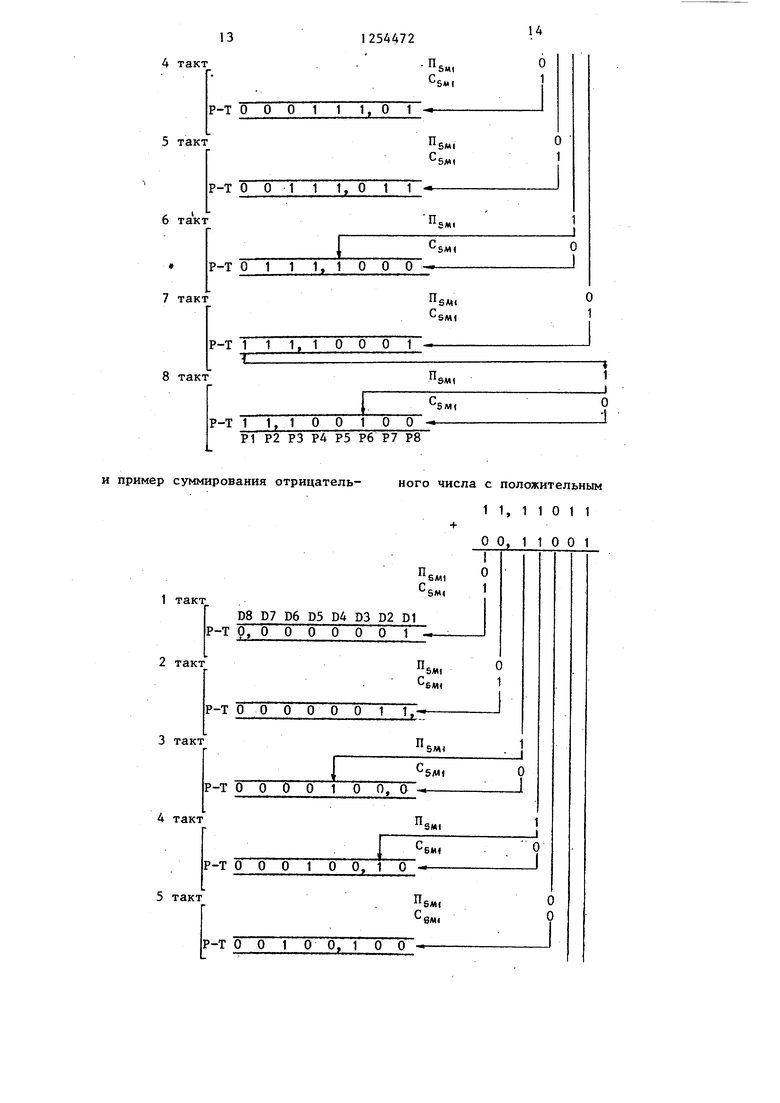

При суммировании отрицательных чисел или отрицательных с положительны- ми возникаЁт перенос за знаковые раз- рады, который фиксируется в дополнительном служебном разряде, стоящем после числовых разрядов перед знаковыми, т. е, если считать, что знако

вые разряды находятся в первом и втором разрядах результата суммирования, то служебным является п-й разряд. Обнуление служебного разряда производится в конце каждого цикла суммирования подачей сигнала окончания суммирования, совпадающего по времени с п-м тактом, через вход 21 на вход элемента НЕ 9, на выходе которого появляется в п-м такте нулевой сигнал, запрещающий прохождение информации в п-м такте на D-вход триггера j 11 первого разряда регистра 10 сдвига. Одновременно этот сигнал .переполJ

В«(

S«i

О

1

О

о

нения используется согласно алгоритма суммирования чисел в обратном коде для коррекции результата суммирования. С этой целью в п-м такте сигнал окончания суммирования поступает с шины 21 на вход элемента И 8 и разрешает прохождение сигнала переполнения через элементы И 8, ИЛИ 7 на входы элементов И 12, И 13, НЕ 14 второго разряда регистра 10 сдвига. В результате этот сигнал переполнения произведет в п-м такте по аналогии с описанными выше случаями, когда на входы этих элементов И 12, И 13, НЕ 14 через элемент ИЛИ 7 поступал сигнал переноса с выхода переноса одноразрядного сумматора 2, соответствующую алгоритму суммирования в обратных кодах коррекцию результата суммирования.

В качестве примера представим суммирование двух отрицательных чисел..

1 1, 1 1 1 1 О +

1 1,1001 1

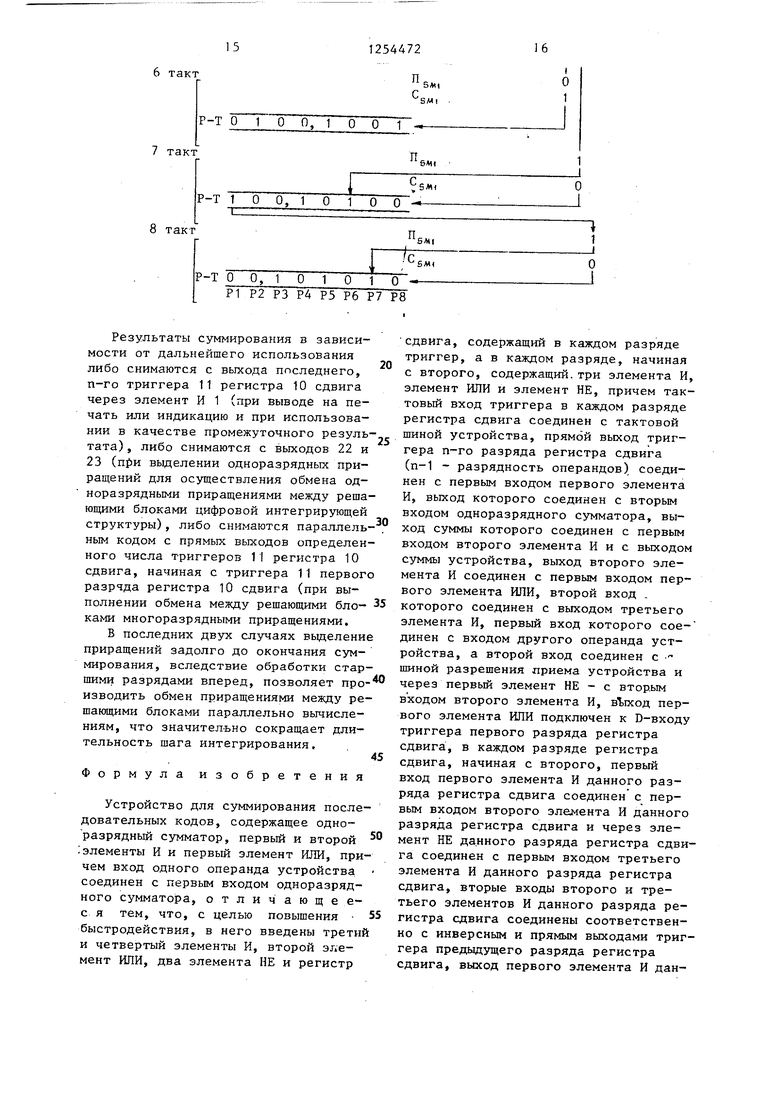

и пример суммирования отрицатель- ного числа с положительным

1 1, 1 1 О t 1

+

О О, 1 1 О О 1

8 такт

Результаты суммирования в зависимости от дальнейшего использования либо снимаются с выхода ппследнего, п-го триггера 11 регистра 10 сдвига через элемент И 1 (при выводе на печать или индикацию и при использовании в качестве промежуточного результата) , либо снимаются с выходов 22 и 23 ( вьщелении одноразрядных приращений для осуществления обмена одноразрядными приращениями между решающими блоками цифровой интегрирующей структуры), либо снимаются параллельным кодом с прямых выходов определенного числа триггеров 11 регистра 10 сдвига, начиная с триггера 11 первого разряда регистра 10 сдвига (при выполнении обмена между решающими бло- ками многоразрядными приращениями.

В последних двух случаях вьщеление приращений задолго до окончания суммирования, вследствие обработки стар

шими разрядами вперед, позволяет производить обмен приращениями между решающими блоками параллельно вычислениям, что значительно сокращает длительность шага интегрирования.

Формула изобретения

Устройство для суммирования последовательных кодов, содержащее одноразрядный сумматор, первый и второй ;элементы И и первый элемент ИЛИ, причем вход одного операнда устройства соединен с первым входом одноразрядного сумматора, отличающе е- с я тем, что, с целью повышения быстродействия, в него введены третий и четвертый элементы И, второй элемент ИЛИ, два элемента НЕ и регистр

0

5

0

5

П

5

5

сдвига, содержащий в каждом разряде триггер, а в каждом разряде, начиная с второго, содержащий.три элемента И, элемент ИЛИ и элемент НЕ, причем тактовый вход триггера в каждом разряде регистра сдвига соединен с тактовой шиной устройства, прямой вьосод триггера п-го разряда регистра сдвига (п-1 - разрядность операндов) соединен с первым входом первого элемента И, выход которого соединен с вторым входом одноразрядного сумматора, выход суммы которого соединен с первым входом второго элемента И и с выходом суммы устройства, выход второго элемента И соединен с первым входом первого элемента ИЛИ, второй вход . которого соединен с выходом третьего элемента И, первый вход которого сое- динен с входом другого операнда устройства, а второй вход соединен с шиной разрешения приема устройства и через первый элемент НЕ - с вторым входом второго элемента И, вЪгход первого элемента ИЛИ подключен к D-входу триггера первого разряда регистра сдвига, в каждом разряде регистра сдвига, начиная с второго, первый вход первого элемента И данного разряда регистра сдвига соединен с первым входом второго элемента И данного разряда регистра сдвига и через элемент НЕ данного разряда регистра сдвига соединен с первым входом третьего элемента И данного разряда регистра сдвига, вторые входы второго и третьего элементов И данного разряда регистра сдвига соединены соответственно с инверсным и прямым выходами триггера предыдущего разряда регистра сдвига, выход первого элемента И дан17

ного регистра сдвига соединен с первым входом первого элемента И следующего разряда регистра сдвига, а второй вход первого элемента И данного разряда регистра сдвига соединен с вторым входом третьего элемента И данного разряда регистра сдвига, выходы второго и третьего элементов И данного разряда регистра сдвига сое447218

вход первого элемента И подключен че- .рез второй элемент НЕ к шине окончания суммирования устройства, первый и второй входы четвертого элемента И соединены соответственно с прямым выходом триггера п-го разряда регистра сдвига и с шиной окончания суммирования устройства, первый и второй входы второго элемента ИЛИ соединены соотдинены с входами элемента ИЛИ данного Ю ветственно с выходом .переноса одно- разряда регистра сдвига, выход которого соединен с D-входом триггера данного разряда регистра сдвига, первый вход первого элемента И второго разряда реги стра сдвига соединен с 15 выходом переноса устройства, второй

17

разрядного сумматора и с вьпсодом чет вертого элемента И, выход второго элемента ИЛИ соединен с первым входом первого элемента И второго разряда регистра сдвига.

ветственно с выходом .переноса одно-

разрядного сумматора и с вьпсодом четвертого элемента И, выход второго элемента ИЛИ соединен с первым входом первого элемента И второго разряда регистра сдвига.

редактор Н.Слободяник

Составитель В.Березкин

Техред Л.Сердюкова Корректор Л.Пилипенко

Заказ 4721/52Тираж 671Подписное

ВНИИПИ Государственного комитета СССР

по делам изобретений и открытий 113035, Москва, Ж-35, Раушская наб., д. 4/5

Производственно-полиграфическое предприятие, г. Ужгород, ул. Проектная, 4

| название | год | авторы | номер документа |

|---|---|---|---|

| Последовательный сумматор | 1983 |

|

SU1149248A1 |

| СПОСОБ И УСТРОЙСТВО СУММИРОВАНИЯ ДВОИЧНО-ДЕСЯТИЧНЫХ КОДОВ | 2008 |

|

RU2395833C2 |

| СПОСОБ И УСТРОЙСТВО УМНОЖЕНИЯ ДВОИЧНО-ДЕСЯТИЧНЫХ КОДОВ | 2009 |

|

RU2410745C1 |

| Параллельный сумматор | 1981 |

|

SU1018114A1 |

| СПОСОБ И УСТРОЙСТВО СУММИРОВАНИЯ И ВЫЧИТАНИЯ ДВОИЧНО-ДЕСЯТИЧНЫХ КОДОВ | 2008 |

|

RU2389064C1 |

| Последовательный сумматор | 1988 |

|

SU1571573A1 |

| СПОСОБ И УСТРОЙСТВО УМНОЖЕНИЯ ДВОИЧНО-ДЕСЯТИЧНЫХ КОДОВ | 2008 |

|

RU2386998C1 |

| НЕЙРОПРОЦЕССОР, УСТРОЙСТВО ДЛЯ ВЫЧИСЛЕНИЯ ФУНКЦИЙ НАСЫЩЕНИЯ, ВЫЧИСЛИТЕЛЬНОЕ УСТРОЙСТВО И СУММАТОР | 1998 |

|

RU2131145C1 |

| Последовательный сумматор кодов с иррациональными основаниями | 1983 |

|

SU1170449A1 |

| УСТРОЙСТВО ДЛЯ УМНОЖЕНИЯ ЧИСЕЛ | 1991 |

|

RU2021633C1 |

Изобретение предназначено для использования в решающих блоках цифровых интегрирующих структур (ЦИС), а также может быть использовано в процессорах цифровых вычислительных машин. В отличие от известных устройств предложенное позволяет произ-, водить обработку, чисел в обратном двоичном коде старшими разрядами вперед, затрачивая на суммирование столько же времени, что при суммировании в дополнительных кодах, в то время чкак при суммировании младшими разрядами вперед время суммирования в обратном коде за счет циклического переноса в 2 раза больше, чем в- допол- .нительном коде. А так как обработка старшими разрядами вперед дает к тому же возможность вьщелять приращения задолго до окончания процесса вычислений и тем самым позволяет организовать обмен информацией параллельно процессу вычислений, то в результате предлагаемый сумматор, оперирующий с обратными кодами, позволяет повысить быстродействие ЦЙС в 2,5 раза при затратах оборудования в 1,3 раза меньших, чем при использовании дополнительного кода. Положительный эф- фект достигается введением четвертого злемента И и второго элемента ИЛИ. 1 ил. g СЛ

| Последовательный сумматор | 1983 |

|

SU1149248A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Соловьев Г.Н | |||

| Арифметические устройства ЭВМ | |||

| М.: Энергия, 1978, с | |||

| Способ приготовления строительного изолирующего материала | 1923 |

|

SU137A1 |

| Кипятильник для воды | 1921 |

|

SU5A1 |

Авторы

Даты

1986-08-30—Публикация

1984-09-29—Подача