i,r(ip;, ).; iirrpnofo сумчатоГ)а no моду.по ,iiia, аы.ход .ервого су-ч1,-.гпора (lo моду.-по лпа. соединен с первым входом перекл:очате., netvebiil выход котор/счч сс1М,иneii с пр)вым входом б.юку упрай,;ечия, гго; л) выход п./реключатели соединен со входом буфе)11ого регистра сдвига. и11;хсд которого соединен со вторым входом переключателя, пторои выход блока yrip;:ri. eirnn соединен с треты-;;, входом переключателя, третий выход которого является выходом

устройств..

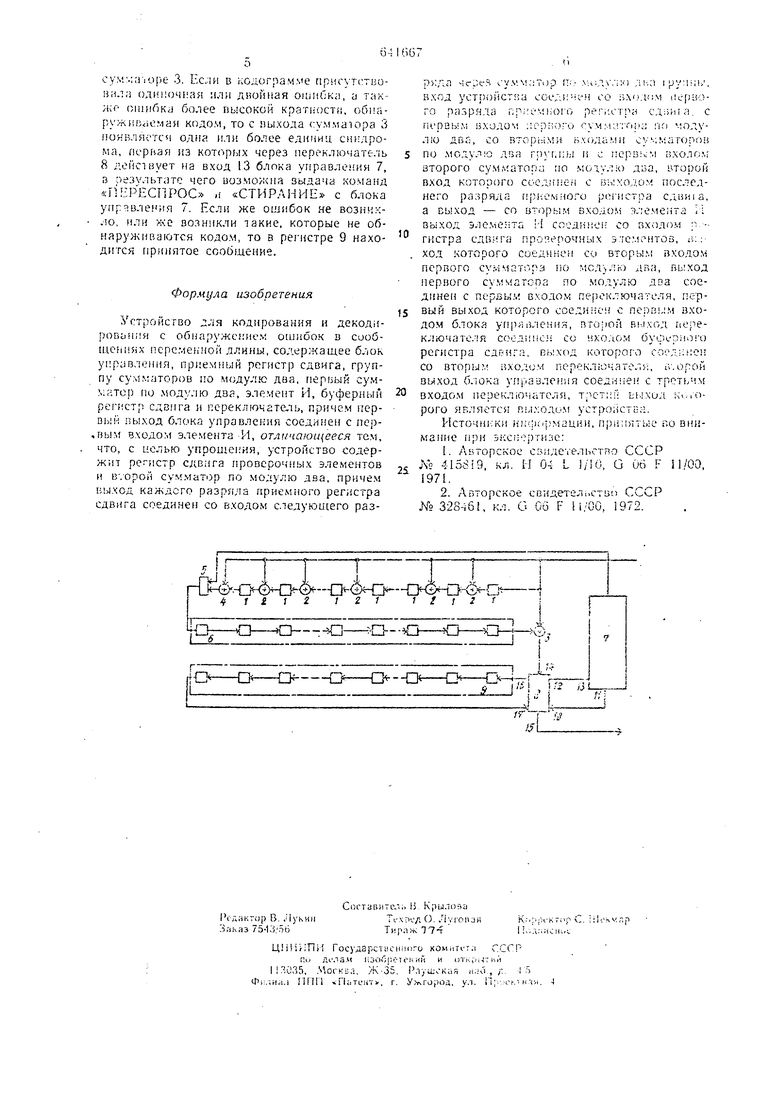

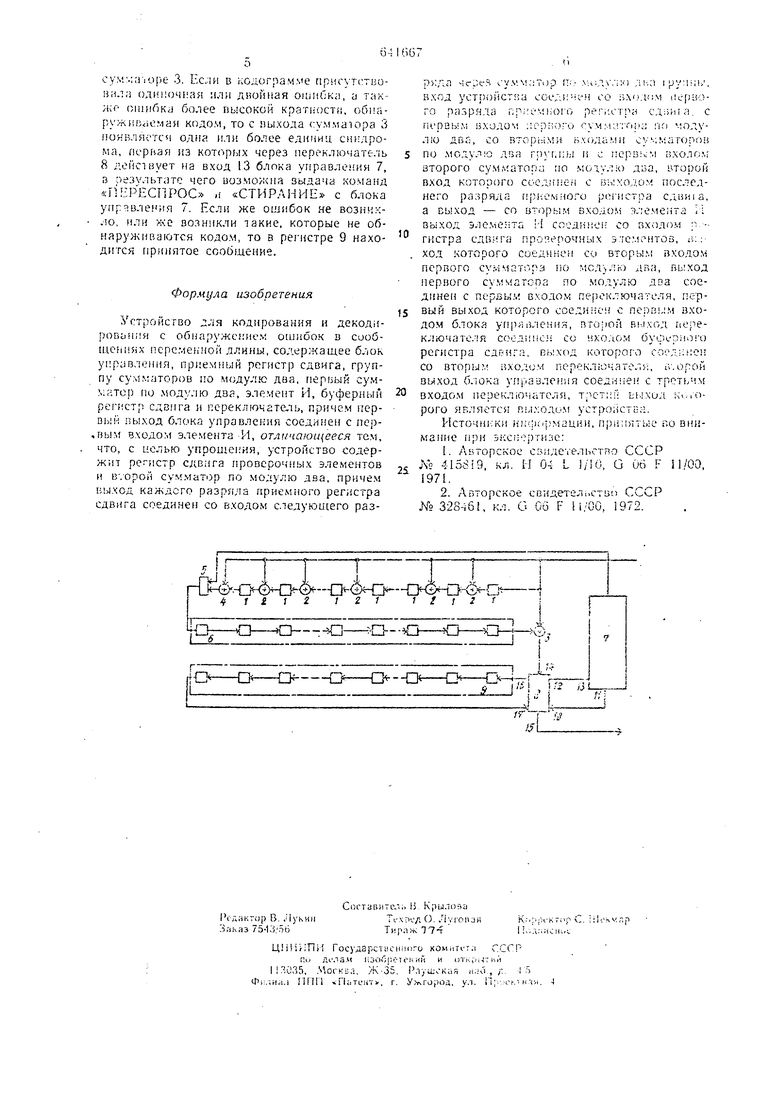

Ма чертеже изображена схема устройства для кодирования н декодирования с с5наружением ошибок в cooGmcHiinx переменной длины.

Устройство содержит 1рием- ыи регистр сдвига с разрядами,обозначенными через 1.

Выход ка 1 до1о из разрядов со входом следуюи1е1о разряда через соотаетсгвующип ему сумматор по модулю два, нодкл1Оченн;,1Й вторым входом ко входу устpOiiCiBa, а также к первым входам первого, сумматора по модулю два 3 и второго сумматора по модулю два 4 и.ко зхолу нервого разряда приемного регистра сдвига, выход носледнего разряда которого через второй сумматор но модулю два 4 и элеме1-т И 5, подключенный к вы.ходу зтого сум.матора, .соединен со входом регистра сдвига fipoверочных элементов 6, выход которого через nepijiiifi сумл;атор по модулю два 3 подключен к г;ереклк1чателю 8, соединенному с буферным регистром 9 и выходом устройства.

fxioK управления 7 обеспечивает нодачу тактовых нмпульсов на все разряды регистров и управляет работой элемента И 5. С выхода блока управления 7 поступает команда «nEF ECnPOC при обнаружении ошибок в принятом сообщении и при необходимости его повторения, а также «СТИРАНГШ для обнуления регистров (на чертеже эти связи блока управления не изображень;). Перекл;очатель 8, состоящий из трех или более элементов И, функционально связан но входу 0 с выходом 11 блока управления 7, а также по выходу 12 со входо.м 3 блока управления. Переключатель 8 ocyuiecTБляет подключение входа 14 в различньгх режимах работы к выхода.м 12. 15, 16, а также подключение входа 17 к выходу 15 в случае необход1.ости закольцоаки регистра 9 для хранения, принятых (переданных) сообщений. Связь i2-13 необходима для. формирования команд с выхоч,; ... управления 7 в случаях обнаружен; ; ошибок.

Порождающая /(. и проверочная; Z матрицы кода обе paa.-iepa 2п п имеют вид:

л

J1 j )..: ; ;Д|;1;.:;: ; v:-:: .:i-c i ,-:.i; .-, n Ilio x

ИНф)рл;:1Л;:0 ;1-; :Х -i.ii/MiПТСЯ Hh } (CJiO/KcHue np-K;;;iu;.:ii ,: ;:o ;n;i.ii() даа) ,::;ет ои ац;:г | : -;i;-;:; ;; .:ip-.:(;;:i;;.::, n вторых n i ;;j;;e:i; 4;i:,;x .ioN;i;:T;::-. - oiiLoi ллиlib 2n. iic.Iil i ;:iiHO..)K л принятой 1-ОМбЧ; ЛЧ;11

нет, lo iii;0; 3i ex( Z п.. Be)-.Ti;ii-cio.G::u 2г; этой ко 5:1н;:1;:;и TO.-i;:;ecT::0;:;;;paiuio ;iy.iK). Пели ;f;o n ip;i;:H;o: Kiv;orpaNiNe о.,. Дпор; ;; 1ли Givirv высокой xpaTiiOCTi; oiiiiiiM;:;, (б iapvж iBflO :aи кодом, то это прс.иЗК.аЧНе не )авно улю, и при 1 р-овер1:а:: ii,-;i чсу.юст, Е со.г.тг.етстстии с алгорнт-,ом декод.;ро;5а ;;:, задптщым матрицей Z, с выхода cv i :rrop;i появляются единицы .1ма, то я;5.1яется признаком (к в c jo6me H H. .Ллгоригмь: кодирования и декод;|;иязампя, заданн;, MaipiiiiaMH /i ii Z, леж;;7 n c.cjore построен ;; устройства и ..il:i: erij .

в pe/KiiMc код: Г о 5ани;, перед которьл все разрядь) i L-i CTpua находятся в .м состоянии, на вход ycTpoiicTiUi по iiepвым п TaKTaN;, i тече:;ие которых огкрыг элемент И 5, а вход i 4 нере1члючателя S подкл:очен к Е;ь хо;;у ), .чгследоьательно поступают п инсрормлциопных элеме.чтоа (комбина:л:;я .neii н един;1ц), ко орые через cy.-iNiaTop 3 и аерскл;о-:: тел/. 8 .Л.-;ются на выходе устройства ()1но они могут б.ыть записан :. в регистре 9 для повторен 1я). По этим же 1:ерп;..:ч н в реп .стр G пост}иают пос едо-дягсльно п проверочных 3.., (ор..и-пемых в )азрядах репстра и на су:.:.:аторлх 2 в соотзетстви;: с алгоритмом .. 1 течен :е р,то;,)Ь.х п тактов эле. П 5 .зпкрьт и разряд : 1 регистра устпнапли; а;отс; в ;улевое состо:.:п;;е. Псрек.-.ючатель 3 продолжает осу -цес1плять юдк.:(5чен; г iixo; a 14 к ВЫХОД) 16, и. ес.чи это ; Сччххо... вход 17 к выходу i5. На пь:х(;е устро;:сгнг и(;являются последо5ате.;ько :i ;рппор чнь:Х э.;ементов вслед за информац ан;;:.. По OKOi чании п Бтоги,1х .зктоь )c:T,iiiCTBO готово к очеред|0-.у ипкту кодириьання.

В режиме деколирован л repBi e п T.IKTOB огкрыт элем1л:т к; 5 и вход 1- п реключатоля 8 подключен к вы.чоду 15 (коз .;о;;;на закол1 аовка 17--i5). Поступающие ;;а вход п ипd)opMa U OHrib;x )гroв последова геЛ)1О записываются в регистр 9 через о, на втооой вход KOTOpoio подается . ОдHOBpos e i;iO по кн.; 10рмир ;отся п гичовероччых э:1емснтов как i в коднроваП 1Я. В TCHCiiiie пос.еду1О 11их п тактов элеyiii i 5 , вход 14 пе;1екл;лчате.:я S от: лючон от Г1:..;.ода 13 и coi.,rin;e i с зыходо.1 12, пход 17 оолпнен с ib:xc..:oN 15 (регистр 9 Cvu;; ; ;;::с) . (.ф.,рм:1:н)iia ;Hbk npi.4ie;)C4;;..ii э.чсг-ЧНТг; з к;;:-л.;о%5 T;I-:те, -.чи:1ЛЯ с п I-;.) н KJ isiiu ,; -... cpaвн iFi;;:oтcя с ci.глете; ,;;:;;ми ;:s цр, iii;маем 1.1 лi п|.:нс:м-;H.:.:I; s.ic.;c:i ;.) сум:.:а1О)е 3. EC:IH в iiOjiorpaMse присутствовал; с)ли1:оч1 ая млн ,июниая ошибк;), и такл;г- ошибка более пысокон KpariiocTfi, обпару кив 5емая кодом, то с выхода сумматора 3 понвляотсч одна или более единиц синдрома, первая из которых через переключатель 8 лейстнует на вход 13 блока уггравления 7, в результате чего иозможиа выдача команд «П.-РЕСПРОС ,( «СТИРАНИЕ с блока управления 7. Если же ошибок яе возникло, или Хлс возникли такие, которые не обнаруживаются кодом, то в регистре 9 находится принятое сообщение. Формула изобретения Устройство для кодирования н декодирования с обнаружением ошибок в сообщениях перемеьной длины, содержащее блок управления, приемный регистр сдвига, группу сумматоров по модулю два, пер(зый сум,;атср по модулю два, элемент И, буферный регистр сдвига и переключ2те.ть, причем перBhifi пыход блока управления соединен с пер,вым входом элемента И, отлишющееся тем, что, с целью упроше1 ия, устройство содержит регистр сдвига проверочных элементов и в .орой суммат13р по модулю два, причем выход каждого разряда приемного регистра сдвига соединен со входом следующего разР ;ДчП )p .u:,.:.() ;ii-.;i ipyniiu, вход устг))а сосди-к н со Г)|) iiepiioго разряда приемного регг;стра , с П1рвы : входом licpiioro сумматору; nrj .юдулю дай, со BTOpbi.sni входами су-;.;атопов по модулю г)угл:ы и с nepnixM вхолг;, второго сумг.;атора по моаул о Д15а, второй вход которого cocAHiieii с вь;ходом последнего разряда nfiiiCNiHoro регистра сдви1а, а выход - со вторым входо. элемента М выход элемента i-i соодияс ; со входом р гистра сдвига проверочных злемонтов, а;: ход которого соединен со вторым входом первого сумматора по iiBa, вь;ход первого сумматопа по модулю два соеД1 неп с первым входом переключателя, первый выход которого соеди -:ен с перпым входом блока упрявленил, второй В1-.1ход iiepeк- ючате. сосдипс.. со входом буос-р.чо.Ч) регистра сдрнга, вь:ход которого соел;:нен со вторы., входо.м переключателя, а .орой зыход блока управления соедипе с третьим входом переключателя, трет:;й ы.хид KV;,Oрого является п,1ходо.1 устройства. Источн1;ки И)11;1о;;мац1:и, nf).e г.о внимание при 5г;сг ртизе: 1.Авторское свидетельство СССР № 4158Э. кл. Н 04 L J/10, О 06 F 1971. 2.Авторское свидетел1,ств) СССР № 328461, кл. G Об F И/ОО, 1972.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для декодирования с коррекцией ошибок | 1985 |

|

SU1292189A1 |

| Декодер укороченного кода Хэмминга | 1983 |

|

SU1109924A1 |

| Устройство для исправления пакетных ошибок модульными кодами | 1988 |

|

SU1596465A1 |

| Декодер циклического кода с исправлением ошибок и стираний | 1980 |

|

SU1083387A1 |

| Устройство для исправления ошибок | 1984 |

|

SU1287296A1 |

| Мажоритарное декодирующее устройство | 1975 |

|

SU538502A1 |

| Устройство кодирования блоков информации | 1984 |

|

SU1302439A1 |

| Сверточный кодек с алгоритмом порогового декодирования | 1985 |

|

SU1327296A1 |

| Запоминающее устройство с автономным контролем | 1991 |

|

SU1837363A1 |

| Пороговый декодер сверточного кода | 1986 |

|

SU1443180A1 |

и|х.-{(4-- ь4-{ --ЧзА-0-ё С

Авторы

Даты

1979-01-05—Публикация

1974-02-12—Подача