Изобретение относится к электросвязи и может использоваться в системах цифрового радиовещания и цифрового телевизионного вещания при использовании высокоскоростных сверточных кодов и порогового декодирования.

- Цель изобретения - повьшение помехоустойчивости.

, i К(з + 1, коды скорости переда чи кода и корректирующей способности кода . Длина кодового ог ран.ичения составляет п(т+1).По сим

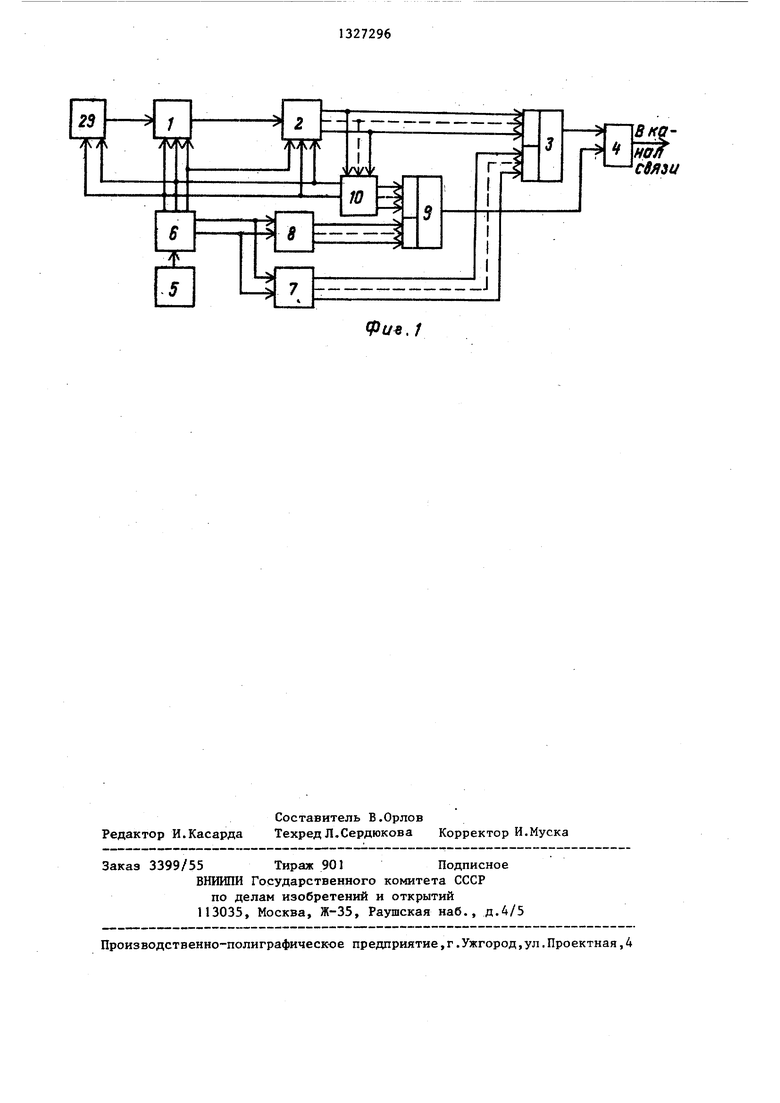

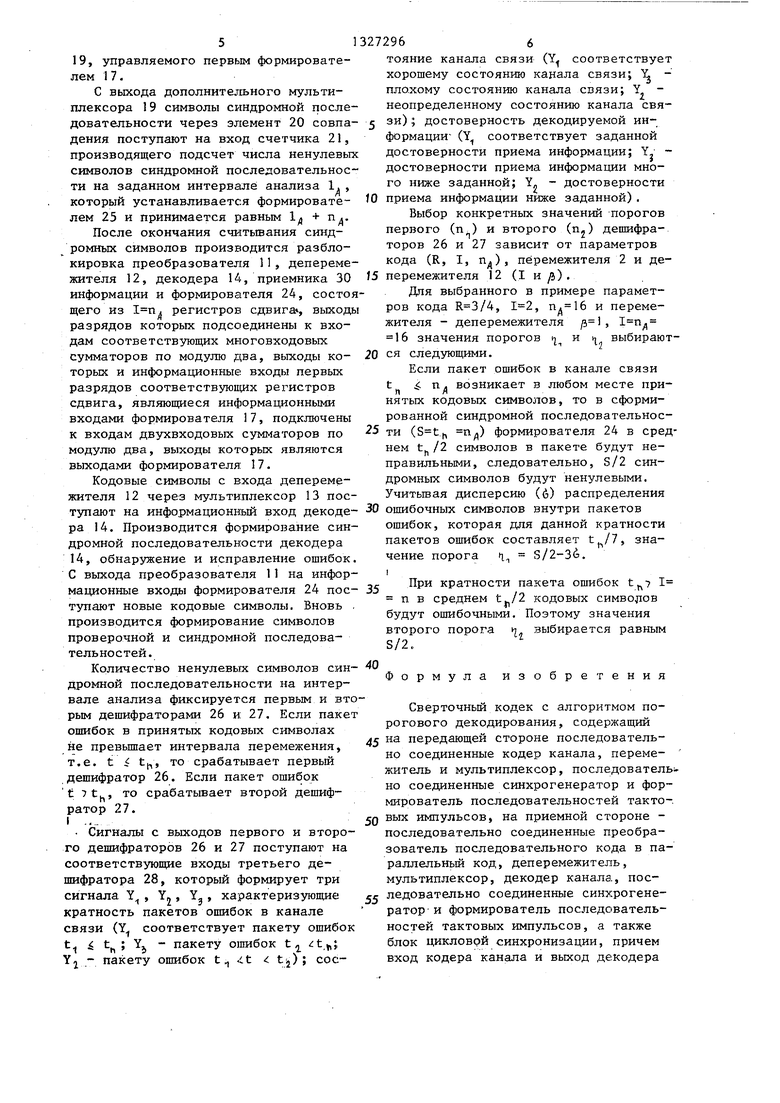

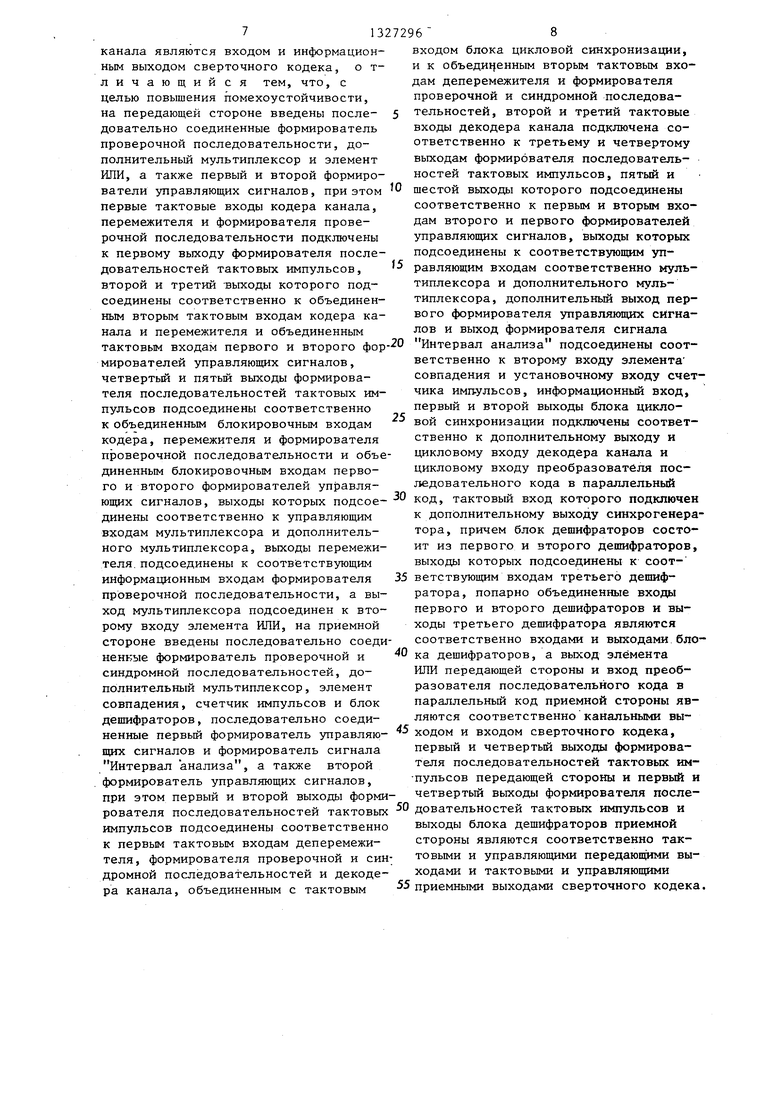

На фиг.1 и 2 представлены структур-iо волов, где m - наивысшая степень поные электрические схемы сверточного кодека с алгоритмом порогового декодирования .

Сверточный кодек с алгоритмом порогового декодирования содержит на пе- редающей стороне кодер 1 канала, пе- ремежитель 2, мультиплексор 3, элемент ИЛИ 4, синхрогенератор 5, формирователь 6 последовательностей тактовых импульсов, первый и второй формирователи 7 и 8 управляющих сиг

налов, дополнительный мультиплексор 9 и формирователь IО проверочной последовательности, на приемной стороне - преобразователь 11 последова- ;, тельного кода в параллельный код, деперемежитель 12, мультиплексор 13, декодер 14 канала, синхрогенератора 15, формирователь 16 последовательностей тактовых импульсов, первый и второй формирователи 17 и 18 управляющих сигналов, дополнительный мультиплексор 19, элемент 20 совпадения, счетчик 21 импульсов, блок 22 дешиф20 Символы первой ветви перемежителя 2 передаются без задержки. Кодовые символы остальных (I-I) параллельных вет вей передаются с задержкой соответственно ft, 2|i,. .. . (1-1)/3 тактов. В

25 результате перемежения каждые два входных символа на выходе перемежителя 2 отстоят друг от друга на п символов. Следовательно, плотный пакет ошибок кратностью t , п . после депеП л

30 ремежения распределяется в одиночные ошибки на длине каждой п.

Кодовые символы с выхода перемежителя 2 в параллельном коде поступают на информационные входы мультираторов, блок 23 цикловой синхрониза- ъ плексора 3 и формирователя 0„ Кодо- ции, формирователь 24 проверочной и синдромной последовательностей, формирователь 25 сигнала Интервал анализа.

Блок 22 дещифраторов содержит пер- 40 ьпс Пд разрядных регистров сдвига и вый, второй и третий дешифраторы 26вые символы с выхода мультиплексора 3 через элемент ИЛИ 4 поступают в каналы связи. Одновременно в формирователь 10, состоящий из I параллель28.

На фиг.1 и 2 также изображены источник 29 информации и приемник 30 информации, которые являются самостоятельными устройствами.

Сверточный кодек с алгоритмом порогового декодирования работает следующим образом.

Информация от источника 29 информации в последовательном коде поступает на вход кодера 1, в котором в соответствии с выбраннЁ ми порождающими полиномами q(D) , q-(D) (1+D), qj(D) I+D , где D - информационные символы, производится кодирование информации самоортогональным сверточным кодом с алгоритмом порогового декодирования. В процессе

I сумматоров по модулю два, входы .которых подключены к выходам разрядов соответствующих п -разрядных регистров сдвига, записывается N

45 I/5 кодовых символов, из которых формируется Пд символов проверочной последовательности.

В первый регистр сдвига формирователя 10 записываются первые симвоCQ лы всех кодовых ограничений Пд. Во второй регистр сдвига формирователя IО записываются вторые символы всех кодовых ограничений п и т.д. При этом первый W символ проверочной подс следовательности представляет собой сумму по модулю два первых символов всех I кодовых ограничений Пд. Второй W- символ проверочной последовательности представляет собой сумму

кодирования из информационных символов формируются проверочные символы J i.v (),. (/7.

Т (D)

Ко

и

in

(D) X ), j l,2,3;

, i К(з + 1, коды скорости передачи кода и корректирующей способности кода . Длина кодового ог- ран.ичения составляет п(т+1).По символов, где m - наивысшая степень порождающих полиномов, п - проверочный символ. На данной длине кодового ограничения п код гарантированно исправляет одиночные и двойные ошибки. Сформированные кодовые символы с выхода кодера 1 поступают на вход пе- ремежителя 2, в котором производится распределение кодовой последовательности на параллельных ветвей.

Символы первой ветви перемежителя 2 передаются без задержки. Кодовые символы остальных (I-I) параллельных ветвей передаются с задержкой соответственно ft, 2|i,. .. . (1-1)/3 тактов. В

результате перемежения каждые два входных символа на выходе перемежителя 2 отстоят друг от друга на п символов. Следовательно, плотный пакет ошибок кратностью t , п . после депеП л

ремежения распределяется в одиночные ошибки на длине каждой п.

Кодовые символы с выхода перемеителя 2 в параллельном коде поступают на информационные входы мультиплексора 3 и формирователя 0„ Кодо-

вые символы с выхода мультиплексора 3 через элемент ИЛИ 4 поступают в каналы связи. Одновременно в формирователь 10, состоящий из I параллель ьпс Пд разрядных регистров сдвига и

I сумматоров по модулю два, входы .которых подключены к выходам разрядов соответствующих п -разрядных регистров сдвига, записывается N

I/5 кодовых символов, из которых формируется Пд символов проверочной последовательности.

В первый регистр сдвига формирователя 10 записываются первые символы всех кодовых ограничений Пд. Во второй регистр сдвига формирователя IО записываются вторые символы всех кодовых ограничений п и т.д. При этом первый W символ проверочной последовательности представляет собой сумму по модулю два первых символов всех I кодовых ограничений Пд. Второй W- символ проверочной последовательности представляет собой сумму

по модулю два вторых символов всех I кодовых ограничений п и т.д. Пос- .ледний w символ проверочной последовательности представляет собой сумму по модулю два последних символов всех 9 кодовых ограничений.

Сформированные через t| тактов символы последовательности в параллельном коде поступают -на информационные входы дополнительного мультиплексора 9. Производится считьшание символов проверочной последовательности в канал связи. На время считывания производится блокировка по соответствующим тактовым входам источника 29 информации, а также кодера 1, перемежителя 2, формирователя 10 и первого формирователя 7, в результате чего передача, кодирование и переме- жение новой информации не производятся,

После передачи в канал связи поспооанительного

мультиплексора 9 осу10

ществляется блоком 23 цикловой синхронизации.

Далее приводится работа сверточ- ного кодека с алгоритмом порогового декодирования после установления цикловой синхронизации преобразователя 1 1 .

С выходов деперемежителя 12 кодовые символы через мультиплексор 13 поступают на вход декодера 14. Производится формирование синдрома, обнаружение и исправление ошибок в

15 пределах корректирующей способности кода и передача информации в приемник 30 информации.

Если в канале связи пакеты ошибок не превьшают кратности t| п . и за20 щитный промежуток между пакетами равен 1а N-t

h

ТО после деперемежения

леднего w

tn

символа проверочной поена вход декодера 14 будут поступать кодовые комбинации из Пд символов, содержащие по одной ошибке, т.е. не преледовательности производятся разблоки-25 вьпяающие корректирующей способности

ровка источника 29 информации, кодера выбранного кода.

1, перемежителя 2, формирователя 10, Б формирователе 24 из принятых кодовых символов, по алгоритму, как и на передающей стороне в кодере 1, форпёрвого формирователя 7 и блокировка второго формирователя 8. Далее процесс кодирования, перемежения, форми- ЗО мируются символы дополнительной проверочной последовательности w,, wj

рования символов проверочной последовательности и считывание информации в канал связи осуществляется аналогичным образом. В результате информация в канал связи передается

г

W,

W

f,

35

В это время первый формирователь 17 заблокирован соответствующим сигналом с формирователя 16. После t.

п

+ w кодовых символов:

блоками из Пд R - информационных символов и n(l-R)+w - проверочных символов (с учетом избыточности кода и символов дополнительной проверочной последовательности) .

На приемной стороне кодовая последовательность пост упает на информационный вход преобразователя 11, в котором производится преобразование кодовой последовательности из последовательного кода в параллельный код, т.е. входная кодовая последовательность распределяется на I п. 16 параллельных подпотоков. С выхода преобразователя 11 символы информационных подпотоков одновременно поступают на входы соответствующих регистров сдвига деперемежителя 12 и фо1 мирователя 24.

Согласование по фазе выходных информационных подпотоков преобразователя 11 с входными информационными подпотоками мультиплексора 3 и до1327296

пооанительного

мультиплексора 9 осу

ществляется блоком 23 цикловой синхронизации.

Далее приводится работа сверточ- ного кодека с алгоритмом порогового декодирования после установления цикловой синхронизации преобразователя 1 1 .

С выходов деперемежителя 12 кодовые символы через мультиплексор 13 поступают на вход декодера 14. Производится формирование синдрома, обнаружение и исправление ошибок в

пределах корректирующей способности кода и передача информации в приемник 30 информации.

Если в канале связи пакеты ошибок не превьшают кратности t| п . и защитный промежуток между пакетами равен 1а N-t

h

ТО после деперемежения

на вход декодера 14 будут поступать кодовые комбинации из Пд символов, со держащие по одной ошибке, т.е. не пре

роj

г

W,

W

f,

5

В это время первый формирователь 17 заблокирован соответствующим сигналом с формирователя 16. После t.

тактов записи информации в регистры сдвига деперемежителя 12 и формирователя 24 производится блокировка сигналом с формирователя 16 депереме0 жителя 12 второго формирователя 18, декодера 14 приемника 30 информации. Через tp +1 тактов осуществляется блокировка преобразователя 11 и первого формирователя 17. Производится

5 формирование символов синдромной последовательности (w @w), (w © V7 ),......, (w|. ® w I ) путем

суммирования по модулю два символов проверочной последовательности, сфорQ мированной из принятых кодовых символов проверочной последовательности, и считывание символов синдромной последовательности. За время считывания синдромных символов поступление новой

е кодовой информации не производится.

Считывание символов синдромной последовательности производится с помощью дополнительного мультиплексора

19, управляемого первым формирователем 17.

С выхода дополнительного мультиплексора 19 символы синдромной последовательности через элемент 20 совпадения поступают на вход счетчика 21, производящего подсчет числа ненулевых символов синдромной последовательности на заданном интервале анализа 1., который устанавливается формирователем 25 и принимается равным 1 + п. После окончания считьшания синд- ромных символов производится разблокировка преобразователя 11, депереме- жителя 12, декодера 14, приемника 30 информации и формирователя 24, состоя щего из , регистров сдвига, выходы разрядов которых подсоединены к входам соответствующих многовходовых сумматоров по модулю два, выходы которых и информационные входы первых разрядов соответствующих регистров сдвига, являющиеся информационными входами формирователя 17, подключены к входам двухвходовых сумматоров по модулю два, выходы которых являются выходами формирователя 17.

Кодовые символы с входа депереме- жителя 12 через мультиплексор 13 поступают на информационный вход декодера 14. Производится формирование синдромной последовательности декодера 14, обнаружение и исправление ошибок. С вькода преобразователя 11 на информационные входы формирователя 24 поступают новые кодовые символы. Вновь , производится формирование символов проверочной и синдромной последовательностей.

Количество ненулевых символов син- Дромной последовательности на интервале анализа фиксируется первым и вторым дешифраторами 26 и 27. Если пакет ошибок в принятых кодовых символах не превьшает интервала перемежения, т.е. t t|,, то срабатывает первый дешифратор 26. Если пакет ошибок t 7t. , то срабатьюает второй дешифратор 27.

I

Сигналы с выходов первого и второго дешифраторов 26 и 27 поступают на соответствующие входы третьего дешифратора 28, который формирует три сигнала Y, Y, Y,, характеризующие кратность пакетов ошибок в канале связи (Y соответствует пакету ошибок t Ц ; YJ - пакету ошибок t ,t Yj - пакету ошибок t ct ; tj) ; coc2966

тояние канала связи (Y соответствует хорошему состоянию канала связи; Y - плохому состоянию канала связи; Y - неопределенному состоянию канала связи); достоверность декодируемой информации- (Y соответствует заданной достоверности приема информации; Y, - достоверности приема информации много ниже заданной; Y. - достоверности

приема информации ниже заданной).

Выбор конкретных значений порогов первого (п.) и второго (п) дешифраторов 26 и 27 зависит от параметров кода (R, I, Пд), пёремежителя 2 и депёремежителя 12 (I и ).

Для выбранного в примере параметров кода , , п,16 и переме- жит(У1я - деперемежителя /3 16 значения порогов ij и выбираются следующими.

Если пакет ошибок в канале связи t д возникает в любом месте принятых кодовых символов, то в сформированной синдромной последовательности ( ) формирователя 24 в среднем tj, /2 символов в пакете будут неправильными, следовательно, S/2 син- дромных символов будут ненулевыми. Учитьшая дисперсию (6) распределения

ошибочных символов внутри пакетов ошибок, которая для данной кратности пакетов ошибок составляет значение порога ч S/2-Зб. I

При кратности пакета ошибок 1 п в среднем кодовых симво юв будут ошибочными. Поэтому значения второго порога i| выбирается равным

S/2.

40

Формула изобретения

Сверточный кодек с алгоритмом порогового декодирования, содержащий

45 на передающей стороне последовательно соединенные кодер канала, переме- житель и мультиплексор, последовательно соединенные синхрогенератор и формирователь последовательностей такто50 вых импульсов, на приемной стороне - последовательно соединенные преобразователь последовательного кода в па- раллельньш код, деперемежитель, мультиплексор, декодер канала, пос55 ледовательно соединенные синхрогенератор и формирователь последовательностей тактовых импульсов, а также блок цикловой синхронизации, причем вход кодера канала и выход декодера

71327296 8

канала являются входом и информацион- входом блока цикловой синхронизации, ным выходом сверточного кодека, от- и к объединенным вторым тактовым вхо- личающийся тем, что, с дам деперемежителя и формирователя целью повышения помехоустойчивости, проверочной и синдромной последова- на передающей стороне введены после- 5 тельностей, второй и третий тактовые довательно соединенные формирователь входы декодера канала подключена со- проверочной последовательности, до- ответственно к третьему и четвертому полнительный мультиплексор и элемент выходам формирователя последователь- ИЛИ, а также первый и второй формиро- ностей тактовых импульсов, пятый и ватели управляющих сигналов, при этом шестой выходы которого подсоединены первые тактовые входы кодера канала, соответственно к первым и вторым вхо- перемежителя и формирователя прове- дам второго и первого формирователей рочной последовательности подключены управляющих сигналов, выходы которых к первому выходу формирователя после- подсоединены к соответствующим уп- довательностей тактовых импульсов, равляющим входам соответственно муль- второй и третий выходы которого под- типлексора и дополнительного муль- соединены соответственно к объединен- типлексора, дополнительный выход пер- ным вторым тактовым входам кодера ка- во го формирователя управляющих сигна- нала и перемежителя и объединенным лов и выход формирователя сигнала тактовым входам первого и второго Интервал анализа подсоединены соот- мирователей управляющих сигналов, ветственно к второму входу элемента четвертьй и пятьй выходы формирова- совпадения и установочному входу счет- теля последовательностей тактовых им- чика импульсов, информационный вход, пульсов подсоединены соответственно первый и второй выходы блока цикло- к объединенным блокировочным входам вой синхронизации подключены соответ- кодера, перемежителя и формирователя ственно к дополнительному выходу и проверочной последовательности и объе- цикловому входу декодера канала и диненным блокировочным входам перво- цикловому входу преобразователя пос- го и второго формирователей управля- ледовательного кода в параллельный ющих сигналов, выходы которых подсое- код, тактовый вход которого подключен динены соответственно к управляющим к дополнительному выходу синхрогенера- входам мультиплексора и дополнитель- тора, причем блок дешифраторов состо- ного мультиплексора, выходы перемежи- ит из первого и второго дешифраторов, теля, подсоединены к соответствующим выходы которых подсоединены к соот- информационным входам формирователя 35 ветствующим входам третьего дешиф- проверочной последовательности, а вы- ратора, попарно объединенные входы ход мультиплексора подсоединен к вто- первого и второго дешифраторов и вы- рому входу элемента ИЛИ, на приемной ходы третьего дешифратора являются стороне введены последовательно соеди- соответственно входами и выходами бло- ненкые формирователь проверочной и ка дешифраторов, а выход элемента синдромной последовательностей, до- ИЛИ передающей стороны и вход преоб- полнительный мультиплексор, элемент разователя последовательного кода в совпадения, счетчик импульсов и блок параллельный код приемной стороны яв- дешифраторов, последовательно соеди- ляются соответственно канальными вы- ненные первый формирователь управляю- ходом и входом сверточного кодека, щих сигналов и формирователь сигнала первый и четвертый выходы формирова- Интервал анализа, а также второй теля последовательностей тактовых нм- формирователь управляющих сигналов, -пульсов передающей стороны и первый и при этом первый и второй выходы форми- четвертый выходы формирователя после- рователя последовательностей тактовых ° довательностей тактовых импульсов и импульсов подсоединены соответственно выходы блока дешифраторов приемной к первым тактовым входам деперемежи- стороны являются соответственно так- теля, формирователя проверочной и син- товыми и управляющими передающими вы- дромной последовательностей и декоде- ходами и тактовыми и управляющими ра канала, объединенным с тактовым 55 приемными выходами сверточного кодека.

Фи,1

| название | год | авторы | номер документа |

|---|---|---|---|

| Пороговый декодер сверточного кода | 1982 |

|

SU1078654A1 |

| Пороговый декодер сверточного кода | 1984 |

|

SU1185629A1 |

| Устройство для устранения неопределенности дискретнофазовой модуляции | 1983 |

|

SU1095428A1 |

| Декодер сверточного кода (его варианты) | 1985 |

|

SU1320875A1 |

| Устройство цикловой синхронизации | 1984 |

|

SU1197122A1 |

| Декодер сверточного кода | 1986 |

|

SU1388998A1 |

| Пороговый декодер сверточного кода | 1986 |

|

SU1443180A1 |

| УСТРОЙСТВО АДАПТИВНОГО ПЕРЕМЕЖЕНИЯ СВЕРТОЧНОГО КОДЕКА | 2006 |

|

RU2340087C2 |

| Кодек несистематического сверточного кода | 1990 |

|

SU1714812A1 |

| Декодер сверточного кода | 1985 |

|

SU1320904A1 |

Изобретение может быть использовано в системах цифрового радиовещания и ТВ вещания при использовании высокоскоростных сверточных кодов и порогового декодирования. Цель изобретения - повышение помехоустойчивости. Считывание символов синдром- ной последовательности (ССП) производится с помощью мультиплексора 19, управляемого формирователем 17 управляющих сигналов. За время считьшания ССП нового поступления кодовой информации не производится. После окончания считывания ССП производится разблокировка преобразователя 11 последовательного кода в параллельный код, деперемежителя 12, декодера 14, . приемника 30 информации и формирователя 24 проверочной и синдромной последовательностей. Кодовые символы с входа деперемежителя 12 через мультиплексор 13 поступают на информационный вход декодера 14. Производится формирование ССП декодера 14, обна- ружение и исправление опмбок. С выхода преобразователя 11 на информационные входы формирователя 24 поступают новые кодовые импульсы. Вновь производится формирование символов проверочной и синдромной последовательностей, 2 ил. § (Л со о

| Патент США № 3988767, кл | |||

| Очаг для массовой варки пищи, выпечки хлеба и кипячения воды | 1921 |

|

SU4A1 |

| The Bell System Technical Journal, т.61, № 8, с.1912, рис.1, 1982. | |||

Авторы

Даты

1987-07-30—Публикация

1985-06-11—Подача