Ф Л.

Изобретение относится к технике связи и может использоваться в устройствах помехоустойчивого кодирования при передаче двоичной информации.

Цель изобретения - повышение помехоустойчивости порогового декодера сверточного кода.

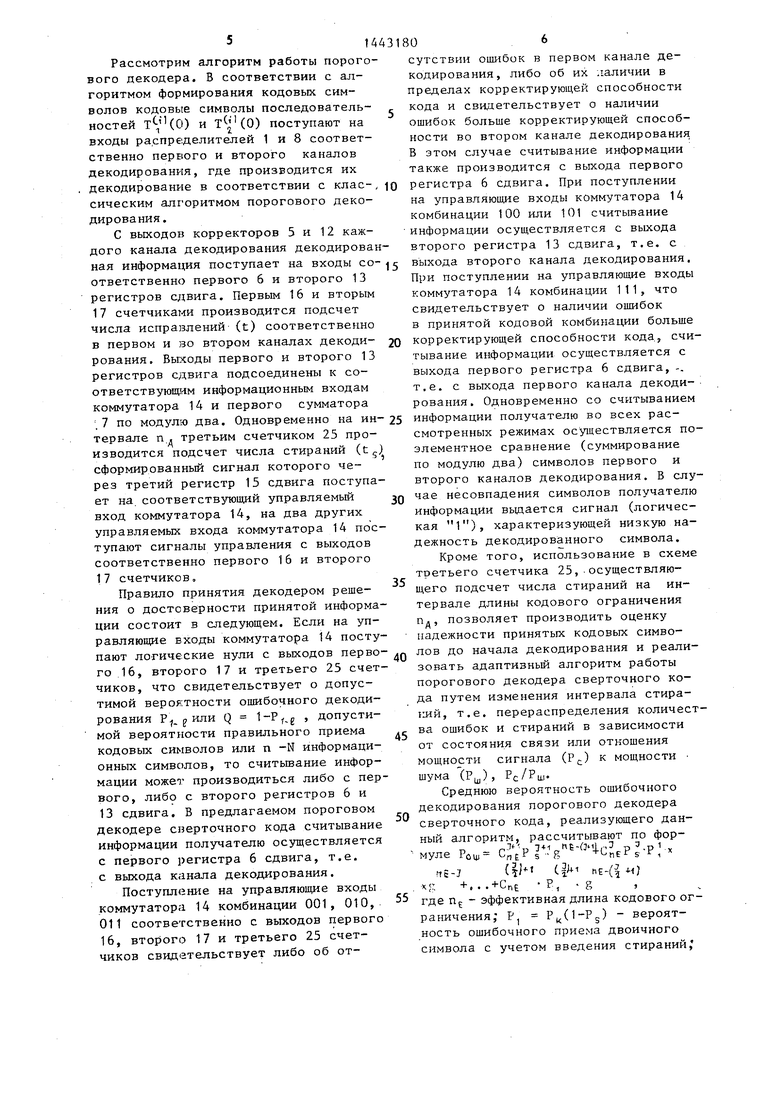

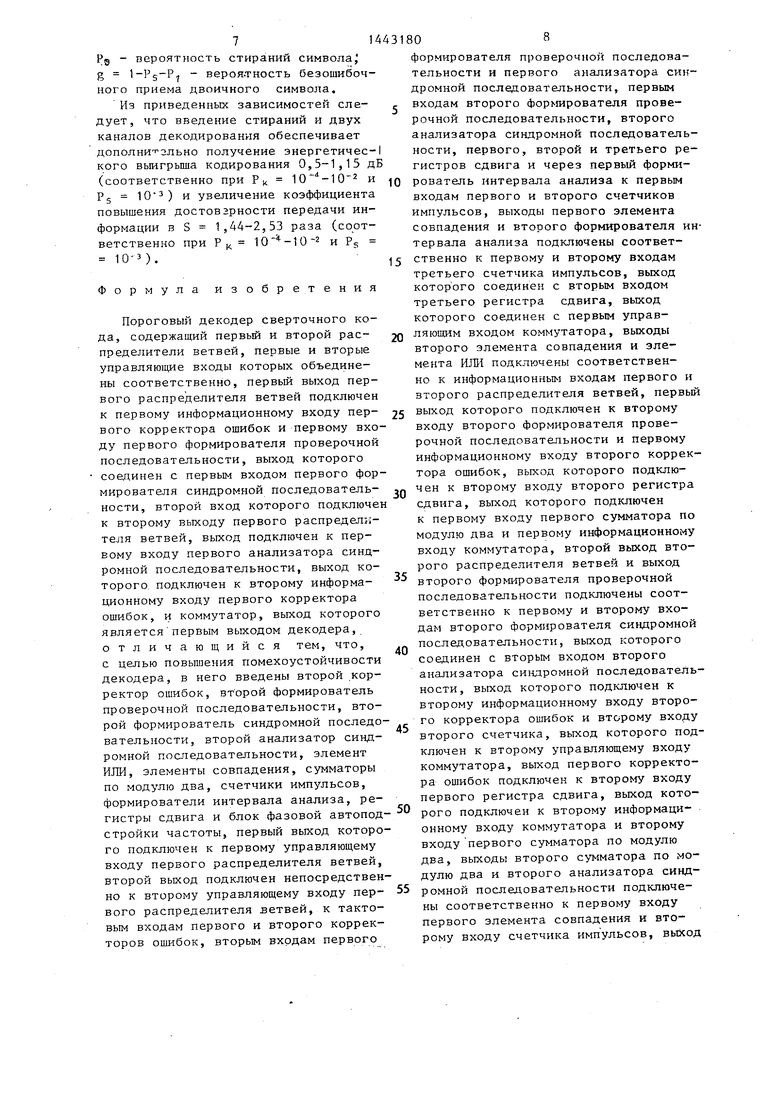

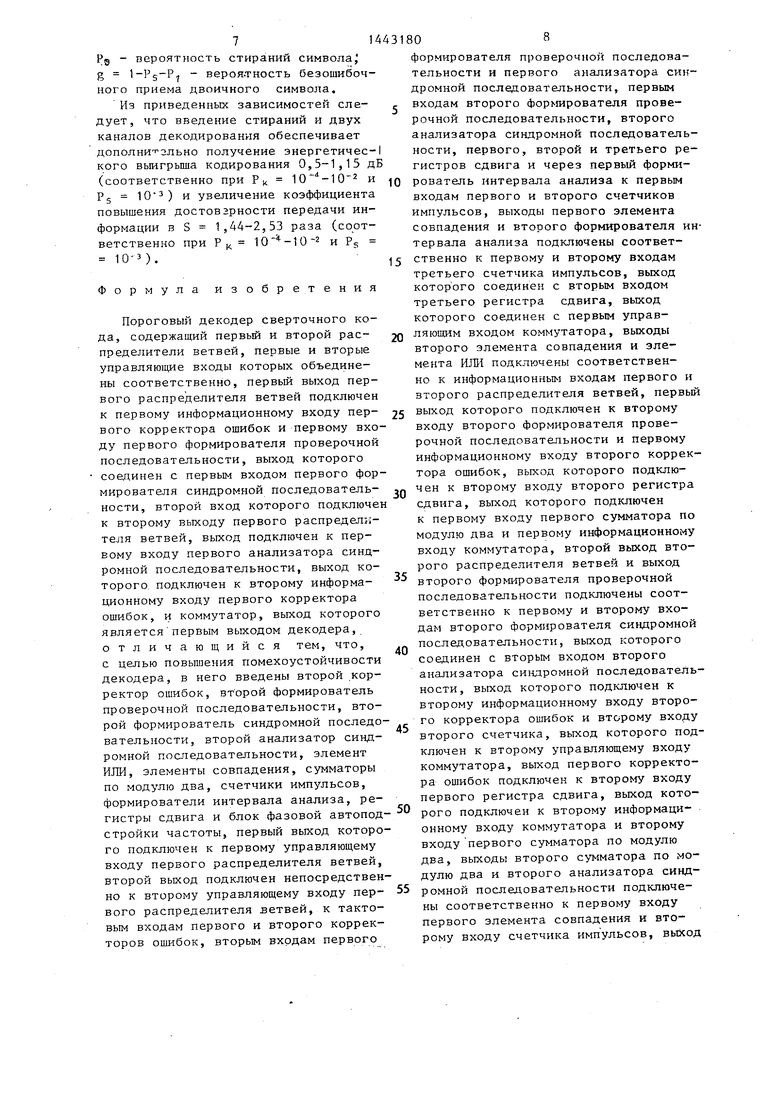

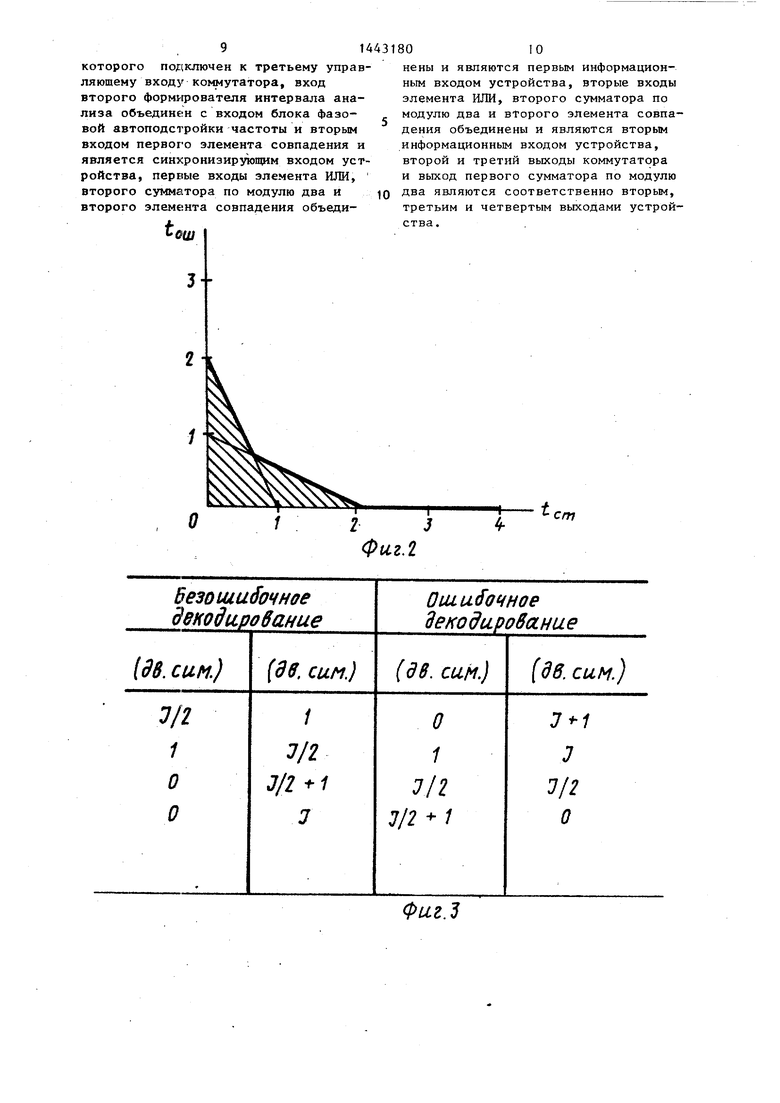

На фиг, 1 приведена структурная электрическая схема порогового декодера сверточного кода на фиг. 2 область безошибочного декодирования порогового декодера сверточного кода на фиг. 3 таблица с корректируемыми и некорректируемыми комбинациями ошибок и стираний; на фиг. 4 - принципиальная электрическая схема формирователя интервала анализа и временные диаграммы, поясняющие принцип работы формирователя интервала анализа.

Пороговый декодер сверточного кода содержит первьм распределитель 1 ветвей, первый формирователь 2 проверочной последовательности, первый формиро1затель 3 синдромной последовательности, первьй анализатор 4 синдромной последовательности, первый корректор 5 ошибок, первый регистр 6 сдвига, первый сумматор 7 по модулю два, второй распредели- тель 8 ветвей, второй формирователь 9 проверочной последовательности, второй 10 формирователь сиддромной последовательности, второй анализатор 11 синдромной последовательности второй корректор 12 ошибок, второй регистр 13 сдвига, коммутатор 14, третий регистр 15, первый и второй счетчики 16 и 17 импульсов, первый формирователь 18 интервала анализа, блок 19 фазовой автоподстройки частоты, второй формирователь 20 интервала анализа, первый элемент 21 совпадения, второй сумматор 22 по модулю два, элемент ИЛИ 23, второй элемент 24 совпадения и третий счетчик 25 импульсов.

Распределитель 1 ветвей предназначен для преобразования входной кодовой последовательности первого канала декодирования из последовательного кода в Ujj выходных параллельных подтоков (в рассматриваемом пороговом декодере ), т.е. разделение кодовой последовательности на поток принятых 1(0) информационных символов и поток принятых проверочных

0

5

0

5

0

5

0

5

0

5

,-(0) символов. Распределитель 8 ветвей выполняет аналогичную функцию только для второго канала декодирования 1(0) и Р (0); имеет одинаковое функциональное построение полностью взаимозаменяемых.

Формирователь 2 проверочной последовательности предназначен для формирования из принятых 1(0) информационных символов проверочной последовательности (0}. Функциональная электрическая схема полностью определяется видом порождающего полинома g(0)1+g(0)+g,j(U) + ...+gjO ) и представляет собой регистр сдвига либо с вынесенными (схема Возенкрафта- Рейффена), либо с встроенными (схема Месси) сумматорами по модулю два (2).

Формирователь 9 имеет аналогичное построение и .принцип работы и предназначен для формирования проверочных символов (0) из принятых 1,(0) информационных символов второго канала декодирования.

. Формирователь 3 синдромной последовательности предназначен для формирования синдромной последовательности SДО) путем суммирования по модулю два символов принятой проверочной последовательности Р пр (0) и символов сформированной проверочной последовательности Р 1сф(0) т.е. Si , РПР (0)(0). В качестве ФСП 3 может быть использован один элемент ИМС К155ЛП5. Формирователь 10 второго канала декодирования имеет аналогичное построение и назначение, только суммирование по модулю два производится символом принятой проверочной последовательности Р (0) и символом сформированной проверочной последовательности (Р1сф(0)), т.е. S(0) Pnp(0).(0).

Анализатор 4 синдромной последовательности .предназначен для анализа синдромной последовательности S .,(0) с целью принятия решения о достоверности декодируемой информации по первому каналу декодирования. В качестве анализатора 4 используется регистр сдвига со встроенными сумматорами по модулю два (2). Длина регистра сдвига определяется максимальной степенью m порождающего полинома g(0)1+g ,(О ) + ...-bgJO J, а число сумматоров по модулю два равно (1-1)

Аналогичное построение имеет анализатор 11, предназначенный для принятия решения о достоверности декодируемой информации по второму каналу декодирования.

Корректор 5 ошибок предназначен для согласования по времени информационных символов первого канала декодирования и символов коррекции, поступающих, с выхода анализатора 4.

Аналогичное построение имеет корректор 12 и предназначен для согласования по времени информационных символов второго канала декодирования и символов коррекции, поступающих с выхода анализатора 11 .

Первьш сумматор 7 по модулю два предназначен для формирования сигналов, указывающих месторасположение в де кодированной информации символов, имеющих различную достоверность в соответствующих каналах декодирования. Это обеспечивает при декодировании получение дополнительной информации как об одном символе, так и о комбинации декодированных символов. Формирование сигналов производится путем поэлементного суммирования по модулю два декодированных символов первого и второго каналов декодирова

ячеек памяти, где п, -коэффициент, учитываюищй разную скорость поступления информации на входе декодера и скорости записи информации в первом, и во втором регистрах 6 и 13 сдвига.

Первый счетчик 16 предназначен для подсчета числа коррекций на длине кодового ограничения Пд первого канала декодирования. Коэффициент счета выбирается равным К.с(. i-i + 2

1, где I - число ортогональных проверок сверточного кода.

Аналогичное построение и принцип работы имеет второй счетчик 17, предназначенный для подсчета числа коррекций на длине кодового ограничения Пд второго канала декодирования .

Первый формирователь 18 интервала анализа предназначен для формирования интервала анализа, на котором

производится подсчет количества исправлений как в первом, так и во втором канале декодирования. Интервал анализа выбирается равным 1 т, где m - максимальная степень порож

| название | год | авторы | номер документа |

|---|---|---|---|

| Пороговый декодер сверточного кода | 1982 |

|

SU1078654A1 |

| Устройство для устранения неопределенности дискретнофазовой модуляции | 1983 |

|

SU1095428A1 |

| Кодек несистематического сверточного кода | 1990 |

|

SU1714812A1 |

| ПОРОГОВЫЙ ДЕКОДЕР СВЕРТОЧНОГО КОДА | 1991 |

|

RU2023349C1 |

| Сверточный кодек с алгоритмом порогового декодирования | 1985 |

|

SU1327296A1 |

| Декодер сверточного кода (его варианты) | 1985 |

|

SU1320875A1 |

| Декодер сверточного кода | 1985 |

|

SU1320904A1 |

| Кодек несистематического сверточного кода | 1988 |

|

SU1580567A1 |

| Декодер сверточного кода | 1986 |

|

SU1388998A1 |

| Пороговый декодер сверточного кода | 1985 |

|

SU1252944A1 |

Изобретение относится к технике I связи и может использоваться в устройствах помехоустойчивого кодирования при передаче двоичной информации. 2V Изобретение позволяет повысить помехоустойчивость порогового декодера сверточного кода, рассчитанного для коррекции независимых ошибок за счет введения ненадежных кодовых символов, двух каналов декодирования. Пороговьй декодер сверточного кода содержит распределители 1 и 8 ветвей, формирователи 2 и 9 проверочной последовательности, формирователи 3 и 10 синдромной последовательности, анализаторы 4 и 11 синдромной последовательности, корректоры 5 и 12 ошибок, регистры 6, 13 и 15 сдвига, сумматоры 7 и 22 по модулю два, коммутатор 14, счетчики 16, 17 и 25 импульсов, формирователи 18 и 20 интервала анализа, блок 19 фазовой автоподстройки частоты, элементы 21 и 24 совпадения, элемент ИЛИ 23. 4 ил. (в (Л

35

40

ния. При одинаковых значениях декоди- дающих полиномов выбранного сверточ- рованных символов на выходе первого сумматора 7 по модулю два формируется низкий потенциал (логический нуль) а при разных значениях символов формируется высокий потенциал (логическая единица).

Коммутатор 14 осуществляет считывание информации с первого или второго каналов декодирования в зависимости от достоверности декодированной информации, а также формирует два сигнала Z и Z, характеризующие достоверность декодированной информации; Z , характеризует достоверность декодированной информации в пределах нормы; Z „ характеризует достоверность декодированной информации ниже нормы.

Третий регистр 15 сдвига предназначен для согласования по времени результатов подсчета числа стираний на длине кодового ограничения п д, поступивших на входы первого и второго каналов декодирования, и результата подсчета количества исправлений в каждом из каналов декодирования. Третий регистр 15 сдвига реализуется в виде последовательного регистра сдвига и содержит

ного кода, первый формирователь 18 интервала анализа выполняется в виде двоичного счетчика и дещифратора (фиг. 4),

Блок 19 предназначен для формирования тактовых частот, необходимьк для нормальной работы декодера, является самостоятельным функциональным узлом декодера, которьй может иметь различные схемные реализации.

Второй формирователь 20 интервала анализа предназначен для установления интервала анализа, на котором производится определение количества стираний, поступивших на вход декодера. Интервал анализа выбран равный длине кодового ограничения используе- мЬго сверточного кода. Второй формирователь 20 интервала анализа реализуется по такому же принципу как первый формирователь 18 интервала ана лиза, отличие состоит только лишь в фиксируемой длине интервала анализа

().

второй сумматор 22 по модулю два предназначен для формирования ненулевых символов при фиксировании сигналов стирания.

45

50

дающих полиномов выбранного сверточ-

ного кода, первый формирователь 18 интервала анализа выполняется в виде двоичного счетчика и дещифратора (фиг. 4),

Блок 19 предназначен для формирования тактовых частот, необходимьк для нормальной работы декодера, является самостоятельным функциональным узлом декодера, которьй может иметь различные схемные реализации.

Второй формирователь 20 интервала анализа предназначен для установления интервала анализа, на котором производится определение количества стираний, поступивших на вход декодера. Интервал анализа выбран равный длине кодового ограничения используе- мЬго сверточного кода. Второй формирователь 20 интервала анализа реализуется по такому же принципу как первый формирователь 18 интервала анализа, отличие состоит только лишь в фиксируемой длине интервала анализа

().

второй сумматор 22 по модулю два предназначен для формирования ненулевых символов при фиксировании сигналов стирания.

Рассмотрим алгоритм работы порогового декодера. В соответствии с алгоритмом формирования кодовых символов кодовые символы последовательностей ) и (О) поступают на входы распределителей 1 и 8 соответственно перЕюго и второго каналов декодирования, где производится их декодирование в соответствии с классическим алгоритмом порогового декодирования.

С выходов корректоров 5 и 12 кажсутствии ошибок в первом канале декодирования, либо об их наличии в пределах корректирующей способности кода и свидетельствует о наличии ошибок больше корректирующей способности во втором канале декодирования В этом случае считывание информации также производится с выхода первого регистра 6 сдвига. При поступлении на управляющие входы коммутатора 14 комбинации 100 или 101 считывание информации осуществляется с выхода второго регистра 13 сдвига, т.е. с

дого канала декодирования декодированная информация поступает на входы со- выхода второго канала декодирования, ответственно первого 6 и второго 13 При поступлении на управляющие входы регистров сдвига. Первым 16 и вторым коммутатора 14 комбинации 111, что 17 счетчиками производится подсчет числа исправлений (t) соответственно в первом и во втором каналах декодирования. Вькоды первого и второго 13 регистров сдвига подсоединены к соответствующим информационным входам

20

свидетельствует о наличии ошибок в принятой кодовой комбинации больше корректирующей способности кода,, считывание информации осуществляется с выхода первого регистра 6 сдвига, -. т.е. с вькода первого канала декодирования. Одновременно со считыванием

коммутатора 14 и первого сумматора

1 по модулю два. Одновременно на ин- 25 информации получателю во всех рас- тервале п . третьим счетчиком 25 про- смотренных режимах осуществляется поизводится подсчет числа стираний (t) элементное сравнение (суммирование сформиррванньй сигнал которого через третий регистр 15 сдвига поступало модулю два) символов первого и второго каналов декодирования. В слу

ет на соответствующий управляемый вход коммутатора 14, на два других управляемых входа коммутатора 14 поступают сигналы управления с выходов соответственно первого 16 и второго 17 счетчиков.

Правило принятия декодером решения о достоверности принятой информации состоит в следующем. Если на управляющие входы коммутатора 14 поступают логические нули с выходов перво- го 16, второго 17 и третьего 25 счетчиков, что свидетельствует о допустимой вероятности ошибочного декодирования Р. р или Q 1-P,g допустимой вероятности правильного приема кодовых символов или п -N информаци- онньпс символов, то считывание информации может производиться либо с первого, либо с второго регистров 6 и 13 сдвига. В предлагаемом пороговом декодере сверточного кода считывание информации получателю осуществляется с первого регистра 6 сдвига, т.е. с выхода канала декодирования.

Поступление на управляющие входы коммутатора 14 комбинации 001, 010, 011 соответственно с выходов первого 16, второго 17 и третьего 25 счетчиков свидетельствует либо об от

0

сутствии ошибок в первом канале декодирования, либо об их наличии в пределах корректирующей способности кода и свидетельствует о наличии ошибок больше корректирующей способности во втором канале декодирования В этом случае считывание информации также производится с выхода первого регистра 6 сдвига. При поступлении на управляющие входы коммутатора 14 комбинации 100 или 101 считывание информации осуществляется с выхода второго регистра 13 сдвига, т.е. с

выхода второго канала декодирования, При поступлении на управляющие входы коммутатора 14 комбинации 111, что

выхода второго канала декодирования, При поступлении на управляющие входы коммутатора 14 комбинации 111, что

свидетельствует о наличии ошибок в принятой кодовой комбинации больше корректирующей способности кода,, считывание информации осуществляется с выхода первого регистра 6 сдвига, -. т.е. с вькода первого канала декодирования. Одновременно со считыванием

информации получателю во всех рас- смотренных режимах осуществляется поэлементное сравнение (суммирование

ло модулю два) символов первого и второго каналов декодирования. В слу5

д

Q

5

0

чае несовпадения символов получателю информации выдается сигнал (логическая 1), характеризующей низкую надежность декодированного символа.

Кроме того, использование в схеме третьего счетчика 25,.осуществляющего подсчет числа стираний на интервале длины кодового ограничения Пд, позволяет производить оценку надежности принятых кодовых символов до начала декодирования и реализовать адаптивный алгоритм работы порогового декодера сверточного кода путем изменения интервала стира- 1ШЙ, т.е. перераспределения количества ошибок и стираний в зависимости от состояния связи или отношения мощности сигнала (Р,) к мощности шума (Рц,), РС/РШ.

Среднюю вероятность ошибочного декодирования порогового декодера сверточного кода, реализующего данный алгоритм, рассчитывают по ,

муле Р, с;, 16-7 (

х;: +,..+СПЕ

,3

ПбР S

р1

пЕ-(| J-0

g

5 где Hg - эффективная длина кодового ограничения; Р P(l-Pj) - вероятность ошибочного приема двоичного символа с учетом введения стираний,

Pg - вероятность стираний символа, g вероятность безошибочного приема двоичного символа.

Из приведенных зависимостей следует, что введение стираний и двух каналов декодирования обеспечивает дополни-г-ально получение энергетического выигрьша кодирования 0,5-1,15 д (соответственно при 10 -10 2 и Pg 10) и увеличение коэффициента повышения достоварности передачи информации в S 1,44-2,53 раза (соответственно при Рц 10 -10 2 и РЗ

10-3).

Формула изобретения

Пороговый декодер сверточного кода, содержащий первый и второй рас- пределители ветвей, первые и вторые управляющие входы которых объединены соответственно, первый выход первого распределителя ветвей подключен к первому информационному входу пер- вого корректора ошибок и первому входу первого формирователя проверочной последовательности, выход которого соединен с первым входом первого формирователя синдромной последователь- ности, второй вход которого подключе к второму выходу первого распределителя ветвей, выход подключен к первому входу первого анализатора синдромной последовательности, выход которого подключен к второму информа- ционному входу первого корректора ошибок, и коммутатор, выход которого является первым выходом декодера,.

отличающийся тем, что.

с целью повышения помехоустойчивости декодера, в него введены второй .корректор ошибок, второй формирователь проверочной последовательности, второй формирователь синдромной последовательности, второй анализатор синдромной последовательности, элемент ИЛИ, элементы совпадения, сумматоры по модулю два, счетчики импульсов, формирователи интервала анализа, регистры сдвига и блок фазовой автопод стройки частоты, первый выход которого подключен к первому управляющему входу первого распределителя ветвей, второй выход подключен непосредственно к второму управляющему входу пер- вого распределителя ветвей, к тактовым входам первого и второго корректоров ошибок, вторым входам первого

т-

1 Q

15

20 25 ,Q

40

45

55

50

формирователя проверочной последовательности и первого анализатора синдромной последовательности, первым входам второго формирователя проверочной последовательности, второго анализатора синдромной последовательности, первого, второй и третьего регистров сдвига и через первый формирователь интервала анализа к первым входам первого и второго счетчиков импульсов, выходы первого элемента совпадения и второго формирователя интервала анализа подключены соответственно к первому и второму входам третьего счетчика импульсов, выход которЪго соединен с вторым входом третьего регистра сдвига, выход которого соединен с первым управ- ляюшкм входом коммутатора, выходы второго элемента совпадения и элемента ИЖ подключены соответственно к информационным входам первого и второго распределителя ветвей, первый выход которого подключен к второму входу второго формирователя проверочной последовательности и первому информационному входу второго корректора ошибок, выход которого подключен к второму входу второго регистра сдвига, выход которого подключен к первому входу первого сумматора по модулю два и первому информационному входу коммутатора, второй выход второго распределителя ветвей и выход второго формирователя проверочной последовательности подключены соответственно к первому и второму входам второго формирователя синдромной последовательности, выход которого соединен с вторым входом второго анализатора синдромной последовательности, выход которого подключен к второму информационному входу второго корректора ошибок и второму входу второго счетчика, выход которого подключен к второму управляющему входу коммутатора, выход первого корректора ошибок подключен к второму входу первого регистра сдвига, выход которого подключен к второму информационному входу коммутатора и второму входу первого сумматора по модулю два, выходы второго сумматора по модулю два и второго анализатора синдромной последовательности подключены соответственно к первому входу первого элемента совпадения и второму входу счетчика импульсов, выход

которого подключен к третьему управляющему входу коммутатора, вход второго форм1 рователя интервала анализа объедин€ Н с входом блока фазовой автоподстройки частоты и вторым входом первого элемента совпадения и является синхронизирующим входом устройства, nepEtbie входы элемента ИЛИ, второго сумматора по модулю два и второго элем€ нта совпадения объеди езоили чноеЗекодирование

44318010

иены и являются первым информационным входом устройства, вторые входы элемента ИЛИ, второго сумматора по модулю два и второго элемента совпадения объединены и являются вторым информационным входом устройства, второй и третий выходы коммутатора и выход первого сумматора по модулю 0 два являются соответственно вторым, третьим и четвертым выходами устройства.

cm

фиг.2

OuLufoffHoe декодирование

Фиг.З

;;

fe

V. CS, : QO

Vx

Vv

V.

%

I

1

t

LJ

CV4

| Пороговый декодер сверточного кода | 1984 |

|

SU1185629A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

| Касами Т | |||

| и др | |||

| Теория кодирования- М.: Мир, 1978, с | |||

| Стеклографический печатный станок с ножной педалью | 1922 |

|

SU236A1 |

| Кипятильник для воды | 1921 |

|

SU5A1 |

| Декодер сверточного кода | 1986 |

|

SU1388998A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

Авторы

Даты

1988-12-07—Публикация

1986-12-15—Подача