мя входами регистра адреса и регистра данных, третий вход регистра данных соединен с 1ретьим входом регистра адреса и вторым входом узла синхронизации, третий вход узла синхронизации со@дш1ен с вторым выходом дешифратора сигнаяов управления, первый вход которого соединен с третьим входом деишфратора адреса, второй выход дешифратора адреса соединен с першым входом узла управления обменом, второй вход которого соединен с третьим выходом узла синхроииэацш, третий вход узла управления обменом соединен с вторым вьсходом регистра адреса, четвертым входом соединенного с третыш выходом дешифратора адреса,, четвертый вход дешифратора адреса соединен с четвертым выходом узла синхронизации, соединенного двусторонними связями с шифратором сигналов управления 2. Это устройство не позволяет транслировать сигналы сопряжения ввода-вывода ЭВМ типа общей шины, в том числе передачу приоритетов запросов от периферийных устройств, оптимизировать в зависимости от вида информации форматы передаваемой посылки, использовать одинаковые схемы для передачи информации, а также обеспечивать необходимую степень совмещения процедур обмена данными между ЭВМ и периферийными устройствами.

Цель изобретения - повышение скорости обмена информацией ЭВМ с абонентами. В описываемом устройстве зто достигается тем, что в него дополнительно введены шифратор данных, дешифратор данных, регистр сдвига, коммутатор, узел задания форматов, первый выход которого соед 1ен с четвертым входом узла управления обменом, а вход - с первым выходом коммутатора и с первым входам дешифратора сигналов управления, второй выход узла задания форматов соединен с вторыми входами дешифратора сигналов управления и шифратора сигналов управления, выход шифратора сигналов управления соединен с первым входом регистра сдвига, второй вход которого соединен с третьим выходом узла задания форматов, первый выход регистра сдвига соединен с третьим входом дешифратора сигналов управления, второй - с первым входом коммутатора, вторые вход и выход которого соединены соответственно с выходом и входом первого узла связи, третий выход - с третьим входом шифратора сигналов управления, четвертый выход - с третьим входом регистра сдвига, первый вход шифратора данных соединен с первым выходом узла управления обменом, второй выход которого соединен с первым входом дешифратора данных, второй вход дешифратора данных соединен с выходом регистра приема, а выход - с третьим входом регистра данных, выход шифратора данных соединен с входом регистра передачи, второй вход - с третьим

ВЫХОДОМ решстра адреса, третий вход - с вторым выходом регистра данных.

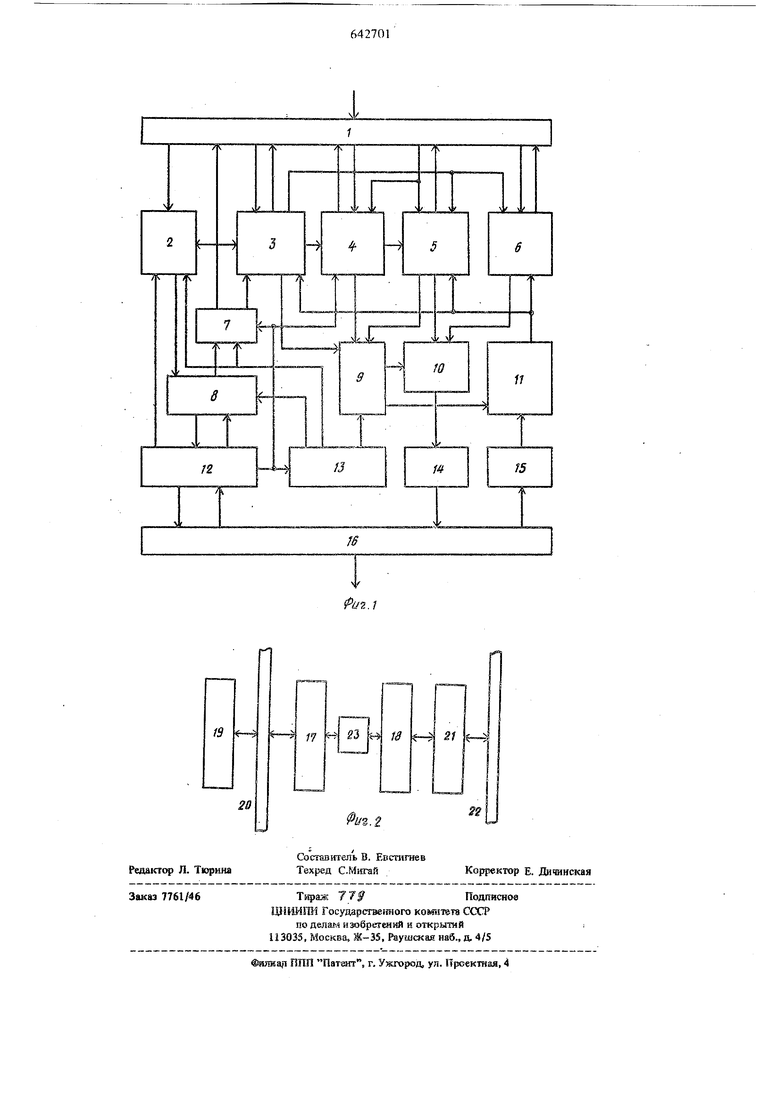

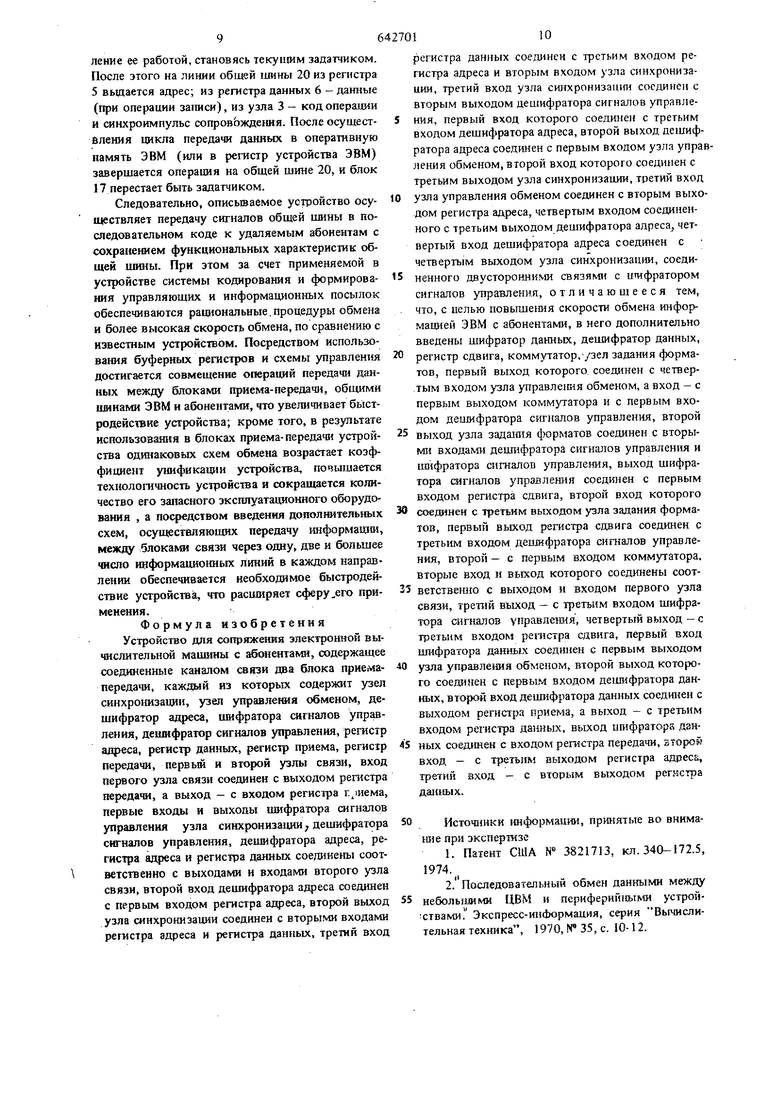

На фиг. 1 представлена блок-схема описываемого устройства; на фиг. 2 - схема соединения устройства с ЭВМ и с абонентами.

Устройство содержит второй узел 1 связи, шифратор 2 сигналов управления, узел 3 синхронизаиЕки, дешифратор 4 , регистр 5 адреса, регистр 6 данных, дешифратор 7 сигналов управления, pej-истр 8 сдвига, узел 9 управления обменом, шифратор 10 данных, дешифратор 11 данных, коммутатор 12, узел 13 задания форматов, регистр 14 передачи, регистр 15 приема, первый узел 16 связи, блоки 17 и 18 приема-передачи, блок 19 управления обшей шиной ЭВМ, общую шину 20 ЭВМ, блок 21 управления общей шиной абонентов, общую шину 22 абонентов и канал 23 связи.

Абоненты связываются с устройствами ЭВМ (процессором, оперативной памятью н др.) с помощью следующих основных типов операций: захвата цшны, прерывания программы и передачи данных.

Операции передачи данных осуществляются относительно задающего устройства (задатчика); ввод данных (чтение) вьшолняется всегда от исполнителя к задатчику, а выход данных (запись) - от задатчика к исполнителю.

ОЛрация захвата шины служит для подготовки к передаче управления обшей шиной 20 от текущего абонента к очередному и происходит следующим образом. Шифратор шгналов управления блока 18 приема-передачи с помощью коммутатора 12, настраивается на щифрапнк сигналов запроса, шифратор 2 сигналов управления блока 17 приема-передачи - на шифрацию сигналов управления от общей щины 20, дешифратор 7 сигналов управления блока 18 приема-передачи на дешифрацию сигналов управления, а дешифратор 7 сигналов управления блока 17 приема-передачи - на дешифрацию сигналов запроса. Запрашивающее устройство абонента выставляет сигнал запроса по соответствующей линии общей шины 22, который поступает в блок 21. При зтом одновременно может быть выставлено несколько запросов произвольного приоритета от разных абонентов. В блоке 21 анализируется,осуществляется ли абонентом в текущий момент времени операция захвата шины 22. Если она осуществляется, то запросы в блок 21 не принимаются, если же нет, - то запросы поступают в блок 21. В блоке 21 вьщеляется наиболее приоритетный запрос, который передается в шифратор сигналов управления блока 18. В шифраторе 2 осуществляется его ишфрация в соответствующий трехразрядный двоичный код (например, для запросов пяти уровней приоритета): 001-запрос 1-го урювня приоритета; 010 -запрос 2-го уровня приS64

сритета; Oil - запрос 3-го уровня приоритета; 100- запрос 4-го уровня приоритета; 101запрос 5-го уровня приоритета. Сформированный запрос (например, S П,, i г J 5) поступает затем из шифратора 2 в регис1р сдвига, в нем осуществляется преобразование параллельного кода запроса в последовательный код, которым через коммутатор 12 поступаег на второй узел связи 1. Одновременно с поразрядной передачей кода запроса регистр сдвига 18 формирует oiHхроимпульсы сопровождения, передающиеся через коммутатор 12 на первый узел 16 связи. С выхода второго узла I сяязи блока iS запрос в последовательном коде поступает через канал 23 связи на первый узел 16 связи блока 17, в котором осущесгеляются дальнейшие onepaujiH. Через канал 23 связи на вход первого узла 16 поступают синхроимпульсы сопровожден запросов. С выхода второго узла 1 связи сигналы запроса и сиихроннзаиии поступают через коммутатор 12 на регистр 8 сдвига, с помощью которого осуществляется преобразование последсшательного кода запроса в параллельный код. Затем код запроса передается в дешифратор 7 ао-налов управления, где осуществляется дешифрация параллельного кода запроса и форьшрование запрсь са соответствующего уровня приоритета (ЗЯ i 1-5).

После осушептвления операц ш захват общей шиной запраилшающее устр(жство подготавливается к вшюлнению операции прерывания. В процессе передачи запроса из блока 18 в блок 7 запрашивающее устройство осуществляет операцию прерывания на общей шине 22. В результате ее выполнения в узле синхронизаши блока 18 запоминается признак прерывания, а в решстре данных 6 - адрес вектсфа прерывания, переда,ваемый из устройства через второй узел связа I. Признак прерывания затем поступает в шифратор 2 сигналов управления, а адрес вектора прерывания - в идафратор 10 данных. В шифраторе 2 осуществляется шифрация сигнала прерывания в трехразрядный двоичный код (например, для рассматриваемого уровня 110). Из шифратоpa 2 шифрованный признак прерьшания передается в регистр 8 сдвига, из которого он в последовательном коде поступает с синхроимпульсами сопровождения через коммутатор 12 и первый узел 16 связи и канал 23 связи в блок 17 приема-передачи. В шифраторе 10 выполняется шифрация признака адреса вектора в трехразрядный двоичный код и формирование в параллельном коде посылю адреса вектора прерывания, формат которой: (0-2) разряды - признак адреса вектора прерывания, (3-10) разряды - адрес вектора прерьшания. Из шифратора 10 сформированная посылка поступает в регистр 14 передачи, где осуществляется 1)еобразование иараллельноto кода посылки в последовательный код и его передача вместе с синхр жмпульсами сопровождения через первый узел 16 связи и канал 23 связи в блок 17 приема-передачи. В блоке 17 с помощью узлов 16, 12 и 18 осуществляются прием и восстановленне признака прерывания-и его запоминание в узле шнхронизацин 3, а с помощью узлов 16, IS и 11 осуществляются прием и восстановлею1е в параллельном коде адреса вектора прерьюаняя н его 3anoNeiHaHHe в регистре 6.

Таким образом, в узле синхронизации блока 17 имеется запрос передачи соответствующего прио{ 1тета и признак прерывания, в регистре данных 6 - адрес вектора прерывания.

Блок 17 осуществляет сначала посредством узла 3 операцшо захвата общей шины ЭВМ, а затем операцию прерывания, в результате которой передает в процессор через блок 19 а/фес вектора прерывания из регастра 6 от абонента.

В результате выполнеш я прерывания процесс ф организует процедуру (Лмена данными с запрашиваемым абонентом, которая происходат следуюи01м образом. Процессор с помощью блока 19 становится текущим задагадком, устанавл}тает на общей шине 20 код операции и адрес регистра абона1та и посылает синхросигнал сопровождения. Этот сигнал и код операции поступают в узел 3 синхронизаоди блока 17, а адрес на первый и второй входы соответственно регистра 5 адреса и деишфрагора 4 адреса. По сигналу разрешения из узла синхронизации 3 в дешифраторе 4 осуществляется дешифрация адреса. В случае его (хютветствйя регистров абонентов осуществляется пртем адреса в регастр 6 данных.

При onepauiiH записи в зависимости от кода операшш происхогщт прием в регистр 6 либо слова, либо старшего или младд1его байта данных.

Операция записи на общей шине ЭВМ завершается с помоца ю блоков 17 и 19, после чего блок 19 берет управление общей шиной 20. После приема адреса при операщш записи осуществляется такая последовательность действий. В шифраторе с помощью узла 9 управления обменом производятся цшфрация признака адреса в трехразрядный двоичный код, ф()p fflpoвaниe кода посылки адреса, поступающего в шифратор 10 из регистра 5 адреса. Сформированный код посылки адреса передается в регистр 14 передачи. В нем осуществляются преобразование параллельного кода посылки в последовательный и его передача в блок 18 вместе с синхроимпульсалад сопровождения через первый узел 16 связи и канал 23 связи.

При использовании для передачи а;фесов и данньис из блока 17 в блок 12 одной информаШ1ОННОЙ линии, после передачи посылки адреса в блок 18, в шифраторе 10 с (юмошьш б.-ш ка 9 управления обменом осу1иествляе ся inn(|ipaция признака передаваемых данных в трехразрядный двоичный код. Двоичное число, записываемое, например, с помощью трех разрядов и используемое в процедуре обмена данными, обозначает: О - не используются, 1- признак адреса; 2 - признак слова данных записи; 3- признак старшего байта данных записи; 4 - признак младшего байта записи; .5 - признак чтения слова данных; 6 - признак чтения старшего байта данных; 7 - признак чтения младшего байта данных. После пересылки адресной посылки из блока 1 аналогично осуществляется передача посылки данньк в блок 18. В блоке 18 с помощью регистра 15 приема производится перевод посылок адреса и данных в параллельный код, который поступает в дешифратор 11 дшшых. В нем осуществляется декодирование признаков посылок. Затем адреса и данные из дешифратора 11 запоминаются соответственно в регистрах 5 к 6. В узел синхронизации 3 из дешифратора 11 поступает кодированный двухразрядный код операции. Узел 16 блока 18 осуществляет операцию захвата общей шины и затем берет управление общей шиной 22. В случае операции записи данные передаются из регистра 6 через первьш узел связи 1 адресуемому абоненту. При операции чтения данные считьшаются от абонента и через второй узел связи 1 поступают в регистр 6, после чего блок 12 завершает операцию чтения на общей шине 22. В шифраторе осуществляется затем формирование кода посылки данных и с помощью регистра 14 передачи ее передача из блока 18 в блок 17. В блоке 17с помощью регистра 15 приема и дешифратора 11 осуществляется формирование данных и запоминание их в регистре 6. Таким образом, при операции чтения из блока 17в блок 18 сначала передается код операции и адрес, по которому в зависимости от кода операции читаются дангпые соответствующего формата из регистра абонента. Считанные данные передаются затем в блок 17. Он посылает принятые данные в процессор и завершает на общей шине операцию чтения. Блок 19 берет управление обшей шиной и на этом заканчивается выполнение операции чтения. Процедура обмена данными между оперативной памятью ЭВМ и абонентом удаленной периферийной системы в режиме прямого доступа, при котором абонент (а не процессор) является задатчиком, а оперативная память испол1штелем, отличается алгоритмом обмена. При этом код операции, адреса и данные (при операции записи) передаются от абонента в оперативную память и ЭВМ следующим образом. Абонент периферийной системы с помощью блока 21 осуществляет операцию захвата общей шины 22. Задатчик выстав618 ляет на линии общей щины 22 разряда адреса код операции, сигналы управления и синх(юнизацин, признак занятости обшей шины и в случае операции записи соответствующие данные. Сигнал синхронизадаи поступает в блоке 1 на узел 3 стнхронизации, адрес - в регистр 5 адреса и на дешифратор 4 адреса. По сигналу из узла синхронизащш 3 осуществляется дешифрация адреса в децшфраторе 4. В случае его несоответствия адресам регистров абонентов осуществляется его прием в регистр 5. При оперзшш записи по сигналам узла 3 в зависимости от кода операции осуществляется прием в регистр 6 блока 18 либо слова, либо старшего или младшего байта данных. Кроме того, эти сигналы передаются из узла 3 в узел 9 управления обменом. Затем в блоке 18 осуществляется такая последовательность действий. В шифраторе 10 управлением узла 9 производатся ишфрацня признака адреса в трехразрядный двоичный код, а затем форм1 роваш1е кода посылки адреса. Код посылка признака адреса и адреса поступают в регистр 14 передачи, где осуществляется их преобразование в последовательный код, передаваемьи вместе с сянхроимпульсалш сопровояодения через первый узел 16 связи и канал 23 связи в блок 17. При использованик для перетчк информации из блока tS в блок 3 7 одной информационной линии, после передачи адреса в блок 17, в шифраторе 10 и блоке 4 осуществляется шифрация признака передаваемых данных и cajkfflx данных s код посылки данных. После передачи в блок J7 адресной посылки из блока 18 осуществляется передача Посылки данных. В блоке 17с помо1ш ю регистра 15 посылки адреса данные переводятся в параллельный код, поступающий в дешифратор 11. В нем декодируются признаки посылок. Затем адрес и данные заносятся соответственно в регистр 5 и дешифратор 4, а в узел 3 из дешифратора 11 поступает кодированный двухразрядный код операции. После этого блок 17 с помощью узла 3, дешифратора 2 и дешифратора 7 и регистра 8 сдвига осуществляет формирование закодированного признака окончания приема посылки и его передачу вместе с синхросигналами сопровождения в блок 18. В блоке 18 эти сигналы через коммутатор 12 поступают на регистр 8, в котором осуществляется перевод посылки в параллельный двоичный код {III). Последний передается в дешифратор 7, где осуществляется его дешифрация, после чего сформированный сигнал управления посылается в узел 3. При операции записи узел 3 через первый узел 16 и канал 23 передает в блок 21 сигнал разрешения осуществления на общей шине операции в режиме прямого доступа в память ЭВМ. Одновременно блок 17 осуществляет операЩ1Ю захвата общей шины 20 и затем берет управление ее работой, становясь текущим задатчиком. После этого на линии общей шины 20 из регистра 5 выдается адрес; из регистра данных 6 - данные (при операции записи), из узла 3 - код операции и синхроимпульс сопровождею1я. После осуществления цикла передачи данных в оперативную память ЭВМ (или в регистр устройства ЭВМ) завершается операция на общей шине 20, и блок 17 перестает быть задатчиком.

Следовательно, описываемое устройство осуществляет передачу сигналов общей шины в последовательном коде к удаляемым абонентам с сохранением функциональных характеристик общей шины. При этом за счет применяемой в устройстве системы кодирования и формирования управляющих и информационных посылок обеспечиваются рациональные, процедуры обмена и более высокая скорость обмена, по сравнению с известным устройством. Посредством использования буферных регистров и схемы управления достигается совмещение операций передачи данных между блоками приема-передачи, общими шинами ЭВМ и абонентами, что увеличивает быстродействие устройства; кроме того, в результате использования в блоках приема-передачи устройства одинаковых схем обмена возрастает коэффициент уннфикащш устройства, повышается технологичность устройства и сокращается количество его запасного эксплуатационного оборудования , а посредством введения дополнитель{&1х схем, осуществляющих передачу 1шформавдш, между блоками связи через одну, две и большее число информацио(гаых линий в каждом направлении обеспечивается необход 1мое быстродействие устройства, что расширяет сферу,его применения.

Формула изобретения

Устройство для сопряже1шя электронной вычислительной с доцентами, содержащее соединенные каналом связи два блока приемапередаш, кажщлй из которьи содержит узел синхро1шзации, узел управле1дая обменом, дешифратор адреса, ишфратора сигналов управления, дешифратор сигналов управления, регистр адреса, регистр данных, регистр приема, регистр передачи, первый и второй узлы связи, вход первого узла связи соединен с выходом регастра передачи, а выход - с входом регистра , первые входы и выходы шифратора сигналов управления узла синхронизации j дешифратора сигналов управления, дешифратора адреса, регистра адреса и регистра данных соединены соответственно с выходами и входами второго узла связи, второй вход дешифратора адреса соещшен с первым входом регистра адреса, второй выход узла сиихронизащш соединен с вторыми входами регистра адреса и регистра данных, третий вход

регистра данных соединен с третьим входом регистра адреса и вторым входом узла синхронизации, третий вход узла синхронизации соедиiron с вторым выходом дешифратора сигналов управлекия, первый вход которого соединен с третьим входом дешифратора адреса, второй выход дешифратора адреса соединен с первым входом узла управления обменом, второй вход которого соединен с третьим выходом узла синхронизации, третий вход

узла управления обменом соединен с вторым выходом регистра адреса, четвертым входом соединенного с третьим выходом дешифратора адреса четвертый вход дешифратора адреса соединен с четвертым выходом узла синхронизации, соединенного двусторонникш связям с итфратором сигналов управления, отличающееся тем, что, с целью повыше1шя скорости обмена информацией ЭВМ с абонентами, в него дополнительно введены шифратор данных, дешифратор данных, регистр сдвига, коммутатор,узел задания форматов, первый выход которого соединен с четвертым входом зла управле шя обменом, а вход - с первым выходом коммутатора и с первым входом дешифратора сго-налов управления, второй выход узла задшшя форматов соединен с вторыми входами дешифратора сигналов управления и шифратора сигаалов управления, выход шифратора сигналов управления соедт1ен с первым входом регистра сдвига, второй вход которого соеданен с третьим выходом узла задания форматов, первый выход регистра сдвига соед1шен с третьим входом дешифратора управления, второй - с первым входом коммутатора, вторые вход и выход которого соедю{ены соответствешю с выходом и входом первого узла связи, третей выход - с третьим входом шифратора а}гналов управле шя, четвертый выход - с третьим входом регистра сдвига, первый вход шифратора данных соединен с первым выходом

узла управления обменом, второй выход которого соединен с первым входом дешифратора данных, второй вход дешифратора данных соединен с выходом регистра приема, а выход - с третьим входом pei Hcipa данных, выход ишфраторк данных соештен с входом регистра передачи, второй вход - с третьим выходом регистра адреса, трети вход - с BTopbiM выходом регистра .

Источники 1шформацни, принятые во внимаloje при экспертизе

1. Патент США № 3821713, кл. 340-172.5, 1974.

2. Последовательный обмен данными между неболь 11ими ЦВМ и периферийтгми устройствами. Экспресс-ин(Ьормация, серия Вычислительная техника, 1970, hf 35, с. Ю-12.

19

/7

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство обмена информацией | 1987 |

|

SU1532941A1 |

| Устройство для сопряжения ЭВМ с абонентом | 1990 |

|

SU1702380A1 |

| УСТРОЙСТВО ДЛЯ СОПРЯЖЕНИЯ ЭВМ С ТЕЛЕФОННЫМИ ЛИНИЯМИ СВЯЗИ | 1992 |

|

RU2006927C1 |

| Устройство для сопряжения внешних устройств с электронной вычислительной машиной | 1983 |

|

SU1100615A1 |

| Устройство для сопряжения ЭВМ с абонентами | 1989 |

|

SU1658163A1 |

| Система ввода-вывода для микропрограммируемой ЭВМ | 1988 |

|

SU1667084A1 |

| Устройство для сопряжения ЭВМ с синхронными каналами передачи данных | 1986 |

|

SU1347083A1 |

| Устройство для сопряжения ЭВМ с внешними устройствами | 1987 |

|

SU1501077A1 |

| Устройство для сопряжения ЭВМ с датчиками состояния телефонных линий связи | 1984 |

|

SU1265786A1 |

| Устройство для сопряжения электронной вычислительной машины с общей шиной | 1983 |

|

SU1144112A1 |

Авторы

Даты

1979-01-15—Публикация

1976-04-12—Подача