Изобретение относится к технике связи и может быть использовано для синхронизации аппаратуры при передаче рекуррентных носледовательностей по каналам связи с груннированием ошибок.

Известно устройство для цикловой синхронизации, содержащее приемник, соединенный с cyMMaTopOiM по модулю два, второй вход которого через генератор опорной носледовательностн соединен с выходом цнклового распределителя, второй выход которого через реверсивный счетчик подключен к пороговому блокуСЙ.

Однако известное устройство в каналах связи с группироваинем помех не обладает достаточно высокой помехоустойчивостью, Это объясняется тем, что в таких каналах число ошибочных знаков в пачке может превышать заданный порог счетчика ошибок. С другой стороны, повышение порога счетчика приводит к возрастанию ложного приема псевдослучайного сигнала (ПС).

Целью изобретения является повышенне помехоустойчивости синхронизации в каналах связи с группированием помех.

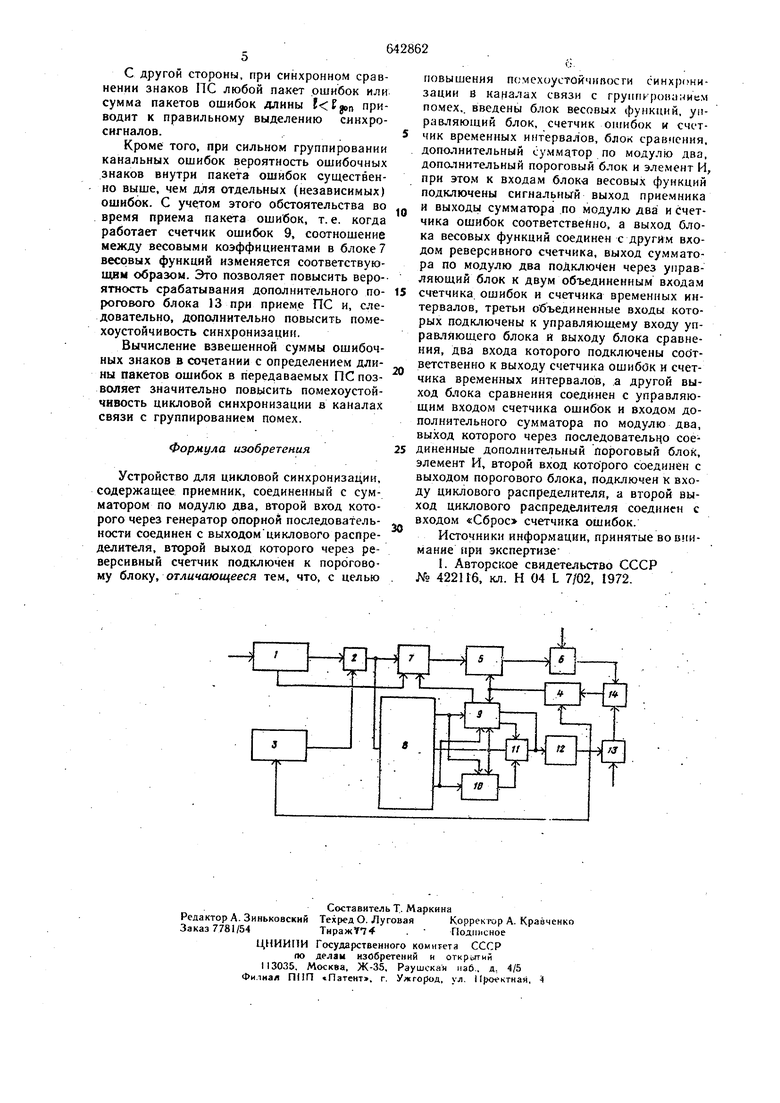

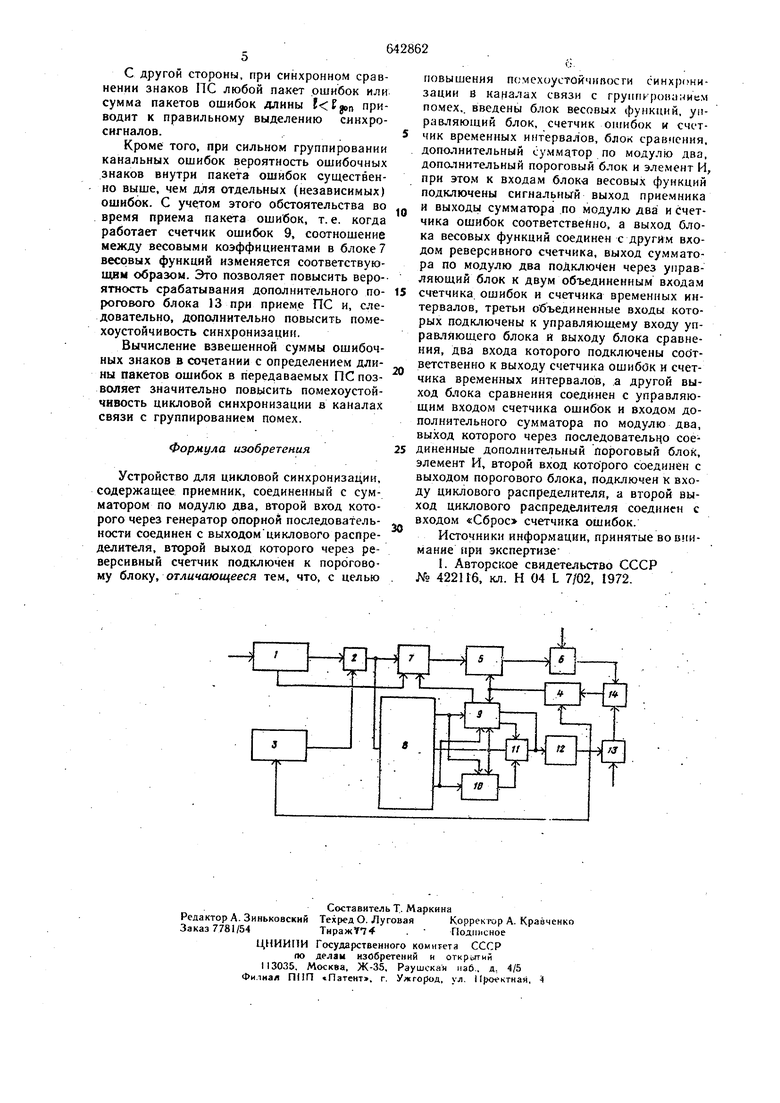

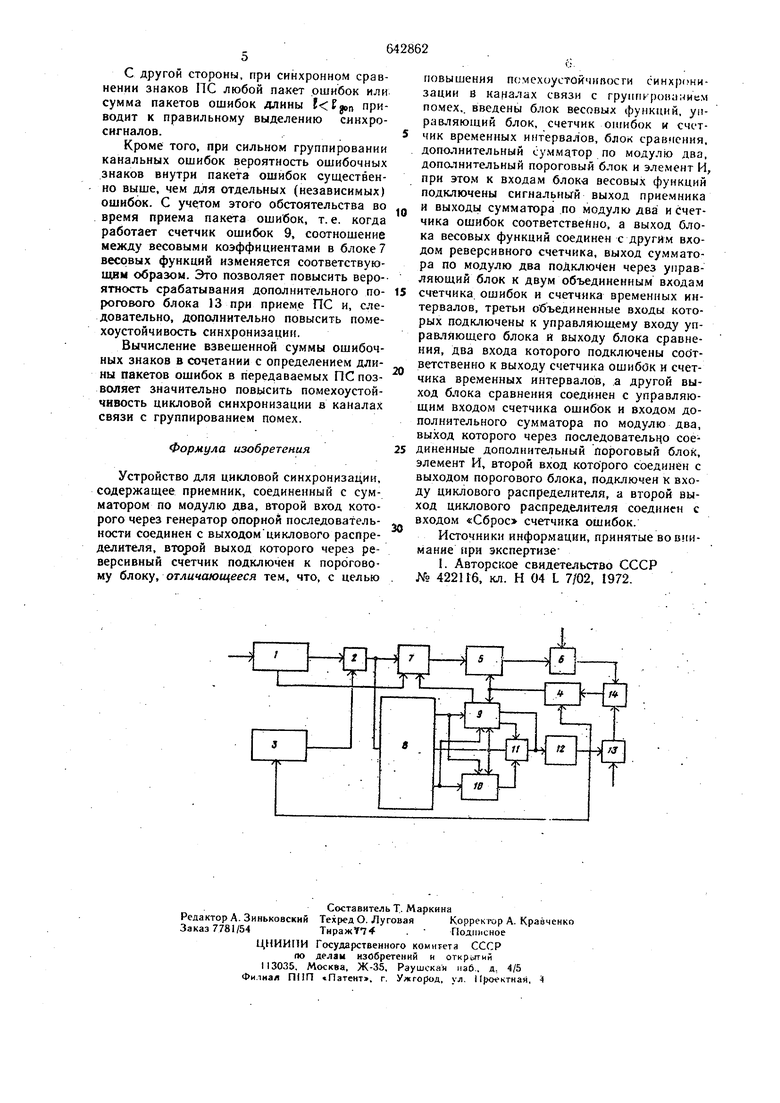

Д.ЛЯ этого в устройство для цикловой синхронизации, содержащее Приемник, соединенный с сумматором по модулю два, второй вход которого через генератор опорной последовательности соедяпен с выходом циклового распределителя, .второй выход которого через реверсивный счетчик подключен к пороговому блоку, ввех1ены блок весовых функций, управляющий блок, счетчик ошибок я счетчик временных интервалов, блок сравнения, дополнительный сумматор по модулю два дополнительный пороговый блок и элемент И, при этом к входам блока весовых функций подключены сигнальный выход приемника н выходы сумматора по модулю два и счетчика ошибок соответственно, а выход блока весовых функций соединен с другим аходом реверсивsного счетчика, выход сумматора по модулю два подключен через управляющий блок к двум объединенным входам счетчика ошибок н счетчика временных интервалов, третьи объединенные входы которых подключены к управляющему входу управляющего блока и выходу блока сравнения, два входа которого подключены соответственно к выходу счетчика ошибок и счетчика временных интервалов, а другой выход блока сравнения соединен с управляющим входом счетчика ошибок и входом дополнительного сумматора по модулю-два, выход которого через последовательно соединенные дополнительный пороговый блок, элемент И, второй вход которого соединен с выходом порогового блока, подключен к входу циклового распределителя, а второй выход циклового распределителя соединен с входом «Сброс счетчика ошибок. На чертеже приведена структурная электрическая схема устройства. Устройство для цикловой синхронизации содержит приемник 1, соединенный с сумматором 2 по модулю два, второй вход которого через генератор 3 опорной последовательности соединен с выходом циклового распределителя 4, второй выход которого через реверсивный счетчик 5 подключен к пороговому блоку 6, а также блок 7 весовых функций, управляющий блок 8, счетчик ошибок 9 и счетчик 10 временных интервалов, блок сравнения 11, дополнительный сумматор 12 по модулю 2, дополнительный пороговый блок 13 и элемент И 14, при этом к входам блока 7 весовых функций подключены соответственно сигнальный выход приемника 1 и выходы сумматора 2 по модулю два и счетчика ошибок 9, а выход блока 7 весовых функций соедиген с ругим входом реверсивного счетчика 5, выход сумматора 2 по модулю два подключен через управляющий блок 8 к двум объединенным входам счетчика ошибок 9 и счетчика временных интервалов 10, третьи объединенные входы которых подключены к управляющему входу управляющего блока 9 и выходу блока сравнения И, два входа которого подключены соответственно к выходу счетчика сшибок 9 и счетчика временных интервалов 10, а другой выход блока сравнения 11 соединен с управляющим входом счетчика ошибок 9 и входом дополнительного сумматора 12, выход которого через последовательно соединенные дополнительный пороговый блок 13, элемент И 14, второй вход которого соединен с выходом порогового блока 6, подключен к входу циклового распределителя 4, а второй выход циклового распределителя 4 соединен с входом «Сброс счетчика ошибок 9. Устройство работает следующим образом. Принимаемые знаки посылки ПС из приемника 1 поступают в сумматор 2 по модулю два, где складываются по модулю два со знаками рекуррентной последовательности, вырабатываемыми генератором 3. Одновременно с сигнального выхода приемника I поступают импульсы, свидетельствующие о правильности регистрации двоичных знаков ПС («1 - ненадежная регистрация, «О - надежная регистрация). Блок 7 весовых функций формирует кодовые управляющие сигналы, которые поступают на ВХОДЫ реверсивного счетчика 5 в зависимости от результатов сравнения и регистрации каждого знака ПС. Так, при совпадении сравниваемых знаков вырабатывается суммирующий управляющий сигнал, а при несовпадении - вычитающий. Кроме того, величина этого сдвига реверсивного счетчика 5 определяется и тем, как зарегистрирован данный принятый знак. Результаты сравнения знаков ПС поступают также через управляющий блок 8, на счетчик ошибок 9 и счетчик временных интервалов 10 между пакетами ошибок. Первый несовпавший знак ПС через элемент И 14 запускает счетчик ошибок 9 и сбрасывает счетчик 10 временных интервалов. Последующий несовпавший знак, проходя через элемент И 14, запускает счетчик 10 временных интервалов. Таким образом, счетчик ошибок 9 будет содержать число импульсов, пропорциональное длине пакета ощибок I. Блок сравнения 11 вырабатывает управляющий сигнал, когда интервал Т между пакетами ошибок превысит длину пакета ошибок Е. По этому сигналу значения счетчика ошибок 9 пере.писыва отся в дополнительный сумматор 12, а управляющий блок 8 переводится в исходное состояние. Ноли с сумматора 2 появится сигнал несовпадения до того, как произойдет событие , то счетчик ошибок 9 продолжает счет тактовых импульсов до последующей остановки. Цикловой распределитель 4 опрашивает показания реверсивного счетчика 5 и счетчика ощибок 9 с периодичностью в п знаков (где п - длина ПС) и при суммарной длине пакетов ошибок Е и взвешенной сумме S, не превышаюЦ1ИХ допустимых значений, установленных в пороговых блоках 6 и 13, на элементе И 14 селектируется синхросигнал, фазирующий цикловой распределитель 4. В то же время на несинхронных сдвигах или при поступлении на вход приемника I несовпадающие знаки равномерно распределены по всей длине ПС. При этом длина вычисленных пакетов ошибок будет значительно превышать пороговое значение tgm и, следовательно, ложной синхронизации не произойдет. Действительно, рекуррентные последовательности длины (т - длина регистра сдвига генератора 3) не содержат серии нулей, большей, чем (т-1). Поэтому при корреляционном сложении ПС по модулю два со всеми возможными циклическими перестановками, минимальная длина пакета ошибочных (несовпавших) знаков составляет -nv Даже присутствие канальных пакетов ошибок су.ммарной длины f не может повлиять на выделение ПС, если . С другой стороны, при синхронном сравнении знаков ПС любой пакет ошибок или сумма пакетов ошибок длины водит к правильному выделению синхросигналов. Кроме того, при сильном группировании канальных ошибок вероятность ошибочных знаков внутри пакета ошибок суш,ественно выше, чем для отдельных (независимых) ошибок. С учетом этого обстоятельства во время приема пакета ошибок, т.е. когда работает счетчик ошибок 9, соотношение между весовыми коэффициентами в блоке весовых функций изменяется соответствующим образом. Это позволяет повысить вероятность срабатывания дополнительного порогового блока 13 при приеме ПС и, еледовательно, дополнительно повысить помехоустойчивость синхронизации. Вычисление взвешенной суммы ошибочных знаков в сочетании с определением длины пакетов ошибок в передаваемых ПС позволяет значительно повысить помехоустойчивость цикловой синхронизации в каналах связи с группированием помех. Формула изобретения Устройство для цикловой синхронизации, содержащее приемник, соединенный с сумматором по модулю два, второй вход которого через генератор опорной последовательности соединен с выходомциклового распределителя, второй выход которого через реверсивный счетчик подключен к порогово му блоку, отличающееся тем, что, с целью повышения помсхоустойчквосги синхронизации в каналах связи с группкрови ием помех,, введены блок весовых функций, управляющий блок, счетчик ошибок и счетчик временных интервалов, б,пок сравмсния, дополнительный Оуммдтор по модулю два, допатнительный пороговый блок и элемент И, при этом к входам блока весовых функций подключены сигнальный выход приемника и выходы сумматора ,по модулю два и счетчика ошибок соответствейно, а выход блока весовых функций соединен с другим входом реверсивного счетчика, выход сумматора по модулю два подключен через управляющий блок к двум объединенным входам счетчика ошибок и счетчика временных интервалов, третьи объединенные входы которых подключены к управляющему входу управляющего блока и выходу блока сравнения, два входа которого подключены соответственно к выходу счетчика ошибок и счетчика временных интервалов, .а другой выход блока сравнения соединен с управляющим входом счетчика ошибок и входом дополнительного сумматора по модулю два, выход которого через последовательно соединенные дополнительный пороговый блок, элемент И, второй вход которого соединен с выходом порогового блока, подключен к входу циклового распределителя, а второй выход циклового распределителя соединен с входом «Сброо счетчика ошибок, Источники информации, принятые вовиимание нри экспертизе 1. Авторское свидетельство СССР № 422116, кл. Н 04 L 7/02, 1972.

| название | год | авторы | номер документа |

|---|---|---|---|

| Пороговый декодер сверточного кода | 1989 |

|

SU1667264A1 |

| УСТРОЙСТВО ДЛЯ СИНХРОНИЗАЦИИ ПО ЦИКЛАМ | 2002 |

|

RU2239953C2 |

| Сверточный кодек с алгоритмом порогового декодирования | 1985 |

|

SU1327296A1 |

| Система для передачи и приема дискретной информации | 1979 |

|

SU903850A1 |

| УСТРОЙСТВО КОДОВОЙ ЦИКЛОВОЙ СИНХРОНИЗАЦИИ С ИНТЕГРИРОВАННЫМИ МЯГКИМИ И ЖЕСТКИМИ РЕШЕНИЯМИ | 2011 |

|

RU2450464C1 |

| УСТРОЙСТВО КОДОВОЙ ЦИКЛОВОЙ СИНХРОНИЗАЦИИ | 2008 |

|

RU2383104C2 |

| СПОСОБ КОДОВОЙ ЦИКЛОВОЙ СИНХРОНИЗАЦИИ | 2011 |

|

RU2450436C1 |

| УСТРОЙСТВО ДЛЯ ЦИКЛОВОЙ СИНХРОНИЗАЦИИ | 2005 |

|

RU2284665C1 |

| Цифровой приемник дельта-модулированных сигналов | 1989 |

|

SU1732499A1 |

| Устройство избирательного вызова и передачи кодограмм | 1983 |

|

SU1136326A1 |

Авторы

Даты

1979-01-15—Публикация

1976-07-14—Подача