Изобретение относится к технике связи и может быть использовано для цикловой синхронизации высокоскоростных систематических сверточных кодов при передаче дискретной информации по каналам связи.

Целью изобретения является расширение области применения за счет использования высокоскоростных сверточных кодов и повышения помехоустойчивости устройства.

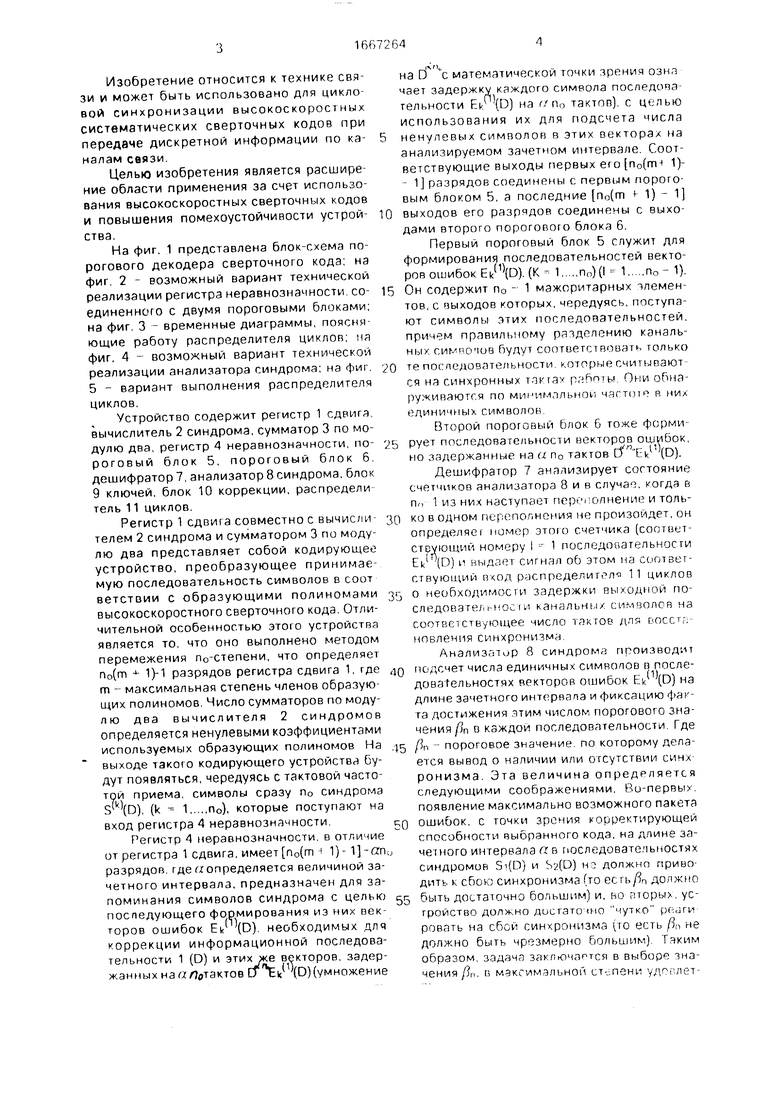

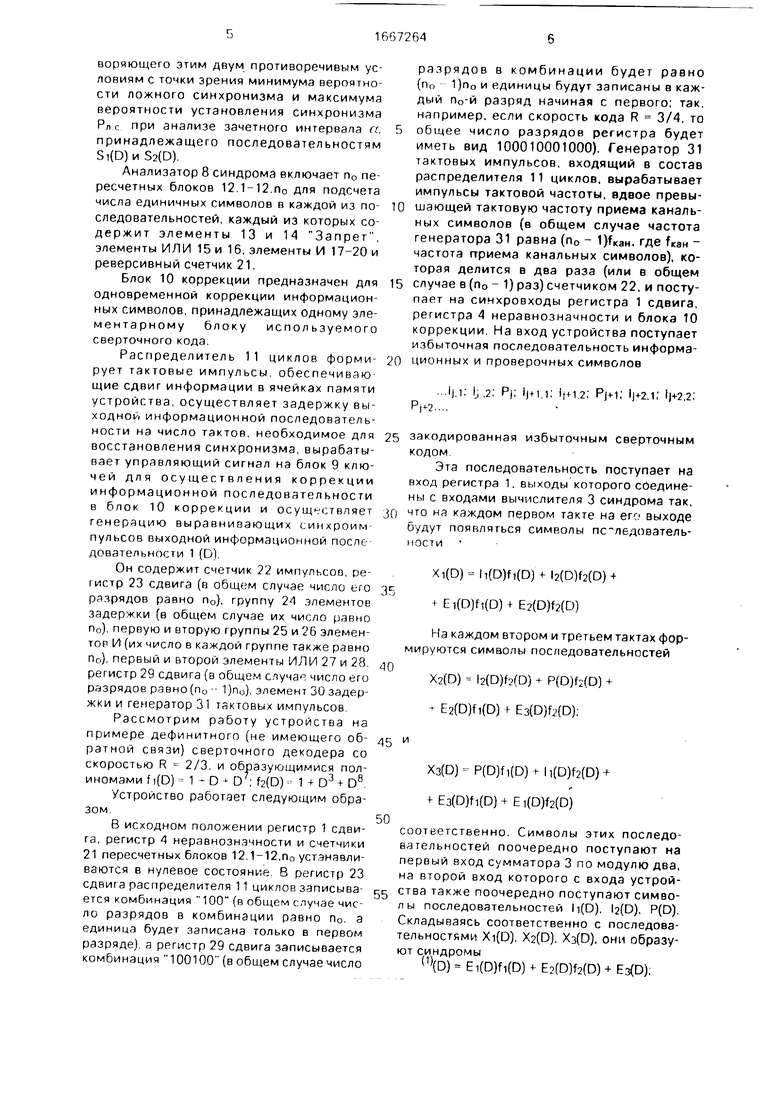

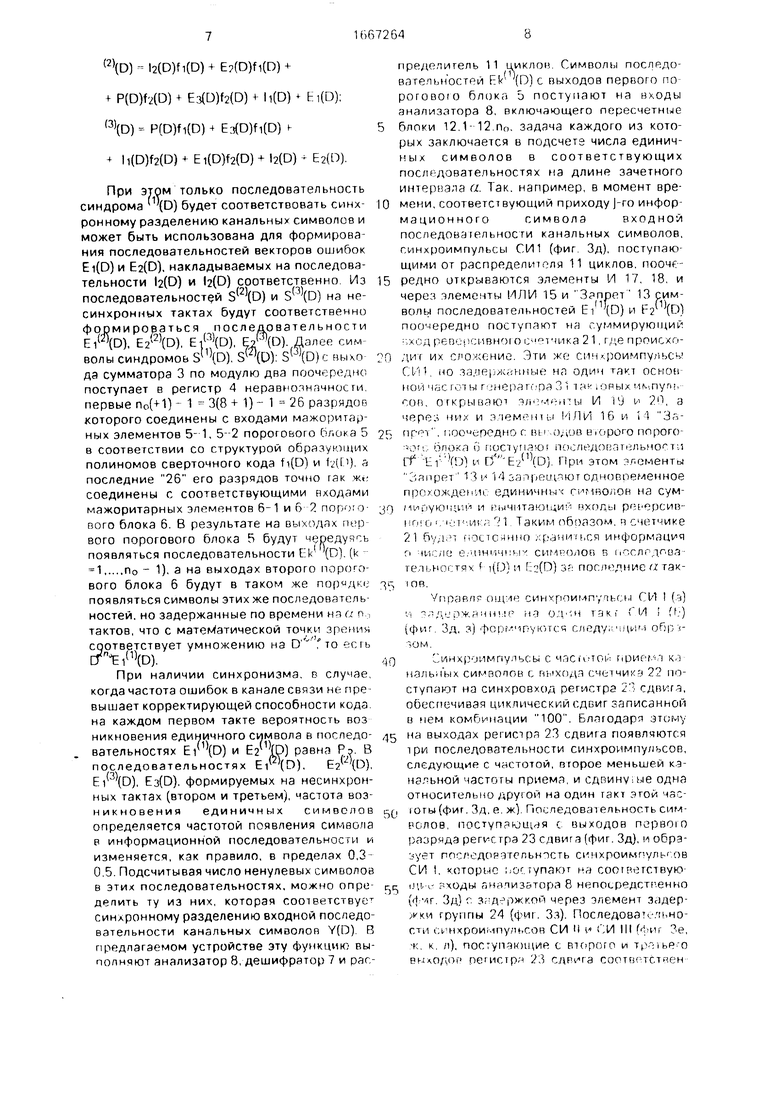

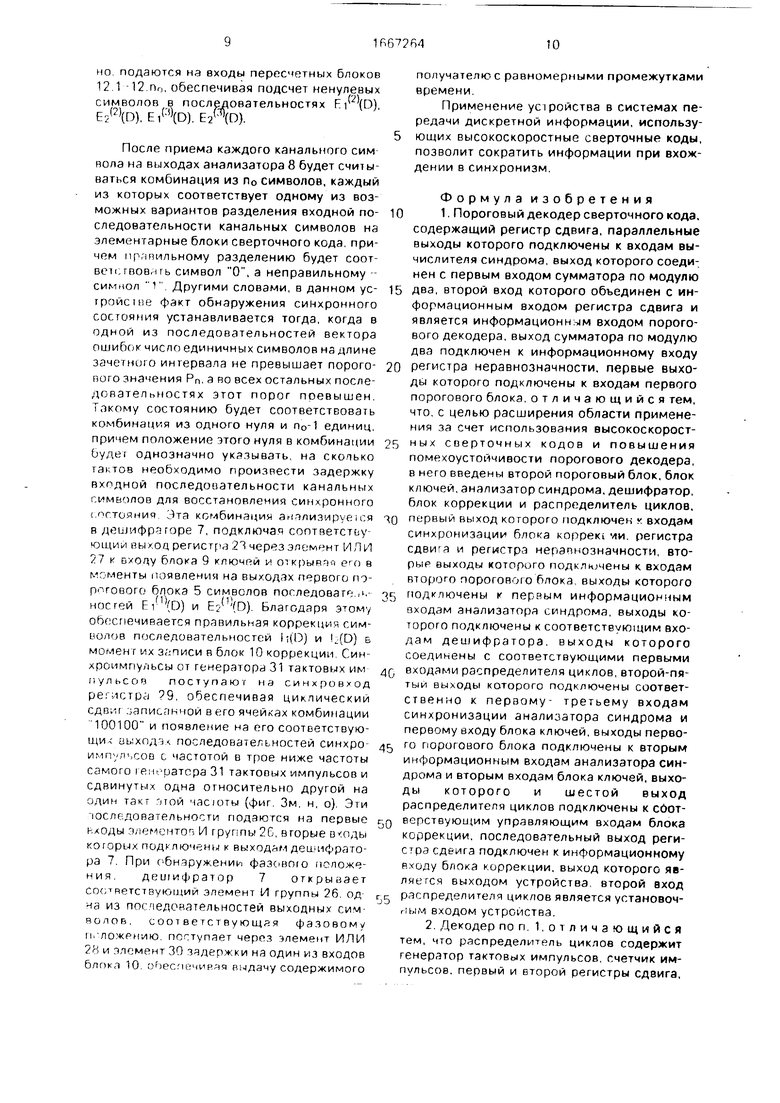

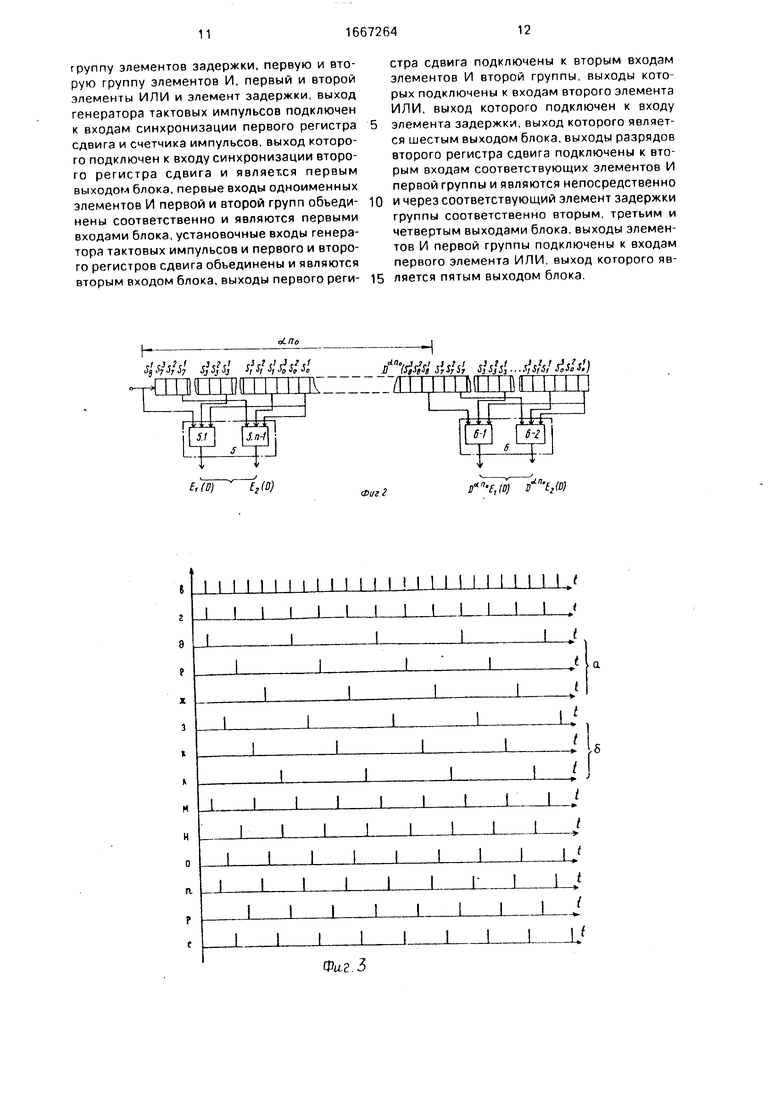

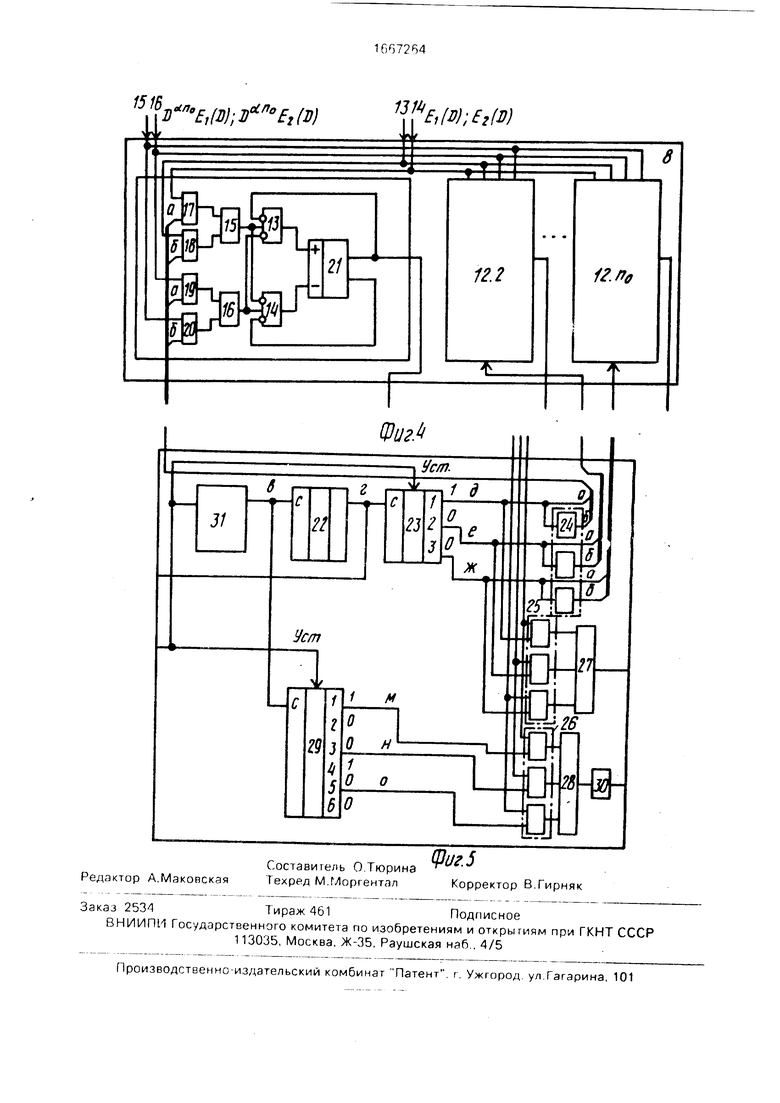

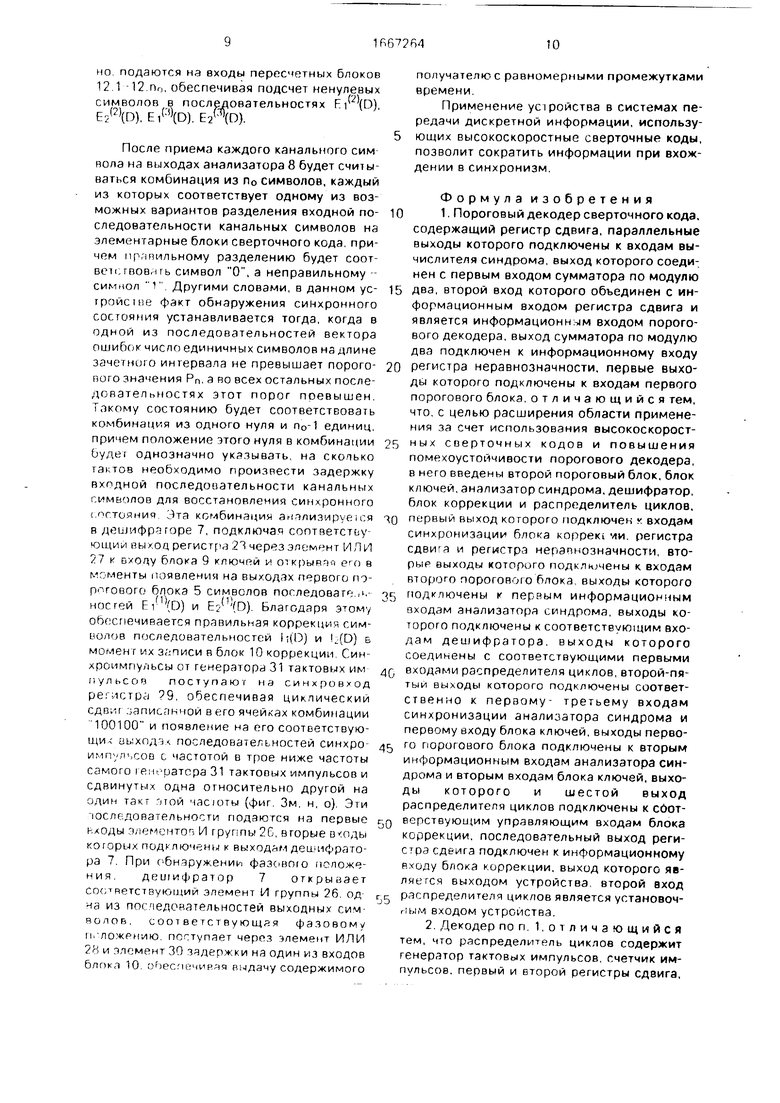

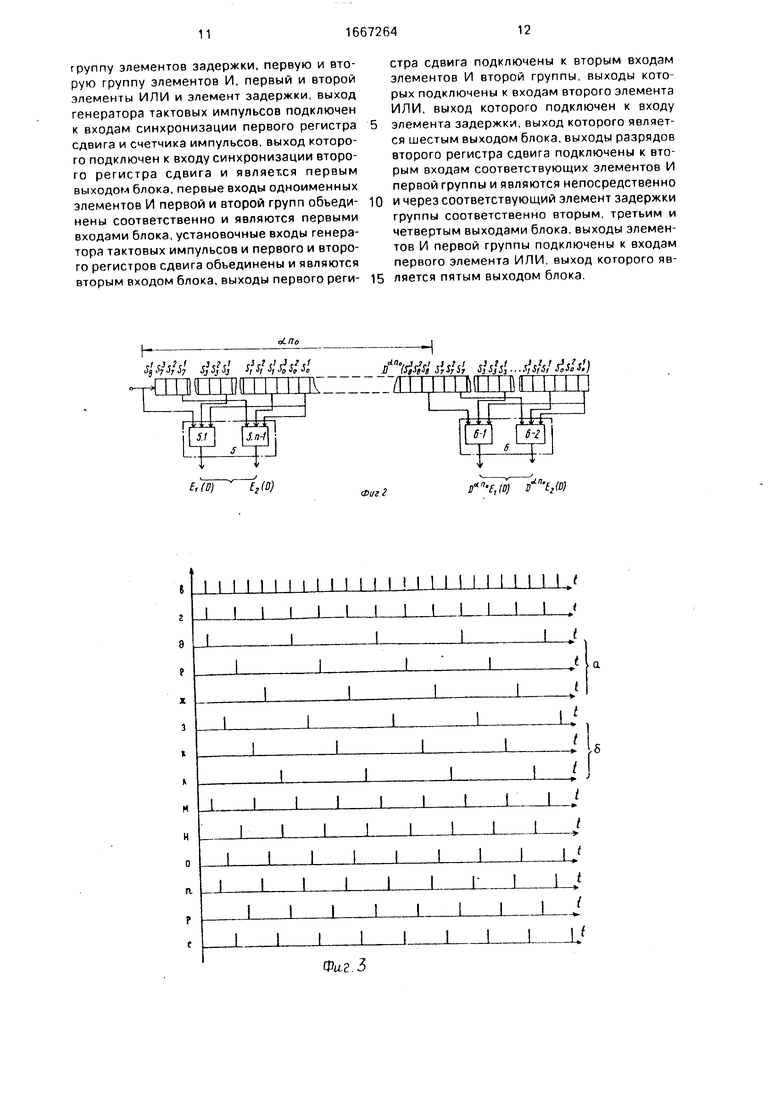

На фиг. 1 представлена блок-схема порогового декодера сверточного кода; на фиг. 2 - возможный вариант технической реализации регистра неравнозначности соединенного с двумя пороговыми блоками; на фиг. 3 - временные диаграммы, поясняющие работу распределителя циклов; ня фиг. 4 - возможный вариант технической реализации анализатора синдрома; на фиг 5 - вариант выполнения распределителя циклов.

Устройство содержит регистр 1 сдвига вычислитель 2 синдрома, сумматор 3 по модулю два, регистр 4 неравнозначности, пороговый блок 5, пороговый блок 6 дешифратор 7, анализатор 8 синдрома, блок 9 ключей, блок 10 коррекции, распредели тель 11 циклов.

Регистр 1 сдвига совместно с вычисли телем 2 синдрома и сумматором 3 по модулю два представляет собой кодирующее устройство, преобразующее принимаемую последовательность символов в соот ветствии с образующими полиномами высокоскоростного сверточного кода. Отличительной особенностью этого устройства является то, что оно выполнено методом перемежения п0-степени, что определяет n0(m 1}-1 разрядов регистра сдвига 1, где m - максимальная степень членов образующих полиномов. Число сумматоров по моду- лю два вычислителя 2 синдромов определяется ненулевыми коэффициентами используемых образующих полиномов На выходе такого кодирующего устройства будут появляться, чередуясь с тактовой частотой приема, символы сразу п0 синдрома

s k (D), (k 1п0), которые поступают на

вход регистра 4 неравнозначности

Регистр 4 неравнозначности, в отличие от регистра 1 сдвига, имеет n0(m i 1)- разрядов где «определяется величиной зачетного интервала, предназначен для запоминания символов синдрома с целью поспедующего формирования из них векторов ошибок Ei (D) необходимых для коррекции информационной последовательности 1 (D) и этих же векторов, задержанных наа/7отактов и tk (D)(умножение

на сГ с математической точки зрения ознгз чает задержку каждого символа последовательности Ei/ (D) на ч п0 тактов) с целью использования их для подсчета числа ненулевых символов в этих векторах на анализируемом зачетном интервале Соответствующие выходы первых его п0(гги 1)- - 1 разрядов соединены с первым пороговым блоком 5, а последние n0(m t- 1) - 1 0 выходов его разрядов соединены с выходами второго порогового блока 6.

Первый пороговый блок 5 служит для формирования последовательностей векторов ошибок Ek(1)(D). (К - 1, ,,п0)(1-1. ,п0-1). 5 Он содержит п0 - 1 мажоритарных элементов, с выходов которых, чередуясь, поступают символы этих последовательностей, причем правильному разделению канальных симчсчов будут соответствовать только 0 те последовательности которые считывают ся на синхронных такта работы Они обнаруживаются по минимальной частоте в нил единичных символов

Второй пороговый блок G тоже форми- Ь РУет последовательности векторов ошибок, но задержанные на а п0 тактов (D).

Дешифратор 7 анализирует состояние счетчиков анализатора Вив случае, когда в по 1 из них наступает ncpt i олнение и толь- 0 ко в одном переполнения не произойдет, он определяв номер этою счетчика (соответствующий номеру I - 1 последовательности Ek1 (D) и выдает сигнал об этом на соответствующий распределителе 11 циклов 13 о необходимости задержки выходной по- следоваге/ hHOv. ги канзльни/ символов на соответствующее число тактов для ооссг:. новлениясинхронизма

Анализатор 8 синдрома производит 0 подсчет числа единичных символов в последовательностях векторов ошибок Ek (D) на длине зачетного интервала и фиксацию факта достижения чтим числом порогового значения/In в кзждои последовательности Где 45 /Зп - пороговое значение по которому делается вывод о наличии или отсутствии сичх ронизма. Эта величина определяется следующими соображениями. Во-первых появление максимально возможного пакета 50 ошибок, с точки зрения корректирующей способности выбранного кода, на длине за- четного интервала а. в последовательностях синдромов Si(D) и Ь ДО) н должно приводить к сбою синхронизма (то есть/ п должно 55 быть достаточно большим) и, во пторых, устройство должно досгатопю чутко рс-йги ровать на сбои синхронизма (ю есть /Зп не должно быть чрезмерно большим) Тчким образом задача заключается в выборе значения/ Р, в максимальной степени уд - летворяющего этим двум противоречивым условиям с точки зрения минимума вероятности ложного синхронизма и максимума вероятности установления синхронизма Рлс при анализе зачетного интервала а, принадлежащего последовательностям Si(D)n S2(D).

Анализатор 8 синдрома включает п0 пересчетных блоков 12.1-12.По для подсчета числа единичных символов в каждой из последовательностей, каждый из которых содержит элементы 13 и 14 Запрет, элементы ИЛИ 15 и 16. элементы И 17-20 и реверсивный счетчик 21.

Блок 10 коррекции предназначен для одновременной коррекции информационных символов, принадлежащих одному элементарному блоку используемого сверточного кода.

Распределитель 11 циклов формирует тактовые импульсы, обеспечивающие сдвиг информации в ячейках памяти устройства, осуществляет задержку выходной информационной последовательности на число тактов, необходимое для восстановления синхронизма, вырабатывает управляющий сигнал на блок 9 ключей для осуществления коррекции информационной после до в а те л ьности в блок 10 коррекции и осуществляет генерацию выравнивающих синхроим пульсов выходной информационной после довательности 1 (D)

Он содержит счетчик 22 импульсов, регистр 23 сдвига (в общем случае число его разрядов равно п0). группу 24 элементов задержки (в общем случае их число равно п0), первую и вторую группы 25 и 26 элемен- ТОР И (их число в каждой группе также равно п0), первый и второй элементы ИЛИ 27 и 28 регистр 29 сдвига (в общем случа число его разрядов равно (п0 - 1)п0), элемент 30 задержки и генератор 31 тактовых импульсов

Рассмотрим работу устройства на примере дефинитного (не имеющего обратной связи) сверточного декодера со скоростью R 2/3. и образующимися полиномами f i(D) - 1 - D - D ; f2(D) -- 1 + D3 + D8

Устройство работает следующим образом

В исходном положении регистр 1 сдвига, регистр 4 неравнозначности и счетчики 21 пересчетных блоков 12.1-12.п0 устанавливаются в нулевое состояние В регистр 23 сдвига распределителя 11 циклов записывается комбинация 100 (в общем случае число разрядов в комбинации равно n0, a единица будет записана только в первом разряде) а регистр 29 сдвига записывается комбинация 100100 (в общем случае число

разрядов в комбинации будет равно (п0 1)п0 и единицы будут записаны в каждый п0-й разряд начиная с первого; так, например, если скорость кода R 3/4, то

5 общее число разрядов регистра будет иметь вид 100010001000). Генератор 31 тактовых импульсов, входящий в состав распределителя 11 циклов, вырабатывает импульсы тактовой частоты, вдвое превы0 шающей тактовую частоту приема канальных символов (в общем случае частота генератора 31 равна (п0 - 1), где - частота приема канальных символов), которая делится в два раза (или в общем

5 случае в (п0 - 1) раз) счетчиком 22, и поступает на сичхровходы регистра 1 сдвига, регистра 4 неравнозначности и блока 10 коррекции. На вход устройства поступает избыточная последовательность информа0 ционных и проверочных символов

. .ij.i: Ь .2: Ру, IJ-H.I: it+12; Рм-i; ij+2.i; lj+2.2;

P,+2 ..,

5 закодированная избыточным сверточным

кодом

Эта последовательность поступает на

вход регистра 1, выходы которого сбединены с входами вычислителя 3 синдрома так, 0 чт° на каждом первом такте на его выходе

будут появляться символы пс ледовательиости

Xi(D) h(D)fi(D) + l2(D)f2(D) 4 + Ei(D)fi(D) + E2(D)f2(D)

На каждом втором и третьем тактах формируются символы последовательностей

X2(D) - l2(D)f2(D) + P(D)f:(D) + - E2(D)fi(D) ь Ез(О)тЛО); и

Хз(0) - P(D)f i(D) f I i(D)f2(D) + f E3(D)fi(D) + E i(D)f2(D)

соответственно. Символы этих последовательностей поочередно поступают на первый вход сумматора 3 по модулю два, на второй вход которого с входа устрой- ства также поочередно поступают симво- лы последовательностей h(D), I2(D), P(D). Складываясь соответственно с последовательностями Xi(D), X2(D). Хз(0), они образуют синдромы

(1)(D) Ei(D)fi(D) + E2(D)f2(D) + Ез(0).

(2)(D) - la(D)f i(D) + E(D)f 1(D) +

+ P(D)f2(D) + E3(D)f2(D) + li(D) ti(D).

(3)(D) P(D)fi(D) Ea(D)fi(D) ь

h(D)f2(D) + Ei(D)f2(D) 12(D) - E2(0)

При этом только последовательность синдрома (D) будет соответствовать синхронному разделению канальных символов и может быть использована для формирования последовательностей векторов ошибок Ei(D) и E2{D), накладываемых на последовательности l2(D) и l2(D) соответственно Из последовательностей s 2 (D) и ) на несинхронных тактах будут соответственно формироваться последовательности Eiffl(D), E2(2(D), E AD), EAD) Далее сим волы синдромов S(D). SW(D) SlJ)(D)t выхп да сумматора 3 по модулю два поочередно поступает в регистр 4 неравнозначности первые По(-И) - 1 - 3(8 + 1) 1 26 разоядоп которого соединены с входами мажоритарных элементов 5-1.5-2 порогового блока 5 в соответствии со структурой образующих полиномов сверточного кода fi(D) и МП) а последние 26 его разрядов точно гак же соединены с соответствующими входами мажоритарных элементов 6-1 и 6 2 пор но вого блока 6 В результате на выходах пер вого порогового блока 5 будут чередуясь появляться последовательности Е И (D) (k

1п0 - 1). а на выходах второго пороги

вого блока 6 будут в таком же породи, появляться символы этихже последователь ностей. но задержанные по времени нл а г тактов, что с математической точки зрение соответствует умножению на D то гль

crw%)).

При наличии синхронизма, в случае когда частота ошибок в канале связи не пре вышает корректирующей способности кода на каждом первом такте вероятность воз никновения единичного символа в последовательностях ) и (Р) равна Р В последовательностях Er (D), E (D), ), Ез(0), формируемых на несинхронных тактах (втором и третьем), частота воз- никновения единичных символов определяется частотой появления симвопа в информационной последовательности и изменяется, как правило, в пределах 0.3- 0 5 Подсчитывая число ненулевых символов в этих последовательностях, можно опре депить ту из них, которая соответствуем синлронному разделению входной последовательности канальных символов Y(D) В предлагаемом устройстве эту функцию выполняют анализатор 8, дешифратор 7 и распределитель 11 циклон Символы ПОСЛРДО взгетьн остри Fk (Die выходов первого по роговою блока 5 поступают на входы анализатора 8, включающего пересчетные

блоки 12 1 12 По, задача каждого из которых заключается в подсчете числа единичных символов в соответствующих noc/if довательностях на длине зачетного интервала и Так. например, в момент вре0 мени, соответствующий приходу J-ro инфор мационногосимволавходной

последова ельносги канальных символов, синхроимпульсы СИ1 (фиг Зд), поступаю щими от распределителя 11 циклов. noo4f5 редно открываются элементы И 17, 18 и через элементы ИЛИ 15 и Запрет 13 символы последовательностей Ei (D) и Рг (D) поочередно поступают на гуммирующий м д peri, .дивного 21 гдепроисхо0 лиг их сложение Эти же синхроимпульсу С I ll но ( чп один такт основ ной 4oL TI ты г jнеpriti n i 1 , 1Рых ил. пути открываю1 И iy и РП, а мере.-, ни/ и i lHul 16 и 1 1 Зл5 nr-( V 1,ООисООДНО С ВЫ Ог1пв BiOpurO ПОрОТО

ог локл и noci na4jt по педлппнльно т J rf L 1 Ъ и b/(1)(D) При этом -г.ементы Запрет 14 за троирют однооорменное прп ождем ,н единичны символов на сумO )уюь;1 и и рычнтаю чИ холь р Н врсив- (Г| () г HI , ГП Таким пбоазом п счетчике 21 бч,1 т inLTCi4HHo , .ься информация г in jifj с ПН1|Ч1 н сипм}лог ц Г|,глгтг.вя теп not та , f (D) и Г (П) з последние « такюв

/правлю ощ IP синхрпимпутк и СИ I (} i /-л iiv н и н SP г)-т о 1 Н т з к 1 Г И (Ч ) фиг Зд, з) фо (я следу, ми,и oF)|; i- ом

Q ИНХрОИМПу ТЬСЬ С ЧЭСи- TOl TiOHOt l К1

нальпых сиг вопов с пнходз счотчи / j 22 поступают на синхровход регистра 2 сдвига, обеспечивая циклический сдвиг записанной в нем комбинации 100 Благодаря этому

5 на выходах peincipa 23 сдвига появляются три последовательности синхроимпульсов, следующие с частотой, второе меньшей кэ- частоты приема и сдвину ые одна относительно Apyi ой на один такт згой чз

{j юты(фиг Зд. е ж) Поипедова)ельность сим поступающая с выходов первою разряда грэ 23 сдвига (фиг Зд), обра- о-/ет ПП ЛСДОРэгельнпсть симхроимпуль ов СИ I, «шорыс : окупают иг) соогрегслвую

c, i ,i s ходы «Нгпизвторл 8 непосредстгенно (f|-/ir Зд) г з д- ржкои через элемент Зс)дер- ки группы 24 (фиг Зз) Последова стьчо- СЛ11 i.t. нхрои1-1пул,гоч СИ U и (,И II и, Зе, к к л), поолупяющие с втс рогп и тр чье о вмд,одо| пегислр У сдрига соотч

но подаются на входы пересчетных блоков 121-12 п0, обеспечивая подсчет ненулевых символов в последовательностях Ег (D), E2(2)(D), Ei(3)(D). E2f%5).

После приема каждого канального сим вола на выходах анализатора 8 будет считываться комбинация из п0 символов, каждый из которых соответствует одному из возможных вариантов разделения входной последовательности канальных символов на элементарные блоки сверточного кода, причем правильному разделению будет соот- век-гвовнгь символ О, а неправильному - симнол V1 Другими словами, в данном устройств факт обнаружения синхронного состояния устанавливается тогда, когда в одной из последовательностей вектора ошибок число единичных символов на длине зачетною интервала не превышает порогового значения Рп, а во всех остальных после- допательностях этот порог поевышен. Такому состоянию будет соответствовать комбинация из одного нуля и по-1 единиц, причем положение этого нуля в комбинации иуде однозначно указывать, на сколько тактов необходимо произвести задержку входной последовательности канальных символов для восстановления синхронного ( огтояния Эта комбинация аголизируен я в дешифраторе 7, подключая соответствующий выход регистра 23 через элемент ИЛИ

27к входу блока 9 ключей и открывая его в моменты появления на выходах первого порогового блока 5 символов последовать .- нос гей Ei (D) и Е; (D). Благодаря этому обеспечивается правильная коррекция символов последовательностей h|D) и L(D) ь момен г их записи в блок 10 коррекции Синхроимпульсы от генератора 31 тактовых им пульсов поступают на синхровход регисгрй 9, обеспечивая циклический сдвиг написанной в его ячейках комбинации 100100 и появление на его соответствующие оыходз последовательностей синхроимпульсов с частотой в трое ниже частоты самого i ен -ратсра 31 тактовых импульсов и сдвинутых одна относительно другой на один такт лой часюты (фиг. Зм, н, о). Эти -юслр-.довательности подаются на первые ьходы олементог) И группы 2С, вторые входы которых подключены к выходам деи ифрато- ра 7. При обнаружении фазовою положения, дешифратор 7 открывает соответствующий элемент И группы 26 од на из последовательностей выходных символов, соответствующий фазовому положению поступает через элемент ИЛИ

28и элемент 30 задержки на один из входов блокл 10 опеспцчирчя выдачу содержимого

получателю с равномерными промежутками времени.

Применение устройства в системах передачи дискретной информации, использу- 5 ющих высокоскоростные сверточные коды, позволит сократить информации при вхождении в синхронизм.

Формула изобретения

01. Пороговый декодер сверточного кода.

содержащий регистр сдвига, параллельные выходы которого подключены к входам вычислителя синдрома, выход которого соединен с первым входом сумматора по модулю

5 два, второй вход которого объединен с информационным входом регистра сдвига и является информационным входом порогового декодера, выход сумматора по модулю два подключен к информационному входу

0 регистра неравнозначности, первые выходы которого подключены к входам первого порогового блока, отличающийся тем, что, с целью расширения области применения за счет использования высокоскорост5 ных сверточных кодов и повышения помехоустойчивости порогового декодера, в него введены второй пороговый блок, блок ключей, анализатор синдрома, дешифратор, блок коррекции и распределитель циклов,

0 первый выход которого подключен к входам синхронизации блока коррекс ми. регистра сдвига и регистра неравнозначности, вторые выходы которого подключены к входам второго порогового блока, выходы которого

5 подключены к первым информационным входам анализатора синдрома, выходы которого подключены к соответствующим входам дешифратора, выходы которого соединены с соответствующими первыми

Q входами распределителя циклов, второй-пя- тыи выходы которого подключены соответственно к первому- третьему входам синхронизации анализатора синдрома и первому входу блока ключей, выходы перво5 го порогового блока подключены к вторым информационным входам анализатора синдрома и вторым входам блока ключей, выходы которого и шестой выход распределителя циклов подключены к сбот0 верствующим управляющим входам блока коррекции, последовательный выход регистра сдвига подключен к информационному входу блока коррекции, выход которого является выходом устройства, второй вход

5 распределителя циклов является установочным входом устройства.

2. Декодер по п. 1,отличающийся тем, что распределитель циклов содержит генератор тактовых импульсов, счетчик импульсов, первый и второй регистры сдвига,

группу элементов задержки, первую и вторую группу элементов И, первый и второй элементы ИЛИ и элемент задержки, выход генератора тактовых импульсов подключен к входам синхронизации первого регистра сдвига и счетчика импульсов, выход которого подключен к входу синхронизации второго регистра сдвига и является первым выходом блока, первые входы одноименных элементов И первой и второй групп объединены соответственно и являются первыми входами блока, установочные входы генератора тактовых импульсов и первого и второго регистров сдвига объединены и являются вторым входом блока, выходы первого реги

5

стра сдвига подключены к вторым входам элементов И второй группы, выходы которых подключены к входам второго элемента ИЛИ, выход которого подключен к входу элемента задержки, выход которого является шестым выходом блока, выходы разрядов второго регистра сдвига подключены к вторым входам соответствующих элементов И первой группы и являются непосредственно и через соответствующий элемент задержки группы соответственно вторым, третьим и четвертым выходами блока, выходы элементов И первой группы подключены к входам первого элемента ИЛИ, выход которого является пятым выходом блока.

| название | год | авторы | номер документа |

|---|---|---|---|

| Пороговый декодер сверточного кода | 1981 |

|

SU1046958A1 |

| Пороговый декодер сверточного кода | 1991 |

|

SU1781825A1 |

| Пороговый декодер сверточного кода | 1991 |

|

SU1837385A1 |

| Кодер несистематического сверточного кода | 1990 |

|

SU1695516A1 |

| Пороговый декодер сверточного кода | 1985 |

|

SU1252944A1 |

| Декодер сверточного кода | 1986 |

|

SU1388998A1 |

| Кодек несистематического сверточного кода | 1990 |

|

SU1714812A1 |

| Пороговый декодер сверточного кода | 1982 |

|

SU1078654A1 |

| ДЕКОДЕР СВЕРТОЧНОГО КОДА | 1992 |

|

RU2085035C1 |

| Декодер сверточного кода (его варианты) | 1985 |

|

SU1320875A1 |

Изобретение относится к технике связи и может быть использовано для цикловой синхронизации высокоскоростных сверточных кодов при передаче информации по дискретным каналам связи. Целью изобретения является расширение области применения за счет использования высокоскоростных сверточных кодов и повышение помехоустойчивости устройства. Применение предлагаемого устройства в системах передачи дискретной информации, использующих высокоскоростные систематические сверточные коды, позволит существенно сократить потери информации при вхождении в синхронизм. Пороговый декодер сверточного кода содержит регистр 1 сдвига, вычислитель 2 синдрома, сумматор 3 по модулю два, регистр 4 неравнозначности, пороговые блоки 5 и 6, дешифратор 7, анализатор 8 синдрома, блок 9 ключей, блок 10 коррекции, распределитель 11 циклов. 1 з.п. ф-лы, 5 ил.

s tMs} fofo №№ МJ ttjMslsM sjsjs ...fa s/Ms)

I I.I M.IV7II I.I II

E,(D) lj(D)

I I I I 1 I I 1 I I I M I 1 I I I I I I I 1 I I I,

Фи.г.3

Фиг 2.

е,1Щ

JL

151bV EM dnoEi V)

,(3);Јг(3)

| Устройство для декодирования сверточного кода | 1984 |

|

SU1213491A1 |

| Пороговый декодер сверточного кода | 1981 |

|

SU1046958A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

Авторы

Даты

1991-07-30—Публикация

1989-09-21—Подача